## CBCS Schame

|                                                                                    | -//      |                                                                                                                                                     | (9)               |

|------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| USN                                                                                | =        |                                                                                                                                                     | 15EE35            |

| Third Semester B.E. Degree Examination, Dec.2017/Jan.2018                          |          |                                                                                                                                                     |                   |

| Digital System Design                                                              |          |                                                                                                                                                     |                   |

| 95                                                                                 |          |                                                                                                                                                     |                   |

| Time: 3 hrs. Max. Marks: 80                                                        |          |                                                                                                                                                     |                   |

| Note: Answer any FIVE full questions, choosing one full question from each module. |          |                                                                                                                                                     |                   |

|                                                                                    |          | Module-1                                                                                                                                            | 0434 1.)          |

| 1                                                                                  | a.<br>b. | With basic block diagram, explain the combinational logic circuit.  Reduce the following function using K-map technique and implement using basic g | 04 Marks)<br>ates |

|                                                                                    | U.       | i) $f(P, Q, R, S) = \sum_{n=0}^{\infty} m(0, 1, 4, 8, 9, 10) + d(2, 11)$                                                                            |                   |

|                                                                                    |          | ii) $f(A, B, C, D) = \pi M (0, 2, 4, 10, 11, 14, 15)$                                                                                               | 12 Marks)         |

|                                                                                    |          |                                                                                                                                                     |                   |

|                                                                                    |          | OR CO                                                                                                                                               |                   |

| 2                                                                                  | a.       | Simplify using the Quine-Mcclusky minimization technique.                                                                                           |                   |

|                                                                                    | 1.       | 1 (u, o, o, u) \( \sum_{\text{in}} \( \text{(o, =, o, 1 = \( \sum_{\text{in}} \) \)                                                                 | 08 Marks)         |

|                                                                                    | b.       | Simplify the given function using MEV technique.<br>$f(a, b, c, d) = \sum (2, 3, 4, 5, 13, 15) + \sum (4, 8, 9, 10, 11).$                           | 08 Marks)         |

|                                                                                    |          |                                                                                                                                                     |                   |

|                                                                                    |          |                                                                                                                                                     |                   |

| 2                                                                                  |          | With the aid of general structure, clearly distinguish between a decoder and encoder                                                                | r.                |

| 3                                                                                  | a.       |                                                                                                                                                     | (05 Marks)        |

|                                                                                    | b.       | Implement following multiple output function using one 74LS138 and external gate                                                                    | es.               |

|                                                                                    |          |                                                                                                                                                     | (06 Marks)        |

|                                                                                    | c.       | Draw the interfacing diagram of ten keypad interface to a digital system using d                                                                    | ecimal to         |

|                                                                                    |          | BCD encoder (IC 74LS147: Decimal to BCD priority encoder).                                                                                          | (05 Marks)        |

|                                                                                    |          |                                                                                                                                                     |                   |

|                                                                                    |          | OR S                                                                                                                                                |                   |

| 4                                                                                  | a.       | Design a full adder by constructing the truth table and simplify the output equations                                                               | S.                |

|                                                                                    | -        |                                                                                                                                                     | (06 Marks)        |

|                                                                                    | b.       | Write a truth table for two-bit magnitude comparator. Write the Karnaugh map output of two-bit magnitude comparator and the resulting equation.     | (10 Marks)        |

|                                                                                    |          |                                                                                                                                                     |                   |

|                                                                                    |          |                                                                                                                                                     | 3)                |

| _                                                                                  |          | What is the difference between a flip-flop and a latch? With logic diagram and tr                                                                   | nith table        |

| 5                                                                                  | a.       | explain the operation of gated SR latch.                                                                                                            | (08 Marks)        |

|                                                                                    | b        | CM-star along IV Elin flow along with its circuit diagram                                                                                           | (08 Marks)        |

|                                                                                    |          |                                                                                                                                                     |                   |

| (                                                                                  | 0        | OR  Explain the working principle of four bit binary ripple counter, with the help of                                                               | of a logic        |

| 6                                                                                  | a.       | diagram, timing diagram and counting sequence.                                                                                                      | (10 Marks)        |

|                                                                                    | b.       | With logic diagram and counting sequence explain Mod – 4 ring counters.                                                                             | (06 Marks)        |

Module-4

Distinguish between Moore and Mealy model with necessary block diagrams. (08 Marks)

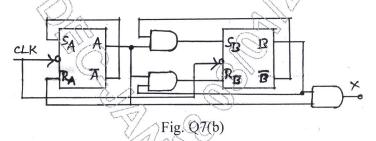

Give output function transition table and state diagram by analyzing the sequential circuit (08 Marks) shown in Fig. Q7(b).

OR

- Write the basic recommended steps for the design of a clocked synchronous sequential 8 (06 Marks) circuit.

- Design a synchronous counter using J-K flip flops to count the sequence 0, 1, 2, 4, 5, 6, 0, 1, (10 Marks) 2. Use state diagram and state table.

Module-5

- Explain brief history of HDL and structure of HDL module, (06 Marks) List the classification of VHDL data types. Compare the VHDL data types and Verilog data

- (10 Marks) types.

OR

Explain signal declaration and signal assignment statements with relevant example. 10

Write a data flow description VHDL for a system that has three 1 bit inputs a (1), a(2) and a(3) one 1-bit output b. The least significant bit is a(1); and b is 1, only when (a(1) a(2) a(3)) = 1, 3, 6 or 7 (all in decimal) otherwise b is 0. Derive a minimized Boolean function of (10 Marks)

the system and write the data flow description.