USN

Time: 3 hrs.

17EE35

(08 Marks)

## Third Semester B.E. Degree Examination, June/July 2019 **Digital System Design**

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

- What is a K-map? Which is the code used to number K-map and why? Write a neat 1 (06 Marks) numbered 4-variable K-map.

- Using K-map, evaluate the minimal POS expression of,  $f(a, b, c, d) = \pi M(0, 2, 4, 6, 8) \cdot \pi D(1, 9, 12, 15)$

- Evaluate the minimal SOP expression using VEM with 'Z' as MEV.  $f(w,x,y,z) = \sum m(0,3,5,7,8,9,10,12,13) + \sum d(1,6,11,14)$ (06 Marks)

- (04 Marks) What is don't care condition? What are its advantages? 2

- Evaluate the canonical SOP expression and hence determine the minimal expression using (08 Marks) K-map  $F = A\overline{B}\overline{D} + \overline{A}B + \overline{A}C + CD$ .

- Minimize the following SOP expression using Quine McCluskey method:  $f(w, x, y, z) = \sum m(3, 7, 8, 10, 11, 12, 14, 15) + \sum d(2, 6)$ (08 Marks)

Module-2

- With a neat diagram, explain the operation of a carry look-ahead adder circuit. (10 Marks)

- Implement the following Boolean function using a 4:1 MUX with a and b as select inputs. b. (06 Marks)  $f(a, b, c, d) = \sum m(4, 5, 7, 8, 10, 12, 15)$ (04 Marks)

- Implement a 2 to 4 decoder using 1 to 2 decoders.

- Design a full adder using 4:1 MUX. 4 a.

- Implement a 1-bit comparator using a suitable decoder.

(06 Marks) (06 Marks)

With a logic diagram, explain the operation of a decimal to BCD priority encoder. (08 Marks)

OR

Module-3

- a. Explain the operation of an SR latch with a circuit diagram and characteristic table. Justify 5 its application as switch debouncer with a relevant circuit and waveforms. (08 Marks)

- Design a 4-bit shift register using DFFs. Design a twisted ring counter using a 4-bit shift (06 Marks) register.

- Design a mod-11 up ripple counter using TFF.

(06 Marks)

- What is the problem in SRFF? How is it eliminated in JKFF? Explain with a neat diagram. 6

- With a neat logic diagram, explain the different modes of operation of universal shift b. register.

- Design a synchronous counter using JKFF with counting sequence 0, 2, 6, 1, 3, 7, 0....

## Module-4

- 7 a. List out the merits and demerits of synchronous sequential circuit asynchronous sequential circuits. (04 Marks)

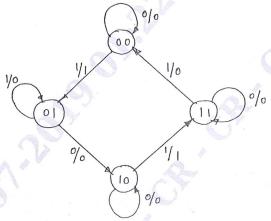

- b. Design a clocked synchronous sequential circuit that operates according to the state diagram shown in Fig.Q7(b). Use DFF in the circuit.

Fig.Q7(b)

(10 Marks)

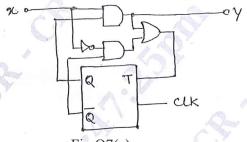

- c. Analyze the following sequential circuit and obtain: [Fig.Q7(c)]

- i) FF input and output equations

ii) Transition table

iii) State table

iv) State diagram

Fig.Q7(c)

(06 Marks)

## OR

- 8 a. Compare and contrast Mealy and Moore synchronous sequential networks with neat block diagrams. (04 Marks)

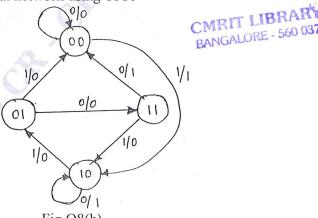

- b. A sequential network has one input and one output. The state diagram is as shown in Fig.Q8(b). Design the sequential network using TFF.

Fig.Q8(b)

(10 Marks)

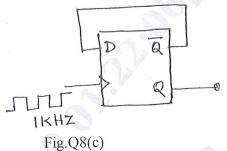

c. An edge triggered DFF is connected as shown in Fig.Q8(c). Assuming Q = 0 initially, sketch the output waveform and determine the frequency of the output signal.

(06 Marks)

Module-5

9 a. Explain entity and architecture with reference to VHDL code of full adder circuit. (08 Marks)

b. Write VHDL code to implement 2:1 MUX.

(06 Marks)

c. List out all operators in VHDL with examples.

(06 Marks)

CMRIT LIBRARY

10 a. Explain various data types supported in VHDL with examples.

(08 Marks)

b. Implement a 1-bit comparator either using VHDL code or verilog.

(04 Marks)

c. Implement a JKFF with active low asynchronous inputs pr and clr along with clock input using verilog/VHDL. (08 Marks)

\* \* \* \* \*