## CBCS SCHEME

15EC655

# Sixth Semester B.E. Degree Examination, June/July 2019 Microelectronics

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

- a. Derive the expression of drain current of a MOS device for triode and saturation region.

- b. Consider a CMOS process for which  $L_{min}=0.4\mu m,\ t_{ox}=8nm,\ \mu_n=450cm^2/v.s$  and  $v_t=0.7V$

- i) Find  $C_{ox}$  and  $k_n^1$

- ii) For an NMOS transistor  $\frac{W}{L} = \frac{8 \mu m}{0.8 \mu m}$ . Calculate the values of  $V_{GS}$  and  $V_{DSmin}$  needed to operate a transistor in saturation region with a DC current  $I_D = 100 \mu A$ .

- iii) For the derive in (ii), find the value of  $V_{GS}$  required to cause the device to operate as  $1000\Omega$  resistor for a very small  $V_{DS}$ . (08 Marks)

OR

- 2 a. With the neat diagram obtain the expression for finite O/P resistance in saturation region.

(07 Marks)

- b. Define the following parameter with respect to MOSFET:

i) Threshold voltage ii) Body Effect.

(05 Marks)

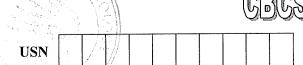

c. For the circuit shown in Fig.Q.2(c), find the values of R and  $V_D$  to obtain a current  $I_D$  of  $80\mu A$ . Let the NMOS transistor have  $V_t = 0.6V$ ,  $\mu_n C_{ox} = 200\mu A/V^2$ ,  $L = 0.8\mu m$  and  $W = 4\mu m$ . Assume  $\lambda = 0$ .

Module-2

- 3 a. Draw the circuit diagram of source follower amplifier. Draw its small signal equivalent circuit with r<sub>o</sub>. Obtain the expression for R<sub>in</sub>, R<sub>out</sub>, A<sub>v</sub>, A<sub>v</sub> and Gv. (10 Marks)

- b. List the various techniques used for biasing in MOS amplifier circuits and explain any two in detail.

#### OR

- 4 a. Draw the development of T-Equivalent circuit model for the MOSFET. (05 Marks)

- b. Explain the high frequency model of MOSEET with a neat diagram and internal capacitances. (06 Marks)

- c. Derive the expression for transconductance  $g_m$  and voltage gain  $A_v$  for a common source amplifier with small input signal. (05 Marks)

### Module-3

- 5 a. Determine the G<sub>v</sub>, A<sub>v</sub>, R<sub>out</sub>, R<sub>in</sub>, A<sub>vo</sub> for a common source MOS amplifier. (08 Marks)

- b. Derive the expression for determining 3-dB frequency (W<sub>H</sub>) of an amplifier. (08 Marks)

#### OR

- 6 a. Explain the operation of a MOSFET current steering circuits with necessary expressions.

(08 Mark

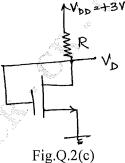

- b. Fig.Q.6(b) shows an ideal voltage amplifier having a gain of -100V/V with an impedance Z is

- i) A  $1M\Omega$  resistance

- ii) A 1pF capacitance. In each case, use the equivalent circuit to determine  $V_0/V_{sig}$ .

(08 Marks)

Fig.Q.6(b)

## Module-4

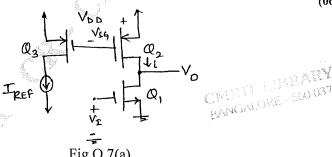

7 a. Consider a CMOS CS amplifier in Fig.Q.7(a) for the case  $V_{DD}=3V$ ,  $V_{tn}=\left|V_{tp}\right|=0.6V$ ,  $\mu_n C_{ox}=200\mu A/V^2$ ,  $\mu_p C_{ox}=65~\mu A/V^2$  for all transistors  $L=0.4\mu m$ ,  $W=4\mu m$ . Also  $V_{An}=20V$ ,  $\left|V_{AP}\right|=10V$ ,  $I_{REF}=100\mu A$ . Find  $g_{m1}$ ,  $r_{o1}$ ,  $r_{o2}$  and small signal voltage gain.

(06 Marks)

b. For a common gate amplifier with active load determine the expression for  $R_i$ ,  $A_{vo}$ ,  $A_v$ ,  $G_{vo}$ ,  $G_v$ ,  $R_o$ . (10 Marks)

OR

- 8 a. Explain the following: i) Double cascode ii) Folded cascode. (08 Marks)

- Explain the high frequency response of MOS cascode amplifier with necessary diagram and expressions.

Module-5

- 9 a. Explain the operation of MOS differential pair with a differential input voltage. (08 Marks)

- b. Prove that  $A_{CM} = \frac{-r_{04}}{2R_{ss}} \times \frac{1}{1 + g_{m3}r_{o3}}$  for the active loaded MOS differential amplifier.

(08 Marks)

OR

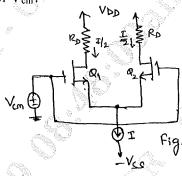

10 a. For the nMOS differential pair with a common mode voltage  $V_{CM}$  applied as shown in Fig.Q.10(a). Let  $V_{DD} = V_{SS} = 2.5 V \ K_n^1 \frac{W}{L} = 3 mA/v^2$ ,  $V_{tn} = 0.7 V$ , I = 0.2 mA,  $R_D = 5 K \Omega$ .

Neglect channel length modulation

- i) Find V<sub>OV</sub> and V<sub>GS</sub> for each transistor

- ii) For  $V_{CM} = 0$ , Find Vs,  $i_{D1}$ ,  $i_{D2}$ ,  $V_{D1}$  and  $V_{D2}$

- iii) What is highest value of  $V_{cm}$  for which  $Q_1$  and  $Q_2$  remain in saturation, if current source I requires a minimum voltage of 0.3V to operate properly. What is the lowest value for  $V_s$  and hence for  $V_{cm}$ ?

OMRIT LIBRAKY RANGALORE - 560 037

Fig.Q.10(a)

(08 Marks)

b. With neat circuit diagram, explain the operation of two stage CMOS Op-amp configuration.

(08 Marks)