## Scheme Of Evaluation Internal Assessment Test 1 – Sept.2019

| Sub:  |            | Analog and Digital Electronics |        |               |    |      | Code: | 18CS33  |     |

|-------|------------|--------------------------------|--------|---------------|----|------|-------|---------|-----|

| Date: | 09/09/2019 | Duration:                      | 90mins | Max<br>Marks: | 50 | Sem: | Ш     | Branch: | ISE |

Note: Answer Any Five Questions

| Que | Question Description #                             |                                                                                           | Marks Distribution |       | Max<br>Marks |

|-----|----------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------|-------|--------------|

|     | a)                                                 | Find the minimum SOP and the minimum POS for<br>each function:                            |                    |       |              |

|     |                                                    | $F(a, b, c, d) = \Pi M (0, 1, 6, 8, 11, 12)$                                              | 2.5M x             |       |              |

|     |                                                    | <ul> <li>Using K-Map for SOP form, calculate minimum SOP</li> </ul>                       | 2                  | 5M    |              |

| 1   | Using K-Map for POS form, calculate minimum<br>POS |                                                                                           |                    | 10 M  |              |

|     | b)                                                 | F(a, b, c, d) = $\Sigma$ m (1, 3, 4, 11) + $\Sigma$ d (2, 7, 8, 12, 14, 15)               |                    |       |              |

|     |                                                    | <ul> <li>Using K-Map for SOP form, calculate minimum<br/>SOP</li> </ul>                   | 2.5M x<br>2        | 5M    |              |

|     |                                                    | <ul> <li>Using K-Map for POS form, calculate minimum<br/>POS</li> </ul>                   |                    |       |              |

|     |                                                    | Find a minimum SOP solution using Quine McCluskey method                                  |                    |       |              |

|     |                                                    | $F(a, b, c, d) = \Sigma m (2, 3, 4, 7, 9, 11, 12, 13, 14) + \Sigma d$                     | 4M                 |       |              |

|     | 2                                                  | (1, 10, 15)                                                                               | 2M                 | 10M   | 10 M         |

|     | -                                                  | <ul> <li>Grouping minterms based on index and<br/>Identifying prime implicants</li> </ul> | 2M                 | 101/1 | 10.11        |

|     |                                                    | Preparing Prime Implicant chart                                                           | 2M                 |       |              |

|     |                                                    | <ul> <li>Identifying Essential PI</li> <li>Obtaining a minimum solution</li> </ul>        |                    |       |              |

|     |                                                    | Find all minimum SOP solutions for the function using                                     | 4M                 |       |              |

|     | 3                                                  | Petrick's method                                                                          | 2M                 | 10M   | 10 M         |

|     |                                                    | F(a, b, c, d) = Σ m (0, 3, 4, 5, 7, 9, 11, 13)  • Grouping minterms based on index and    | 2M                 |       |              |

|   |    | Identifying PI and preparing PI chart  Eliminating Essential PI and its corresponding minterms and obtaining logic function P in terms of rows P1, P2, etc in PI chart  Solving for P using Boolean theorems  Identifying all possible minimum solutions for given function from solution of P.                                                                                                             | 2M       |    |      |

|---|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----|------|

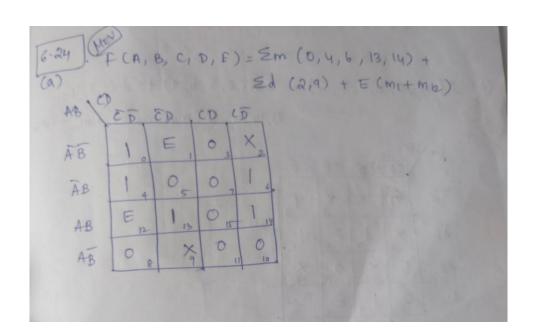

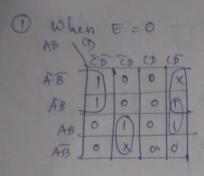

|   | a) | Using the method of map-entered variables, use 4-variable maps to find a minimum SOP expression for:<br>$F(A, B, C, D, E) = \Sigma m (0, 4, 6, 13, 14) + \Sigma d (2, 9) + E(m_1 + m_{12})$                                                                                                                                                                                                                 | 2M       |    |      |

|   |    | <ul> <li>K-Map for given function</li> <li>K-Map for E=0</li> <li>Obtain MS0</li> <li>K-Map for E=1</li> <li>Obtain MS1</li> <li>Obtain final minimum solution</li> </ul>                                                                                                                                                                                                                                   | 2M<br>1M | 5M |      |

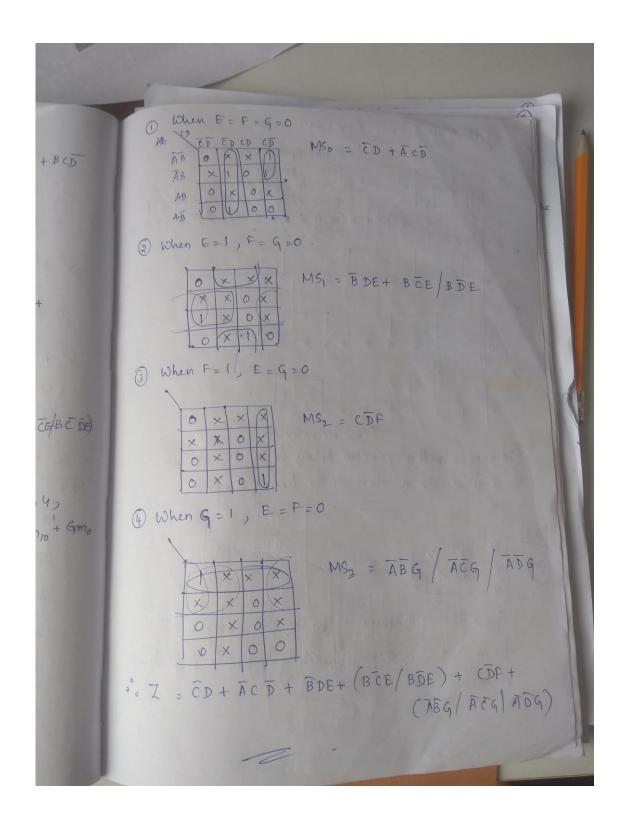

| 4 | b) | Z(A, B, C, D, E, F, G) = Σ m (2, 5, 6, 9) + Σ d (1, 3, 4, 13, 14) + E(m <sub>11</sub> + m <sub>12</sub> ) + Fm <sub>10</sub> + Gm <sub>0</sub> • K-Map for given function • K-Map for E=0, F=0, G=0  • Obtain MS0 • K-Map for E=1 • Obtain MS1 • K-Map for F=1 • Obtain MS2 • K-Map for G=1 • Obtain MS3 • Obtain final minimum solution                                                                    | 1M x 5   | 5M | 10 M |

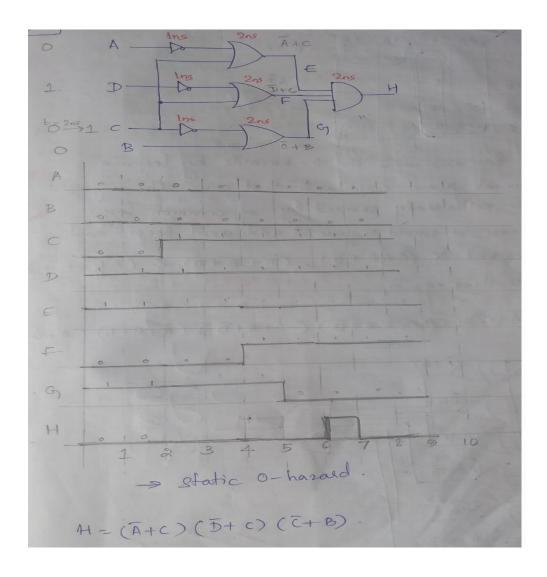

| 5 | a) | In the circuit shown below, assume the inverters have a delay of 1 ns and the other gates have a delay of 2 ns.  Initially A = B = C = 0 and D = 1; C changes to 1 at time 2 ns. Draw a timing diagram showing the glitch corresponding to the hazard.  • Show timing diagrams for all inputs  • Obtain timing diagrams for intermediate outputs  • Obtain timing diagram for output and showing the hazard | 2M x 3   | 6M | 10 M |

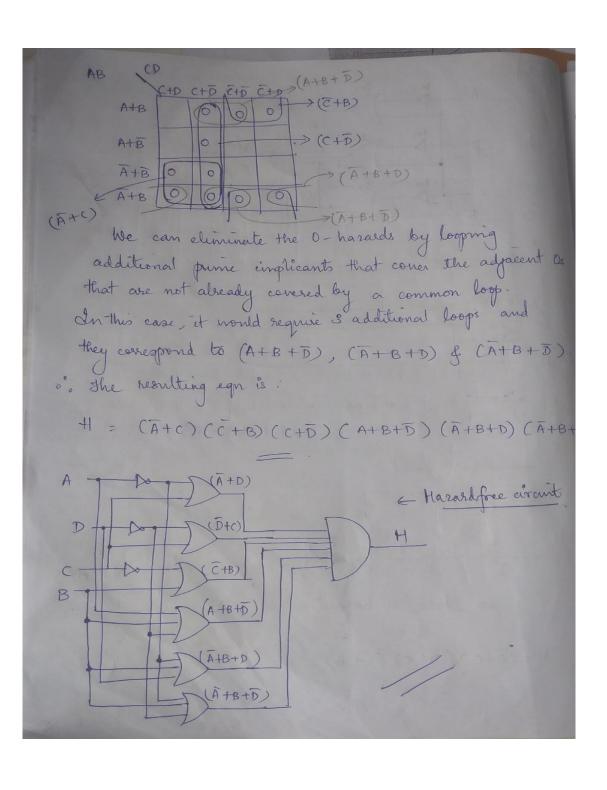

|   | b) | Identify the hazard as per the circuit given below.                                                                                                                                                                                                                                                            |        |    |     |

|---|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----|-----|

|   | ٠, | Modify the circuit so that it is hazard-free.                                                                                                                                                                                                                                                                  |        |    |     |

|   |    | <ul> <li>Identify the type of hazard</li> <li>Obtain the circuit expression with hazard</li> <li>Draw the circuit with hazard and mark the hazard in it</li> <li>Obtain the hazard free expression and draw the corresponding circuit diagram</li> </ul>                                                       | 1M x 4 | 4M |     |

|   |    |                                                                                                                                                                                                                                                                                                                |        |    |     |

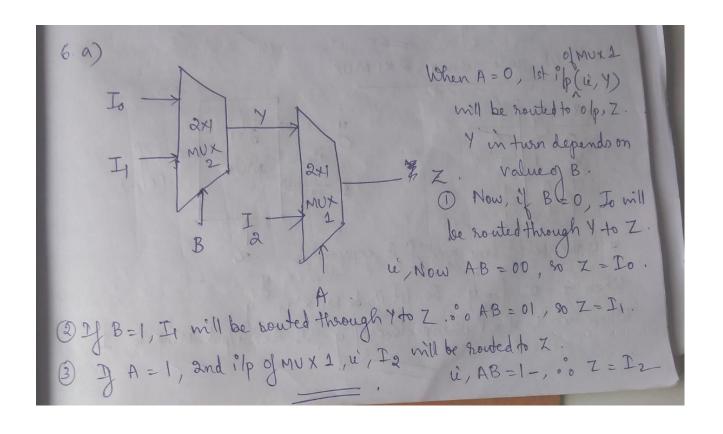

| 6 | a) | Show how two 2:1 multiplexers (with no added gates) could be connected to form a 3:1 MUX. Input selection should be as follows:  If AB = 00, select I <sub>0</sub> If AB = 01, select I <sub>1</sub> If AB = 1- (B is a don't care), select I <sub>2</sub> .  • Show the implementation with necessary details | 2M     | 2M | 10M |

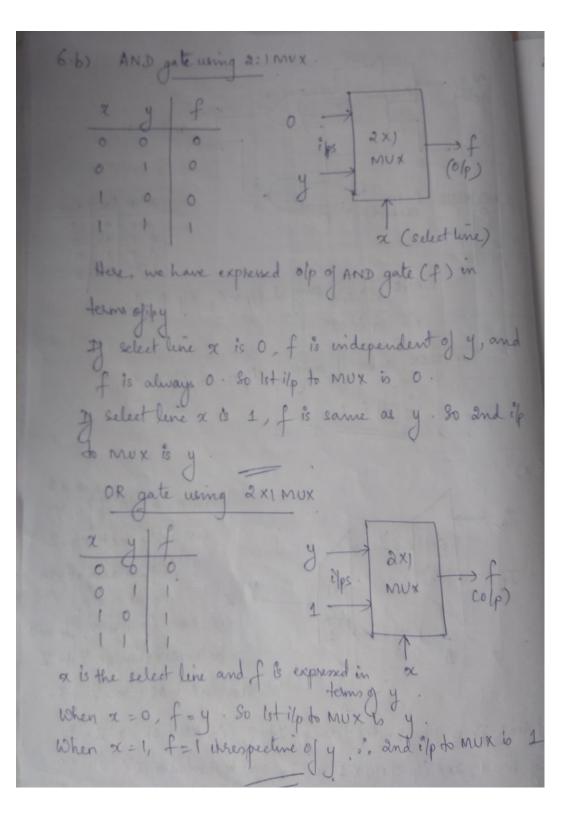

|   | b) | Implement AND gate and OR gate using 2:1 MUX  Implement AND gate using 2:1 MUX  Implement OR gate using 2:1 MUX                                                                                                                                                                                                | 2M x 2 | 4M |     |

| a) What do you mean by hazards in combinational logic? What are the different types of hazards? Explain.  • Description of hazards • 3 types of hazards • Description of each type with diagram/example  b) Obtain the timing diagram for the circuit shown below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.  7  Write the truth table for Binary to Gray code converter  8 and realize the same using four 8:1 multiplexers. • Binary to Gray code conversion using truth table  4M  0.5M x  8  4M  2M x 3  6M  2M x 3  6M  2M x 2  4M  10 M |   | c) | Using four-valued logic, find A, B, C, D, E, F, G and H from the below circuit: |        |     |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|---------------------------------------------------------------------------------|--------|-----|------|

| a) What do you mean by hazards in combinational logic? What are the different types of hazards? Explain.  • Description of hazards  • 3 types of hazards  • Description of each type with diagram/example  b) Obtain the timing diagram for the circuit shown below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.  7  10 M  • Show timing diagram of V  • Show timing diagrams of Z  Write the truth table for Binary to Gray code converter 4M and realize the same using four 8:1 multiplexers. 2M 10M 10 M                                    |   |    | 0 $B$ $F$ $G$ $F$ $G$ $F$ $G$               |        | 4M  |      |

| What are the different types of hazards? Explain.  • Description of hazards  • 3 types of hazards  • Description of each type with diagram/example  b) Obtain the timing diagram for the circuit shown below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.  7  10 M  • Show timing diagram of V  • Show timing diagrams of Z  Write the truth table for Binary to Gray code converter and realize the same using four 8:1 multiplexers. 2M 10M 10 M                                                                                              |   |    |                                                                                 |        |     |      |

| Description of hazards     3 types of hazards     Description of each type with diagram/example      Obtain the timing diagram for the circuit shown below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.       Show timing diagram of V     Show timing diagrams of Z   Write the truth table for Binary to Gray code converter and realize the same using four 8:1 multiplexers.  2M x 3  6M  2M x 3  6M  2M x 3  6M  10 M  10 M                                                                                                                |   | a) | What do you mean by hazards in combinational logic?                             |        |     |      |

| Obtain the timing diagram for the circuit shown below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.   2M x 2 4M  Show timing diagram of V Show timing diagrams of Z  Write the truth table for Binary to Gray code converter and realize the same using four 8:1 multiplexers.  2M 10 M  10 M                                                                                                                                                                                                                                                    |   |    | What are the different types of hazards? Explain.                               |        |     |      |

| Description of each type with diagram/example    Dobtain the timing diagram for the circuit shown below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.    The show timing diagram of V                                                                                                                                                                                                                                                                                                                                                            |   |    | Description of hazards                                                          | 2M x 3 | 6M  |      |

| b) Obtain the timing diagram for the circuit shown below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.  2M x 2 4M  Show timing diagram of V Show timing diagrams of Z  Write the truth table for Binary to Gray code converter and realize the same using four 8:1 multiplexers. 2M 10M 10 M                                                                                                                                                                                                                                                     |   |    | 3 types of hazards                                                              |        |     |      |

| below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.  2M x 2 4M  Show timing diagram of V  Show timing diagrams of Z  Write the truth table for Binary to Gray code converter and realize the same using four 8:1 multiplexers.  2M x 2 4M  10 M  10 M                                                                                                                                                                                                                                                                                            |   |    | Description of each type with diagram/example                                   |        |     |      |

| Show timing diagram of V     Show timing diagrams of Z  Write the truth table for Binary to Gray code converter and realize the same using four 8:1 multiplexers.  2M x 2 4M  4M  10 M  10 M                                                                                                                                                                                                                                                                                                                                                                                           |   | b) | below. Assume that the AND gate has a delay of 10                               |        |     |      |

| Write the truth table for Binary to Gray code converter and realize the same using four 8:1 multiplexers.  Market Show timing diagrams of Z  Write the truth table for Binary to Gray code converter and the same using four 8:1 multiplexers.  Market Show timing diagrams of Z                                                                                                                                                                                                                                                                                                       | 7 |    | X - 1                                                                           | 2M x 2 | 4M  | 10 M |

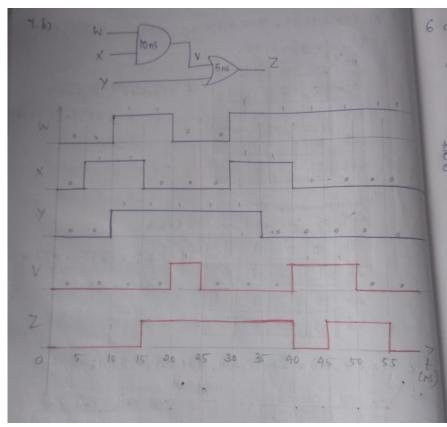

| Write the truth table for Binary to Gray code converter 4M and realize the same using four 8:1 multiplexers. 2M 10M 10 M                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |    | Show timing diagram of V                                                        |        |     |      |

| 8 and realize the same using four 8:1 multiplexers. 2M 10M 10 M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |    | Show timing diagrams of Z                                                       |        |     |      |

| 8 and realize the same using four 8:1 multiplexers. 2M 10M 10 M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |    |                                                                                 |        |     |      |

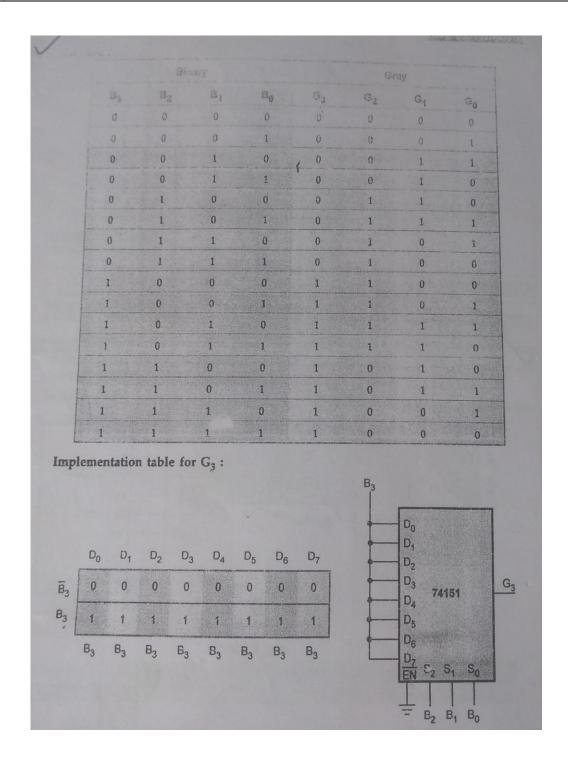

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |    | Write the truth table for Binary to Gray code converter                         | 4M     |     |      |

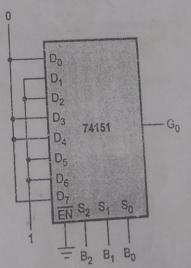

| Binary to Gray code conversion using truth table 4M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 8  | and realize the same using four 8:1 multiplexers.                               | 2M     | 10M | 10 M |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |    | Binary to Gray code conversion using truth table                                | 4M     |     |      |

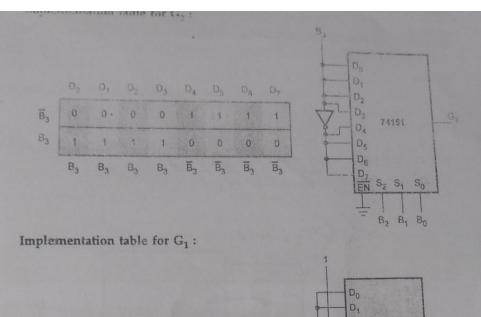

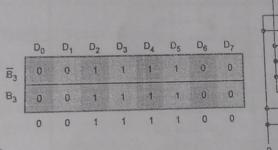

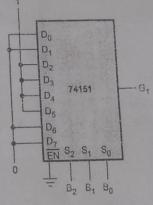

- Implementation table for G3, G2, G1 and G0

- Obtain all 8 inputs to be given to each 8:1 MUX for G3, G2, G1 and G0 and implementation of four 8:1 multiplexers giving the above obtained inputs

## **SOLUTIONS**

| 1   | Find the minimum SOP and the minimum POS for each function:               |

|-----|---------------------------------------------------------------------------|

| (a) | $F(a, b, c, d) = \Pi M (0, 1, 6, 8, 11, 12)$                              |

| (b) | $F(a, b, c, d) = \Sigma m (1, 3, 4, 11) + \Sigma d (2, 7, 8, 12, 14, 15)$ |

|     |                                                                           |

| 2 | Find a minimum SOP solution using Quine McCluskey method                          |

|---|-----------------------------------------------------------------------------------|

|   | $F(a, b, c, d) = \Sigma m (2, 3, 4, 7, 9, 11, 12, 13, 14) + \Sigma d (1, 10, 15)$ |

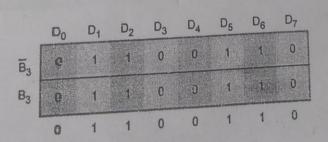

| 2 0 0 2 0 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1                       | 2001   Index 1 001   Index 2 001   Index 3 001   Index 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 000<br>2 001<br>4 010<br>3 00<br>9 100<br>10 101<br>12 110<br>7 011<br>11 101<br>13 110<br>14 111 | $\begin{array}{c} (1,3) \\ (1,3) \\ (1,9) \\ (2,10) \\ (2,10) \\ (3,11) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1) \\ (1$ | $     \begin{array}{c c}       00 - 1 \\       -001 \\       \hline       -001 \\       \hline       -010 \\       \hline       -010 \\       \hline       -010 \\       \hline       -010 \\       \hline       -011 \\       \hline       10 - 1 \\       \hline       1-01 \\       \hline       1-10 \\       \hline       110 - 0     \end{array} $ |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,3,9,11 -<br>1,9,3,11<br>2,3,10,11<br>2,10,3,11<br>3,7,11,15 | -0-1 } II -0-1 II -0-1 } II -0-1 I | PIs<br>4,12<br>1,3,9,1<br>2,3,10,1<br>3,7,11,1<br>9,11,13,                                          | $ \begin{array}{c} (12,14) \\ (11,15) \\ (13,15) \\ (14,15) \end{array} $ $ \begin{array}{c} -100 \\ 1-0-1 \\ 1-01-5 \end{array} $ $ \begin{array}{c} -15 \\ 1-1-1 \\ 15 \end{array} $ $ \begin{array}{c} 15 \\ 1-1-1 \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11-1                                                                                                                                                                                                                                                                                                                                                     |

| PI chart       | _ ,        | ,   |       |    |     |       |     |      |      |    |

|----------------|------------|-----|-------|----|-----|-------|-----|------|------|----|

| 14             | mž         | \m3 | 104   | m7 | mg. | mil   | M12 | m13  | m 14 |    |

| 8CD 4,12       |            |     | 8     |    |     | 41.14 | ×   |      |      |    |

| BD 1,3,9,11    |            | ×   | 200   | 1  | ×   | X     |     |      |      |    |

| Bc 2,3,10,11   | <b>(X)</b> | ×   |       |    |     | ×     |     | 1001 |      |    |

| CD 3,7,11,15   |            | ×   | 411   | 8  |     | ×     |     | 100  |      |    |

| AD 9,11,13,15  |            |     | 241   |    | X   | ×     |     | X    |      | 31 |

| AC 10,11,14,15 |            |     | . 110 |    | 1   | ×     |     | -00  | X    |    |

| AB 12,13,14,15 | 1 50       |     | -131  |    | 8   |       | ×   | ×    | X    |    |

Essential PDs -> BCD, BC, CD.

These 3 terms together cover menterns 2,3,4,7,11 & 12 Remaining menterns to be covered are 9,13 & 14.

- ... We should select a minimum no! of PI, that cover these 3

- 1) 9 can be covered by BD or AD. We select AD as this term covers both 9 and 13.

- 2) Now, only 4 is left. This can be conered by AC or AB we can chose any one of these.

- ... Minimum sopredution is

BCD+Bc+CD+AD+AC

BCD+BC+CD+AD+AB

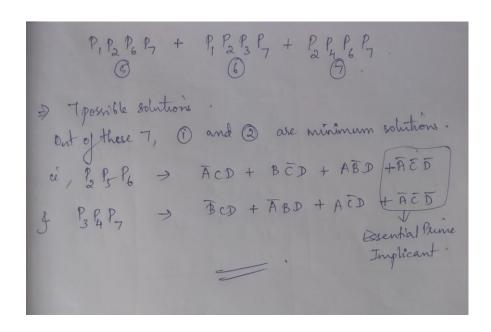

| 3 | Find all minimum SOP solutions for the function using Petrick's method |

|---|------------------------------------------------------------------------|

|   | $F(a, b, c, d) = \Sigma m (0, 3, 4, 5, 7, 9, 11, 13)$                  |

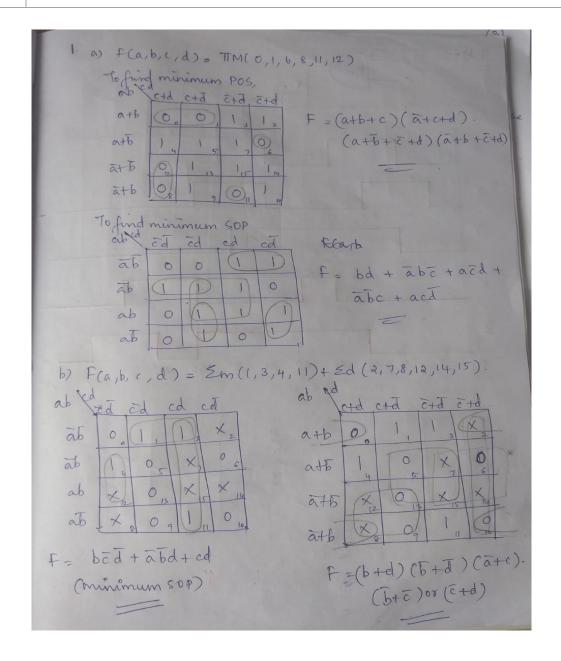

| 3. F(a,b,c,d) = Em (0,3,4,5,7      |              |

|------------------------------------|--------------|

|                                    | Column 2     |

| 0 0000 Index 0. 0 0000 0,4         | 0_00_0       |

| 3 0011 Index 1 4 0100 15           |              |

| 4 01000                            | 010-         |

| 5 0101 - Index 2 3 0011 3-         | 7 0-11 (-11) |

|                                    | 1 -011 are   |

| 1011                               | 7 01-1 PDs.  |

| Index 3                            | 13 _ 101     |

|                                    | 10-1         |

| 13 1101/ 9,                        | 13 1-01      |

| PDs.                               |              |

| 0,4 0_00 ACD                       |              |

| 415 010 - ABC                      |              |

| 3.7 0-11 ACD                       |              |

| 3.11 -011 BCD                      |              |

| 5.7 01-1 ABD                       |              |

| 5/13 -101 BCD                      |              |

| 9,11 10-1 ABD                      |              |

| 9,13 1-01 ACD                      |              |

| PI chast                           |              |

| # PIs [mo   m3   m4   m5   m7   m9 | m11 m13      |

| EPI                                | 9 18 9 18 1  |

| ACDOM X                            |              |

| ABC 415 X X                        | Pı           |

| X X                                | P2           |

| ACD 3,1                            | X P3         |

| BCD 3,111 ×                        | P4           |

| 100 57                             | 00 0         |

| 513                                | 0-           |

| ABD 9,11 X                         | × P6         |

| X                                  | X / P7       |

| ACD 9,13                           |              |

ACD is an essential PI. It covers mentions 0 and 4.

So only remaining PDs need to be considered in Petrick's method to cover minterns 3,5,7,9,11 & 13 Naming them as P1, P2. ... P7.

0° P = (P2+P3)(P1+P4+P5)(P2+P4)(P6+P7) (P3+P6) (P5+P7)

= (P2+P3) (P2+P4) => P2+P3P4 (P6+P7) (P6+P3) => P6+ B767

50 P = (P3+P6)(P+P5P6)(P1+P4+P5)(P2+P4) (P1+P4+P5) (P5+P7) => P5+P1P7+P4P7

· · · P = (P2+P3P4)(P6+P3P7)(P5+P1P7+P4P7)

= (P2 P6 + P2 P3P+ P3 P4 P6 + P3 P4 P7) (P5 + P1 P7 + P4 P7)

= \$P\_2 P\_5 P\_6 \$ + P\_2 P\_3 P\_5 P\_7 + P\_3 P\_4 P\_5 P\_6 + P\_3 P\_4 P\_5 P\_7 + P, B, P6 P7 + P, P2 P3 P7 + P, P3 P4 P6 P7 + P, P3 P4 P7 +

Pary Po P7 + BB4P7 + BP4P6P7 + BP4P7.

= P2 P5 P6 + P3 P4 P7 + P2 P3 P5 P7 + P3 P4 P5 P6 +

4 Using the method of map-entered variables, use 4-variable maps to find a minimum SOP expression for:

(a)  $F(A, B, C, D, E) = \sum m(0, 4, 6, 13, 14) + \sum d(2, 9) + E(m_1 + m_{12})$

(b)  $Z(A, B, C, D, E, F, G) = \Sigma m (2, 5, 6, 9) + \Sigma d (1, 3, 4, 13, 14) + E(m_{11} + m_{12}) + Fm_{10} + Gm_0$

MS. = AD + ACD + BCD

| 2 | When & | 1=  |   |   |    |

|---|--------|-----|---|---|----|

|   | AB Y   | CDI | 0 | 4 | CT |

|   | AB     | X   | 0 | 0 | X  |

|   | AB _   | 12  | 0 | 0 | X  |

|   | AB     | a   | X | 0 | X. |

|   | 43     | 0   | X | 0 | 0  |

» P = MSO + MSI

=

$$\overline{A}\overline{D} + A\overline{C}D + BC\overline{D} + (\overline{A}\overline{B}\overline{C}E/\overline{B}\overline{C}DE) + (\overline{A}\overline{B}\overline{C}E/\overline{B}\overline{C}DE)$$

(b) Z(A,B, C,D,E,F,G) = Em(2,5,6,9) + Ed(1,3,4)

13,14)+, E(m1+m12)+.fm10+6m

| ABUS | CD.  | ED  | CD   | сб   |

|------|------|-----|------|------|

| ĀB   | G    | X   | X    | 1 2  |

| ĀB . | X    | 15  | 0 7  | 16   |

| AB   | E 12 | X   | 0 15 | × ny |

| AB ] | 08   | 1 9 | E    | Flos |

|   | 5 (a) | In the circuit shown below, assume the inverters have a delay of 1 ns and the other gates have a delay of 2 ns. Initially $A = B = C = 0$ and $D = 1$ ; C changes to 1 at time 2 ns. Draw a timing diagram showing the glitch corresponding to the hazard. |

|---|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ı |       |                                                                                                                                                                                                                                                            |

|   | (b)   | Identify the hazard as per the circuit given below. Modify the circuit so that it is hazard-free.                                                                                                                                                          |

Show how two 2:1 multiplexers (with no added gates) could be connected to form a 3:1 MUX.

Input selection should be as follows:

If AB = 00, select I<sub>0</sub>

If AB = 01, select I<sub>1</sub>

If AB = 1- (B is a don't care), select I<sub>2</sub>.

(b) Implement AND gate and OR gate using 2:1 MUX

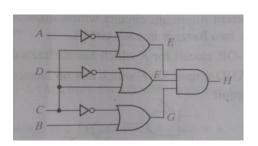

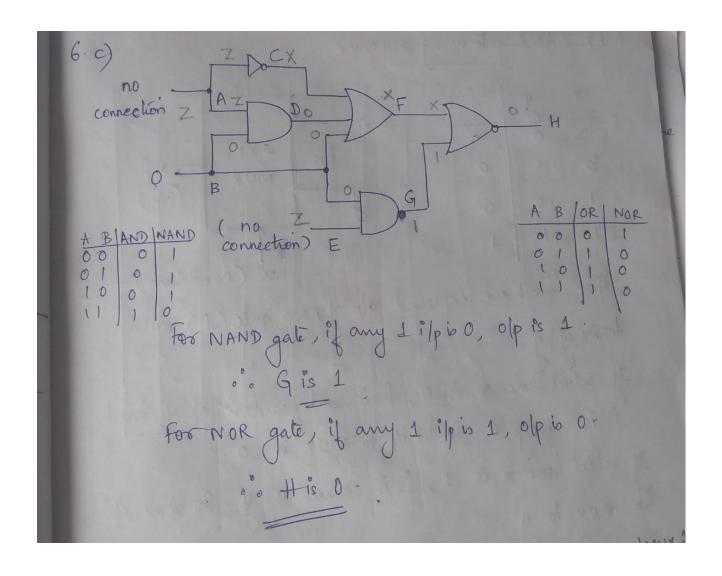

(c) Using four-valued logic, find A, B, C, D, E, F, G and H from the below circuit:

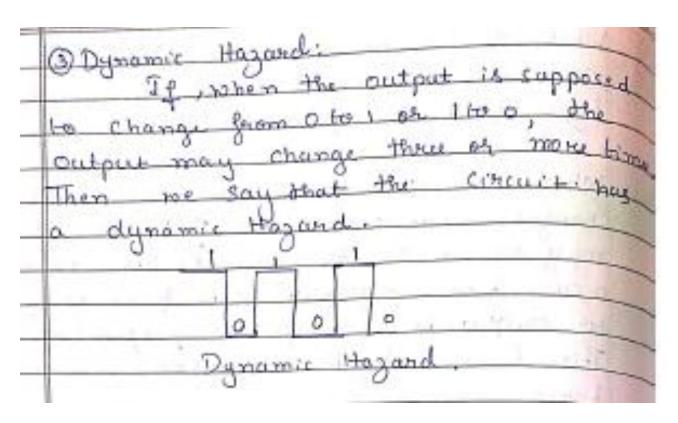

- 7 (a) What do you mean by hazards in combinational logic? What are the different types of hazards? Explain.

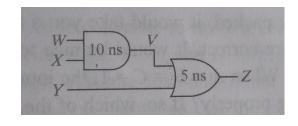

- (b) Obtain the timing diagram for the circuit shown below. Assume that the AND gate has a delay of 10 ns and the OR gate has a delay of 5 ns.

|   | When the input to a combinational cincu     |

|---|---------------------------------------------|

|   | may appear in the suite of                  |

|   |                                             |

|   | This leads to Huzards in Combinational      |

|   | And the                                     |

| _ | Different Egper of Hozards are              |

|   | The Sale of                                 |

|   | 3 Dynamic Hazard.                           |

| _ | Static 1 Hannel                             |

|   | The panes to any single inner               |

|   | the Combination of Otomorophia              |

|   | go to O when it Should remain a combi       |

|   | Then we say that cincuit has a Static I hay |

|   |                                             |

|   | Static Y Hazard.                            |

|   |                                             |

|   | 2) Static O Hazard:                         |

|   | If the output may momentanily               |

|   | ne Say that the count has a                 |

|   | Static O Hazand                             |

|   | 0 0                                         |

|   | static o Hazard.                            |

## Implementation table for G<sub>0</sub>: