$Internal\ Assessment\ Test\ \ I-Sept.\ 2019$

| b:            |                               | 111011                                                                                    |                                                               | 1 – Sept. 20                       | 1        | 1       |      |     |    |

|---------------|-------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------|----------|---------|------|-----|----|

| $\overline{}$ | COMPUTER C                    | ORGANIZATION                                                                              |                                                               | Sub Code:                          | 18CS34   | Branch: | CSE  |     |    |

| ite:          | 7 / 09 / 2019                 | Duration: 90 mins                                                                         | Max Marks: 50                                                 | Sem / Sec:                         | 3 (A,B,  | C)      |      | 0   | BE |

| An            | swer <b>FIVE</b> FUI          | L questions selecting                                                                     | AT LEAST ONE ques                                             | stion FROM E                       | ACH PART | MA      | ARKS | СО  | RE |

| iı<br>C       | n terms of commands. A        | needed to execute the<br>transfers between<br>assume that the in<br>and that this address | ADD A, LOC<br>the components<br>struction itself is           | A, R4<br>and some s<br>stored in t | -        |         | [10] | CO1 | L  |

|               |                               | ting steps  lams (list of in                                                              | notructions) resi                                             | ide in me                          | emory (u | Shows ( |      |     |    |

|               | 1 PC is 1 This signal         | set to point<br>PC contents is                                                            | to first, inst. s transferred memory                          | ruction of p                       | and Rea  | d c     |      |     |    |

|               | address of som                | time require<br>assed word (10<br>memory and<br>or contents are                           | tinstruction in<br>a loaded in<br>a transferred               | this case)<br>MDR.<br>to IR.       | is read  | ou:     |      |     |    |

|               |                               | instruction in                                                                            |                                                               |                                    |          |         |      |     |    |

|               | MAR. Res<br>MDR. 3<br>are ser | ands from mend sesides in mend cycle is in the tis sent to the ALU (in forms operation    | nitialized. D<br>ALU. Simile<br>of required).<br>and sends so | perand consely, more usualt to it  | operands |         |      |     |    |

|               | is bein                       | to MAR,                                                                                   | and write                                                     | you is                             |          |         |      |     |    |

|               |                               | urce of destination                                                                       | point to no                                                   | xt instruc                         |          |         |      |     |    |

OR L3 2 (a) Assume a program with 1000 instructions. 25% of the instructions take 4 [5] CO1 clock cycles, 40% of the instructions take 5 clock cycles, and the remaining instructions take 3 clock cycles to execute respectively. Calculate the time of execution assuming basic performance equation if the clock rate of the machine is 1GHz. P=N\*S/RAns=4.05 micro sec CO2 L2 **(b)** Define Exception. Explain any 2 Kinds of Exception. [5] Exceptions Exception is any event that causes an interruption. I/O interrupts are one example of an exception. Recovery from Essons · Many computes include an earor checking code in main memory, which allows detection of everors in the stored data. If everor occurs, the control hardware actects its and informs the processor by raising an interrupt. The processor may also interrupt a program if it detects an crea or an uneual anditions while executing the instructions of program. Eg- invalid ofwde, division by zero etc Debugging

System & of there usually includes a program called delouger which helps the programmer find arewors in a program The debugger uses exceptions to provide two important facilities called trace and breakpoints trace - when a processor is operating in the trace mode an exception occurs after execution of every instruction using the debugging program as the exception-service routine The debugging program enables user to examine the contents of registers, memory locations, etc. On Return from delanguage program, next instruction in program being debugged is executed , the debugging program is activated again. The trace exception is disabled during the execution of debugging program. · Breakpoints - In this, the program being debugged is intersupted only at specific points selected by user. An instruction called trap or Software-interrupt is usually provided for this purpose. Eg- user wants to interment progr execution after instruction i. Debugging routine

| instructions)                                  | (one-address, two-addr                                                                                                         | ess, three-address                                                                                         |     |     |    |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|-----|----|

| Basic Instru                                   | tion Types                                                                                                                     |                                                                                                            |     |     |    |

| Two-address Op                                 | instruction<br>westion Source, Dest                                                                                            | nation                                                                                                     |     |     |    |

| Move B, C<br>Add A, C                          |                                                                                                                                |                                                                                                            |     |     |    |

|                                                |                                                                                                                                | - A, B contents are us                                                                                     |     |     |    |

|                                                | Sorrel, Source 2,                                                                                                              |                                                                                                            |     |     |    |

| It may be had fit in one bige. In the          | nord for usual of<br>not case, we may                                                                                          | ess instruction doesned and length & adde added and address address accumulation. This may be used values. |     |     |    |

|                                                | Load A<br>Add B<br>Store C                                                                                                     | Copy A contents to a<br>Add Beontents to accur<br>Store accumulator<br>to C.                               |     |     |    |

|                                                |                                                                                                                                |                                                                                                            |     |     |    |

| transfers for all three devices A and B is not | nd C, are connected to the b<br>levices use interrupt control,<br>allowed, but interrupt reque<br>being serviced. Suggest diff | Interrupt nesting for ests from C may be accepted                                                          | [4] | CO2 | L3 |

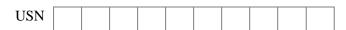

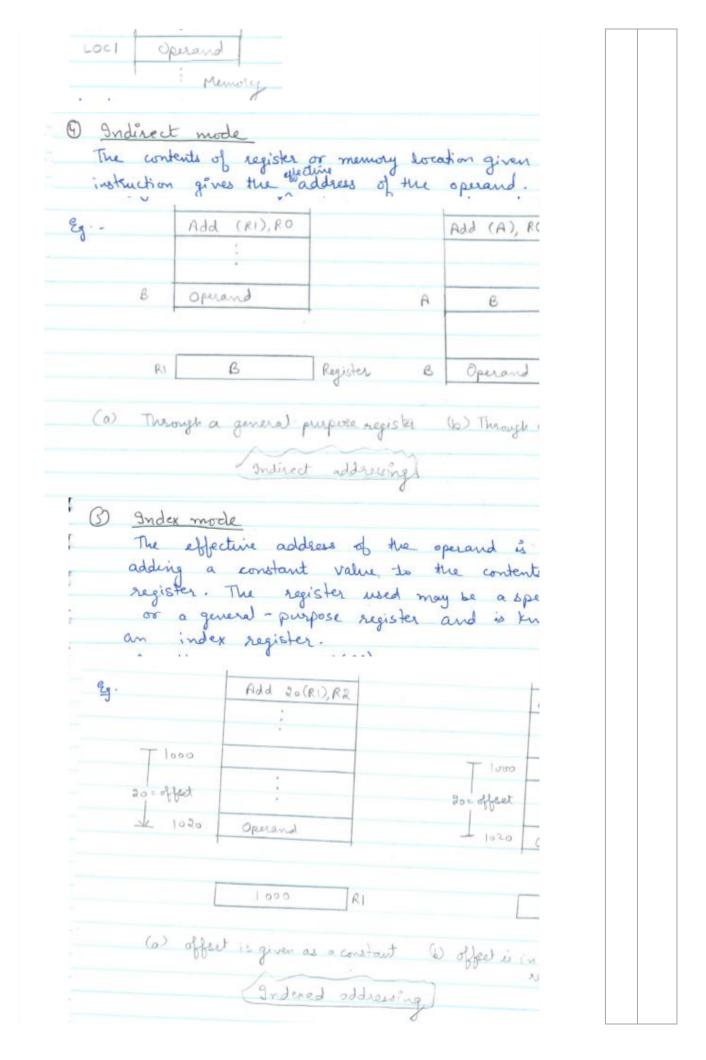

(b) Two interrupt-request lines, INTR1 and INTR2, are available, with INTR1 having higher priority. Specify when and how interrupts are enabled and disabled in each case. 4.6. (a) Interrupts should be enabled, except when C is being serviced. The nesting rules can be enforced by manipulating the interrupt-enable ags in the interfaces of A and B. (b) A and B should be connected to INTR<sub>2</sub>, and C to INTR<sub>1</sub>. When an interrupt request is received from either A or B, interrupts from the other device will be automatically disabled until the request has been serviced. However, interrupt requests from C will always be accepted. CO1 L2 **4 (a)** Explain addressing modes with example of each mode. [10] ADDRESSING MODES The different ways in which the location of an is specified in an instruction are referred to as 1 Immediate mode The operand is given explicitly in the instruction. Above instruction places value 200 in regis! egenerally, this made is used to represent @ Register mode The operand is the contents of a processor reg name of the register is given in the instruction Eg. - Move RI, Ra. Above instruction moves the contents of register generally, this mode is used to access variables 3 Absolute (Direct) mode address of the nemory location where located is given explicitly in the Prostruction. Move LOCI, LOCA Above instruction moves the operand at location Le location LOCA. representing It is generally used for global variables.

[8] C01

L2

A stack is a sist of data elements, wouldy, bytes, with the accessing restriction that elev can be added or removed at one end of the only. This end is called the top of stack,; end is called bottom. The structure is somet referred to as a pushdown stack. It is just pile of trays. It is also rolled as Lifo (los Out) stack! Push operation is used to place a. Hem on the stack, pop operation is used to the top item from the stack Assume that the first element is placed in loc BOTTOM, and when new elements are pushed onto stack, they are placed in successively lower locations. We use a stack that grows in the di of decreasing memory addresses. Consider a stack containing numerical values, with the bottom and -28 at the top. A processor & rigister is used to keep track of the addr

PART C

**5 (a)** Explain the operation of stack with example.

the element of the stack that is at the top at an time. This register is called the stack pointer (SP)

| Push =       |                                 | Subtract # Move N           | H,SP<br>EWITEM, (   | (sp)      |

|--------------|---------------------------------|-----------------------------|---------------------|-----------|

| <u>Pop</u> : |                                 | Move CSF<br>Add #           |                     |           |

| modes, we    | has Au<br>push an<br>Kuchi ons: | to increment and pop can be | d Autode<br>perform | rement as |

| Push :-      | Move                            | NEWITEM , -(                | sp)                 |           |

| Pop:-        | Move                            | (SP)+, ITEM                 |                     |           |

|              |                                 |                             | 100                 |           |

| 3₽ →         | 19                              | 7                           |                     | -28       |

| 31           | -28                             |                             | SP->                | 17        |

|              | 17                              | Stack                       |                     | 739       |

|              | 739                             |                             |                     |           |

|              | ,                               |                             |                     | *         |

|              | :                               |                             |                     |           |

|              | 43                              | J                           |                     | 43        |

|              |                                 |                             |                     |           |

|              | 19                              |                             | ITEM                | - 28      |

| MSTIWIG      |                                 |                             |                     |           |

SAFEPUSH Compare #1500, SP Check to see if SP Branch = O FULLEROR an address value eg, or less than 1500. 9 Stack is full. Branch soutie FULLERROR More NEWITEM, - (SP) Otherwise, push eleme memory location NEW Routine for a wofe push operation SAFEPOP Compare #2000, SP check to see if s Branch 70 EMPTY ERROR an address value than down. It it d stack is empty - B soutine EMPTY ERRO Move (SP)+, ITEM Otherwise, pop the to stack into memory los ITEM Rouline for a safe pop operation

Differentiate between subroutine and Interrupt service Routine **OR**

SUBROUTINES In a program, if a particular subtask is performed me on different data values, such substask is usually a subsortine. Eg subsorterie to evaluate the sine To save space, only one copy of the instructions that the Substitute is placed in the memory, and any that requires me use of the subscritime simply be to Pts starting location - This beauching to a subson called as calling the subruntine - The instruction that this branch operation is named a Call instruction. The is said to return (resume execution, continuing immedia the instruction) to the program that called it by ever a Return instruction. Converds of PC must be saw the Call instruction to enable correct return to the The method followed to call and return from subsoute referred to as is subroutine linkage method. Eg- save a return address in a specific location like a link register. When substructive completes its task, the instruction returns to the calling program by branching indirectly through the link register,

| all instruction                                           |     |     |    |

|-----------------------------------------------------------|-----|-----|----|

| "Store contents of PC in link register                    |     |     |    |

| · Branch to the target address specied by the isn         |     |     |    |

| Return instruction                                        |     |     |    |

| · Branch to the address contained in the link re          |     |     |    |

| Memory Calling Memory S                                   |     |     |    |

| location Program location                                 |     |     |    |

|                                                           |     |     |    |

|                                                           |     |     |    |

| 200 Call SUB                                              |     |     |    |

| 204 next instruction                                      |     |     |    |

| · · · · · · · · · · · · · · · · · · ·                     |     |     |    |

|                                                           |     |     |    |

|                                                           |     |     |    |

| PC 204                                                    |     |     |    |

| 1.                                                        |     |     |    |

| Link 204                                                  |     |     |    |

| Call Return                                               |     |     |    |

|                                                           |     |     |    |

| (Substitute luikage using a link hagister)                |     |     |    |

| Substitutine nesting and the processor stack.             |     |     |    |

| Subscritine nesting - when one subscritine calls another  |     |     |    |

| The return address of second call is also stored in which |     |     |    |

| saving contents of link register at other excation.       |     |     |    |

| Return addresses are generated and used in a LIFO o       |     |     |    |

| particular register is designated as stack poster, SP, Th |     |     |    |

| to a stack called processor stack. The Call Prestruction  |     |     |    |

| the contents of PC onto processor stack & loads su        |     |     |    |

| address into PC. The Return instruction pops the roturn , |     |     |    |

| from the processor stack into PC.                         |     |     |    |

|                                                           |     |     |    |

|                                                           |     |     |    |

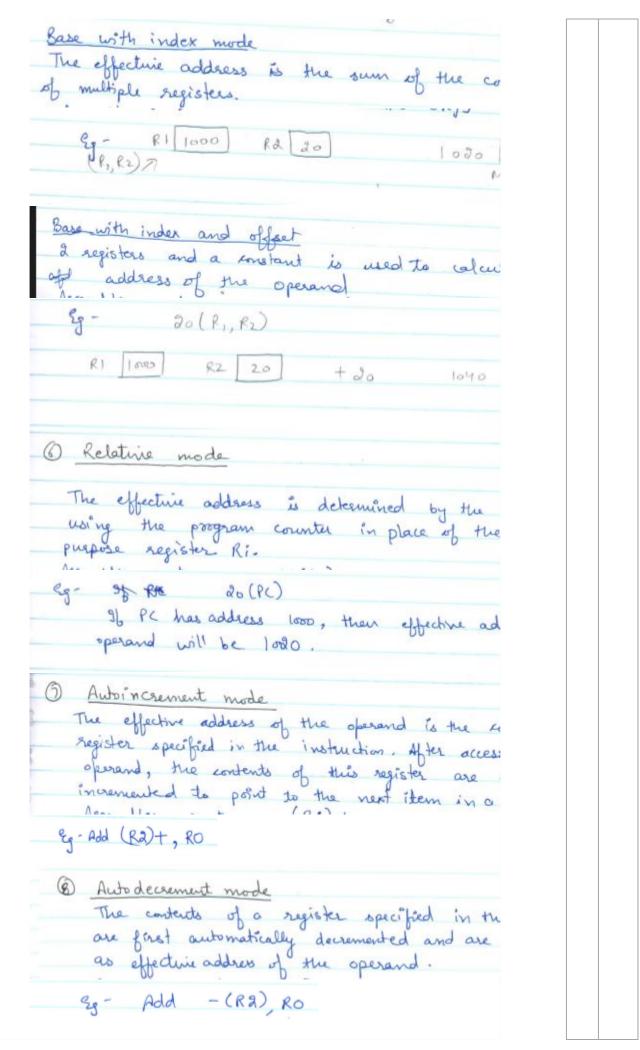

| xplain any three assembler directives with example.       | [3] | CO1 | L2 |

**(b)** Ex

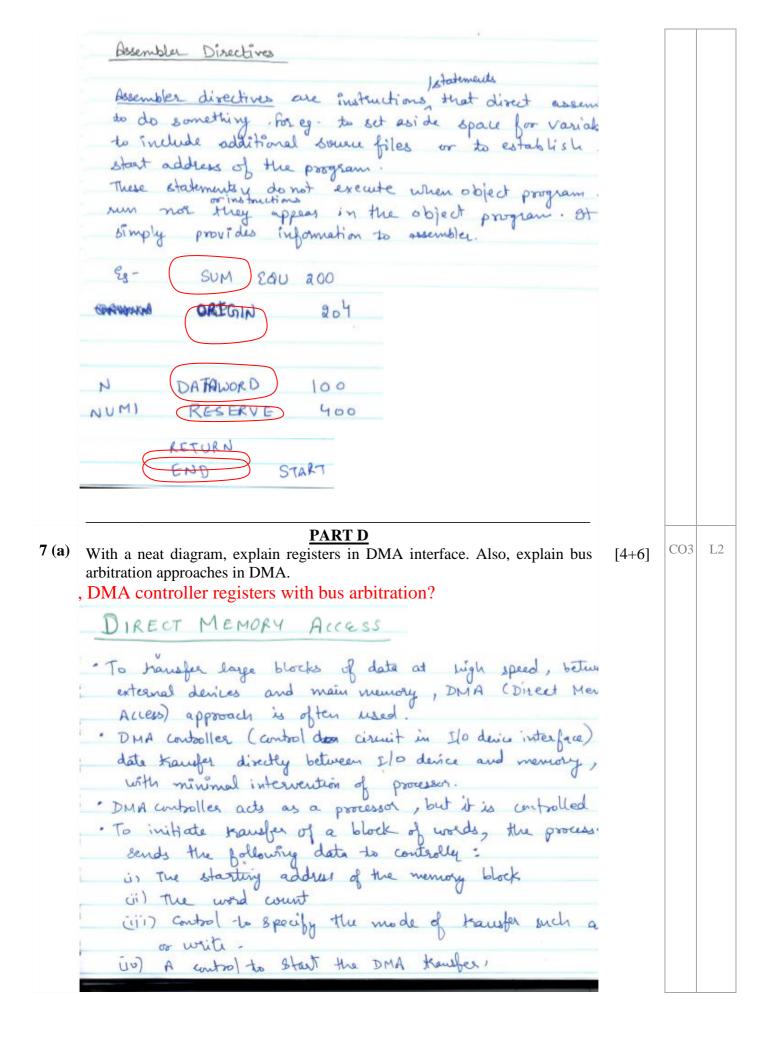

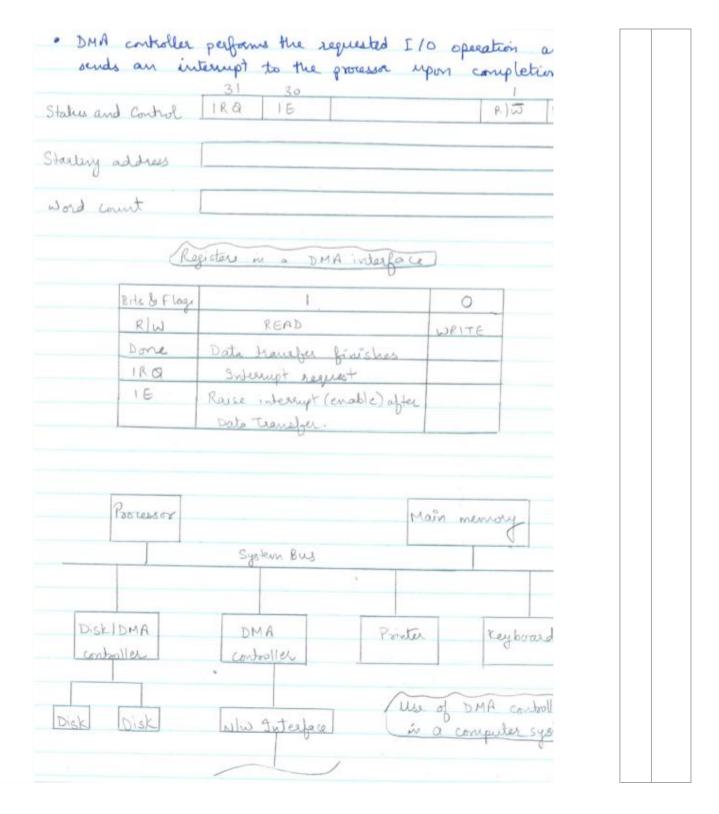

- · Memory accesses by the processor and DMA Controller interview. DMA derices have higher pointing than processor over bus control.

- Tycle Stealing DMA controller steals memory cycle from processor, though processor originates most memory access. For each byte to be transferred, DMA interrupt processor.

- access to the main memory to transfer a block of a without Her intercuption.

A conflict may arise if both the processor and a DMA cor two DMA controllers try to use the bus at the sau time to access the main memory. To resolve this, but arbitration methods are required.

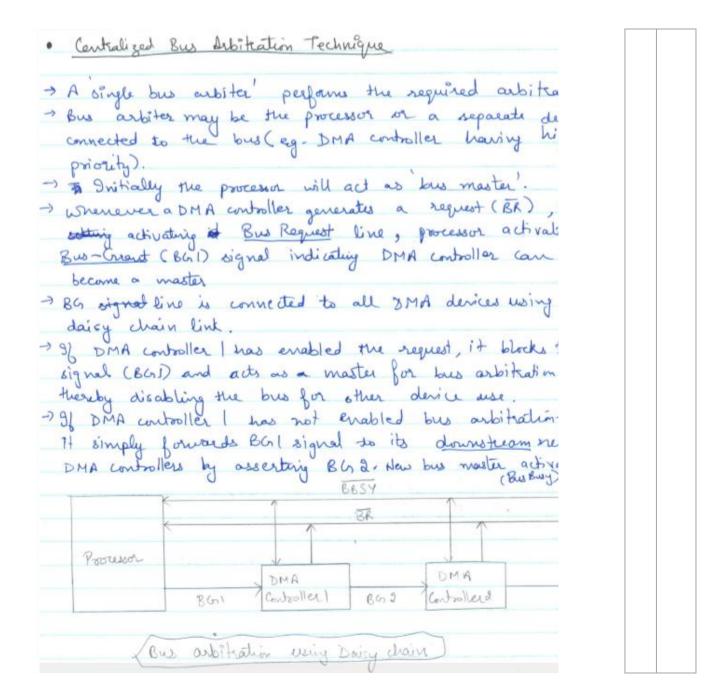

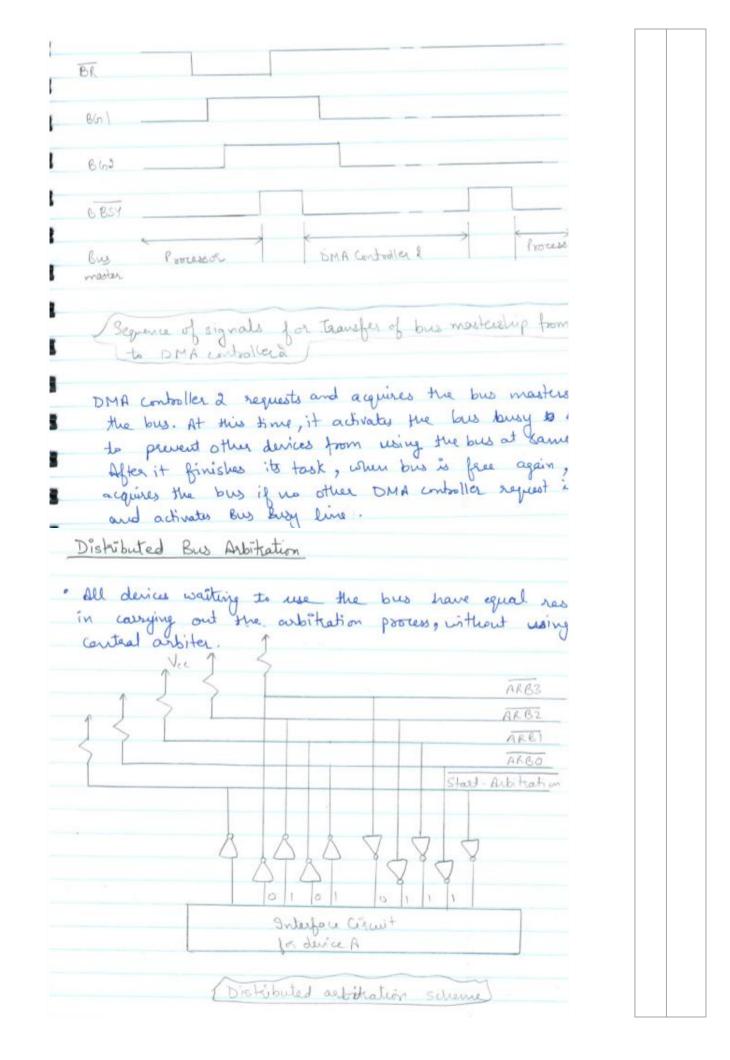

## Bus Asbitration

- · Bus master: device that initiate data transfers on to The next device can take control of the bus after to current master relinquishes control.

- · Bus Arbitation: process by which the next der to become master is selected. I main types:

- 1 Centralized Arbitration 2 Distributed Arbitration

| rumber.                                                                                                                                           |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Derices start contending for bus by enabling 6 start.  signal and place their 4-bit identification manufer                                        |  |

| the bus (4 lines ARBO-ARB3).                                                                                                                      |  |

| I Device having has highest identification number is &                                                                                            |  |

| to get the granted service.                                                                                                                       |  |

| Jelection procedure:                                                                                                                              |  |

|                                                                                                                                                   |  |

| · Assume that two devices A and B have their idea                                                                                                 |  |

| numbers 5 and 6 respectively.                                                                                                                     |  |

| ine id of A = 0101                                                                                                                                |  |

| id of B= 0110.                                                                                                                                    |  |

| Device A transmits the pattern old on arbitration of                                                                                              |  |

| device & sends the pattern 0110 on arbitration le                                                                                                 |  |

| · A code value is calculated applying "Logical OR identification numbers of contending devices.                                                   |  |

| i.e. 0101                                                                                                                                         |  |

| +_0110                                                                                                                                            |  |

| 0111 <- code generated.                                                                                                                           |  |

| This code generated by 'OR' operation is sent                                                                                                     |  |

| to all the contending derices.                                                                                                                    |  |

| · sach contending derice, compares its own id on as lines with code value bit by bit starting from, . when it frinds a mismatch in any bit place, |  |

| him with code value bit by bit starting from                                                                                                      |  |

| . When It finds a mismatch in any bit place,                                                                                                      |  |

| semaining lower order sits of that divice id are disabled to 0.                                                                                   |  |

| device A 0101 Code 0111                                                                                                                           |  |

|                                                                                                                                                   |  |

| mismatch                                                                                                                                          |  |

| So now derice A shows 0/00.                                                                                                                       |  |

|                                                                                                                                                   |  |

| derice 8 0110 code 011                                                                                                                            |  |

| wisnatch                                                                                                                                          |  |

| · ollo code.                                                                                                                                      |  |

| now > 'OR' for new codes 0100                                                                                                                     |  |

| +0110                                                                                                                                             |  |

| 0110                                                                                                                                              |  |

| This means device is wind the election and is chose                                                                                               |  |

| the bus master                                                                                                                                    |  |

|                                                                                                                                                   |  |

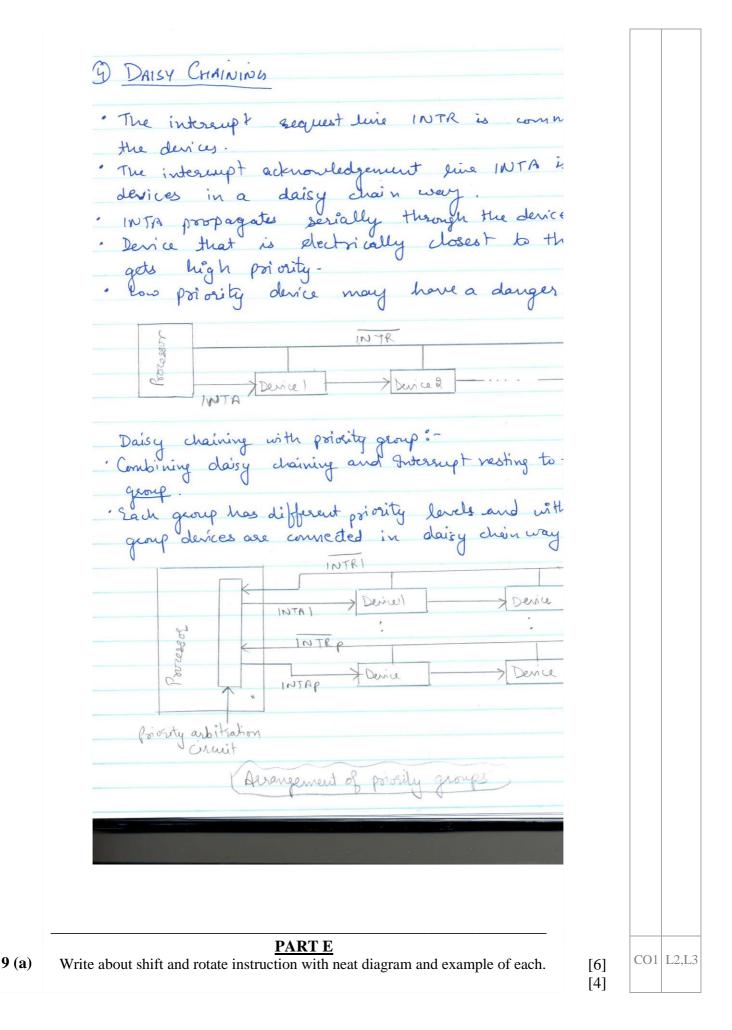

Explain various methods for handling interrupts from multiple devices with neat diagram.

[10]

L2 CO2

Handling multiple devices/interrupts (polling, vectored interrupts, interrupt nesting, daisy chaining)

Handling multiple devices · Multiple derices can initiate interrupts. They use interrupt request line. following techniques may be used :-- Polling - Vectored Interrupts - guterrupt nesting - Daisy chaining. 1) POLLING

- · The IRO (interrupt request) bit in the status device is set to when a device is requesting an The Interrupt service routine polls the I/o device to the bus.

- " The first device encountered with the IRO bit s serviced and ISR is invoked.

- · It is easy to implement, but too much time. checking the IRO of all derices , though so may not be requesting service.

- a) VECTORED INTERRUPTS

- · Device requesting an interrupt identifies itself dire the processor.

(4 to 8 bils) The device sends a special code to the processor · The code rontains o identification of the device, starting address of ISR, address of the branch to ISR lig ISR not at that los The evention pointed to by the intersupting de to store the starting address of the interen soutine. This address is called interrupt vect reads it and loads it into PC. when the processor is heady to receive in code, it a may activate interrupt-acknown INTA. The Ho direce responds by sending it vector code and truing off the INTR styn SNTERRUPT NESTING · Disabling Intercupts during execution of the not favor derives which need immediat eg, keeping track of time of day. · Pre-emption of low priority interrupt by higher priority interrupt is known as Inte · Only interrupts requests of higher priority, accepted during execution of Ish of lower pr · A priority level is assigned to processor which of the program that is currently being exe Duly higher priority interrupts than this area · Processor's priority is encoded in a few bi

status word which can be changed by proge called privileged instructions, which can be while processor is running in supervisor mode executing OS routines) · An attempt to execute a poivileged instructi in user mode leads to a special type called a privilege exception. · A multiple-priority scheme can be implemented using separate interrupt reguest and interrup lines for each device. Each interrupt - request li assigned a different priority level. Interrupt regu seceived over these lines are sent to a priori arbitration circuit in the processor. A request is only if it has a higher priority level than assigned to the processor. INTRI 2 Device Deviced INTAL Priority arbitration circuit Implementation of interrupt priority using individual and acknowledge lines

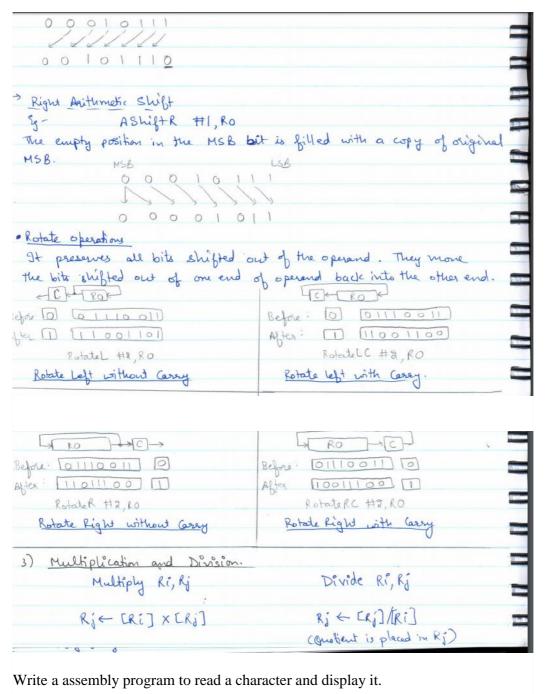

| Shift and Rotate Instructions.  Rest instructions shift bits of, an operand to right or left some specified number of bit positions.  Rotate instructions more the bits that are shifted out of one end of the operand back into the other end.  Logical Shifts  Shift an operand over a number of bit positions specified in a court operand contained in the instruction. Court operand may be given as an investigate operand or in may be contained |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| in a processor register.  Syntax LShift Count, det  LShift R count, det  Bits shifted out are passed through carry flog, ( & then dropped.)  > Logical Shift Left                                                                                                                                                                                                                                                                                       |  |

| Refore 0 01110011 (Logical Shift left)  After: 1 11001100                                                                                                                                                                                                                                                                                                                                                                                               |  |

| > Logical Shift Right.  8g-  O-RO-C-  LShift R #8, RO                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Référe: [00011100] [D] (Logical Chift Right)                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Arithmetic Shifts  Arithmetic Shifts  Arithmetic Shifts  Ashift count, det  Ashift count, det                                                                                                                                                                                                                                                                                                                                                           |  |

| The empty position in the LSB (least significant bit) is filled with a zero.                                                                                                                                                                                                                                                                                                                                                                            |  |

|        | Example: - A program that reads a line of characters and displays it.                                                                                                                                                     |      |        |   |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|---|

|        | More #LOC, RO Initialize pointer register to to<br>point to the address of the first<br>location in memory where closedy                                                                                                  |      |        |   |

|        | READ Test Bit #3) NSTATUS wait for character to be Branch = O READ . entered in keyboard buffer Move Byte DATAIN (RO) DATAIN . Transfer the character from DATAIN into memory                                             |      |        |   |

|        | ECHO TestBit. #3,00TSTATUS wait for display to become scally Branch=0 Echo  MoveByte (RO), DATHOUT Move the character just send  -la display buffer register. (this clears Sourt to c)                                    |      |        |   |

|        | Compare #CR, (RO) + check i'b unovacter just read is CR (corriage return). I) not CR, then branch back & Branch #O READ read another character.                                                                           |      |        |   |

|        | Aso, increment the pointer to store next character.                                                                                                                                                                       |      |        |   |

| 10 (a) | OR  What is an Interrupt? With an example, illustrate the concept of interrupt.                                                                                                                                           | [10] | CO2 L2 | 2 |

|        | INTERRUPTS  In program-controlled 210 processor repeated                                                                                                                                                                  |      |        |   |

|        | dence states. During this wait loop, processor performing any useful computation. There situations where other tasks can be perform waiting for the I/O dence to become read dence may alert the processor when it become |      |        |   |

|        | This alest may be sent using a hardwa called an intersupt to the processor. Go at least one of the low contoo lines, called a                                                                                             |      |        |   |

Program: It consists of 2 routines. COMPUTE - produces a set a n lines. PRINT - send lines of output to printer a time. without interesp to COMPUTE produces n lines. PRINT sends Istline (wait for it to be printed) send and line (wait for it to be printed) so send nothline (wait for it to be priviled) COMPUTE produces next n lines. PRINT sends 18t line (wait) send and ene. (wait) send nthere wait (wait) go on. isadvantage - Processor spends a considerable time waiting for pointer to become ready.

with interrupte Overlapping printing and computation i.e., execute COMPUTE vontine unile printing is in COMPUTE produces n lines PRINT send lot line (suspend PRINT) COMPUTE next in lines, printer printing If printer ready, send ISh. COMPUTE interrupted. PRINT send and line . (Suspend print) COMPUTE next in lines, printer printing So on Program 1 Program 2 COMPUTE routine PRINT routine 2 Transfer of control through the use of interrupts