## 2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8=50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

## Seventh Semester B.E. Degree Examination, May/June 2010 **VLSI Circuits and Design**

Time: 3 hrs.

Max. Marks: 100

Note: Answer any FIVE full questions, selecting at least TWO questions from each part.

## PART - A

Bring out the salient features of fabrication of P-well CMOS inverter. 1 a.

(08 Marks)

What are the differences between CMOS and bipolar technology? b.

(04 Marks)

Derive an expression for Ids in non-saturated region of MOS device.

(08 Marks)

- Show that pull up-to-pull down ratio for nMOS inverter driven through one or more pass 2 a. transistor, is  $\frac{Z_{\text{pu}2}}{Z_{\text{pd}2}} = 8:1$ . (08 Marks)

- Explain the working of Bi-CMOS inverter with and without static current flow.

(06 Marks)

With a circuit, explain two different forms of pull up for inverter.

(06 Marks)

Discuss the latch up in CMOS with p-well or n-well structure. 3 a.

(06 Marks)

Bring out  $\lambda$  based nMOS design rules, with examples.

(06 Marks)

- Bring out micron rules for CMOS with examples, giving the difference between buried and butting contact. (08 Marks)

- 4 What is sheet resistance? Calculate sheet resistance of transistor channel if  $L = 8\lambda$ ,  $W = 2\lambda$ if n transistor channel  $R_s = 10^4 \Omega/\text{square}$ . (04 Marks)

- Derive an expression for rise time and fall time of CMOS inverter.

(06 Marks)

For cascaded inverters as drivers for large capacitive loads, show that minimum delay for given  $y = C_L / \Box C_g = f^N$ , if f = e, where f is the width of the inverter, N is number of stages. What are super buffer buffers? Explain. (10 Marks)

## PART - B

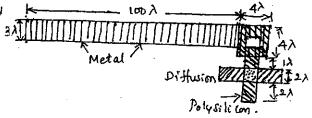

- Calculate the area capacitance for the following structure if relative capacitances are,

- Metal 1 to substrate  $0.075 \times 10^{-4} \, pF/\mu m^2$ . ii) Polysilicon to substrate  $0.1 \times 10^{-4} \, pF/\mu m^2$

- iii) Gate to channel  $1 \, pF \times 10^{-4} \, pF/\mu m^2$ .

(07 Marks)

Fig. Q5 (a)

- For combined voltage and electric field scaling, find scaling factors in terms of  $\alpha$ ,  $\beta$  for the following parameters: i) Gate capacitance ii) Maximum operating frequency fo

- iii) Saturation current I<sub>dss</sub> iv) Switching energy per gate E<sub>g</sub>.

Discuss limitations of scaling for interconnect and contact resistance.

(08 Marks) (05 Marks)

- 6 a. For a combined voltage and electric field scaling, show that the scaling factor for effective voltage Va is  $(m+\beta)/\beta(m+1)$  where m is a real number. (06 Marks)

- b. What are the guidelines for a subsystem design process? Bring out the merits and demerits between pass transistor and transmission gate. (08 Marks)

- c. What are the limitations of sub-threshold current scaling and current density? (06 Marks)

- 7 a. Why NOR gate structure is preferred to NAND for nMOS? Derive an expression for  $Z_{pu}/Z_{pd}$  ratio for NAND and NOR gate. (06 Marks)

- b. Explain the pseudo nMOS and CMOS domino logic showing the difference between the two. (08 Marks)

- c. Give the structured design of bus arbitration logic for n-line bus. (06 Marks)

- 8 a. Discuss the current limitations for VDD and GND rails.

(04 Marks)

b. For 4 bit arithmetic processor, explain any two architectures.

(06 Marks)

c. Give the regular design of an adder cell and show how arithmetic and logical functions are implemented using adder cell. (10 Marks)

\* \* \* \* \*