## VLSI Circuits & Design

Max. Marks: 100

Note: Answer FIVE full questions, selecting at least TWO questions from each part.

PART - A

1 a. Explain the nMOS fabrication process with neat diagram.

b. Discuss Moore's law, with graph.

c. Compare the characteristics of cMOS and bipolar technologies.

(02 Marks) (08 Marks)

2 a. Define  $Z_{p,u}$  and  $Z_{p,d}$ . Show that pull up to pull down ratio for nMOS inverter driven through

one or more pass transistor, is  $\frac{Z_{pu2}}{Z_{pd2}} = 8:1$ .

(10 Marks)

(10 Marks)

b. Explain the latch-up phenomena in cMOS circuits.

c. With neat diagrams, explain the merits and demerits of BiCMOS inverter configurations.

(05 Marks)

3 a. Draw the stick diagram and layout for an nMOS two way selector, with enable input.

b. Define stick diagram. Explain the encodings used for a simple nMOS process. (06 Marks) (06 Marks)

- c. With relevant diagrams, explain the Lambda based design rules as applicable to p-well cMOS process. (08 Marks)

- 4 a. What is silicide? Discuss the advantages and disadvantages of using it inplace of polysilicon.

(06 Marks)

- b. What is sheet resistance? Calculate sheet resistance of transistor channel if  $L = 8\lambda$ ,  $W = 2\lambda$ , if n transistor channel  $R_S = 10^4 \Omega$  / square. (06 Marks)

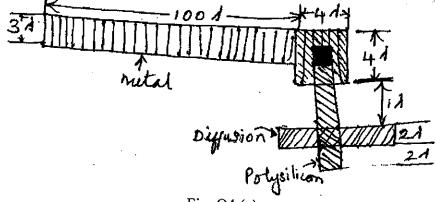

- c. Calculate the area capacitance for the following structure if relative capacitances are:

- i) Metal 1 to substrate  $0.0754 \times 10^{-4}$  pF/ $\mu$ m<sup>2</sup>.

ii) Polysilicon to substrate  $0.1 \times 10^{-4} \text{ pF/}\mu\text{m}^2$

iii) Gate to channel 1×10<sup>-4</sup> pF/μm<sup>2</sup>.

(08 Marks)

Fig. Q4 (c)

PART - B

| 5 |    | List the scaling factors for device parameters.  Discuss limitations of scaling for interconnect and contact resistance.    | (14 Marks)<br>(06 Marks) |

|---|----|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 6 | a. | What are the guidelines for a subsystem design process? Bring out the merits between pass transistor and transmission gate. | and demerits (08 Marks)  |

b. Write the structure and stick diagram of cMOS, BicMOS two input NOR gate. (08 Marks)

c. Explain in detail pseudo-nMOS logic.

(04 Marks)

7 a. Explain the operation of  $4 \times 4$  cross bar switch with a neat diagram.

(10 Marks)

b. Explain the design of an ALU subsystem.

(10 Marks)

Write short notes on:

a. Super buffers.

b. Basic bus architéctures.

c. Two phase clock generator using 'D' flip-flops.

d. Dynamic register élement.

(20 Marks)

CMRIT LIBRARY

BANGALORE - 560 037