CMR INSTITUTE OF TECHNOLOGY

## Internal Assesment Test - II

| Sub:                           | OPERATIONAL AMPLIFIERS AND LINEAR ICS Cod                                                                                  |           |         |               |    | de:  | 15EE46 |            |        |        |        |         |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------|---------|---------------|----|------|--------|------------|--------|--------|--------|---------|

| Date:                          | 10 / 05/ 2017                                                                                                              | Duration: | 90 mins | Max<br>Marks: | 50 | Sem: | IV     | Branch: EH |        |        | EE     |         |

| Answer Any FIVE FULL Questions |                                                                                                                            |           |         |               |    |      |        |            |        |        |        |         |

|                                |                                                                                                                            |           |         |               |    |      |        |            | Mark   | S      | СО     | RB<br>T |

|                                | Using an Opamp uA7                                                                                                         | _         | _       | _             | _  | _    |        |            | [10]   | j c    | C406.5 |         |

|                                | $V_{o(p-p)}$ =6V and frequency 1Khz with ±15V supply. Modify the circuit to provide duty cycle adjustment from 20% to 80%. |           |         |               |    |      | iac    |            |        |        |        |         |

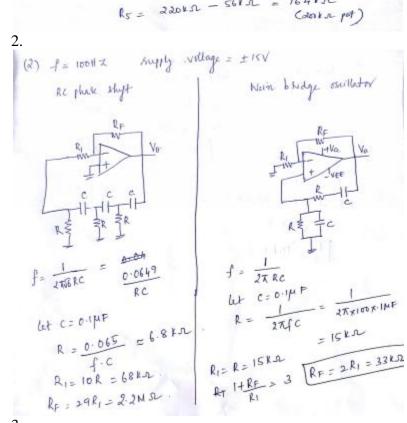

| _                              | Design a RC phase shift oscillator and Wein bridge oscillator to generate a                                                |           |         |               |    |      |        | [10]       | ] [    | C406.5 | L2     |         |

|                                | sinusoidal output of 100Hz and supply voltage ±15V using any bipolar Opamp.                                                |           |         |               |    |      |        |            |        |        |        |         |

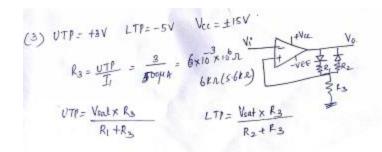

| l                              | 3 Design a non inverting Schmitt trigger to have UTP=+3V and LTP=-5V using an                                              |           |         |               |    |      | g an   | [10]       | ]  C   | C406.4 | L3     |         |

|                                | Op-amp uA741 IC with supply voltage Vcc=±15V.                                                                              |           |         |               |    |      |        |            |        |        |        |         |

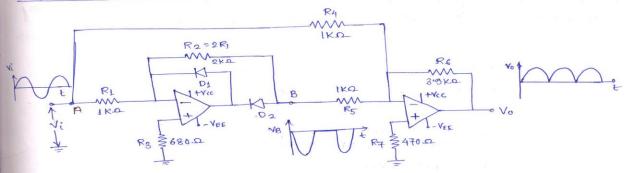

| 4                              | Explain the circuit of a full wave precision rectifier using a half wave rectifier an                                      |           |         |               |    |      | r and  | [10]       | ]  C   | C406.3 | L2     |         |

| 9                              | summing circuit .Demonstrate the input and output waveforms.                                                               |           |         |               |    |      |        |            |        |        |        |         |

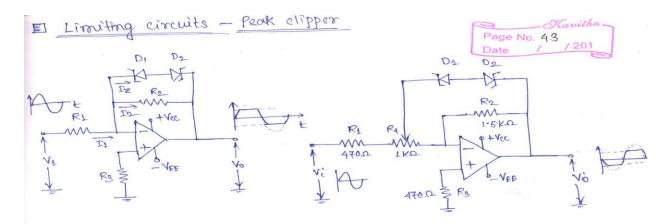

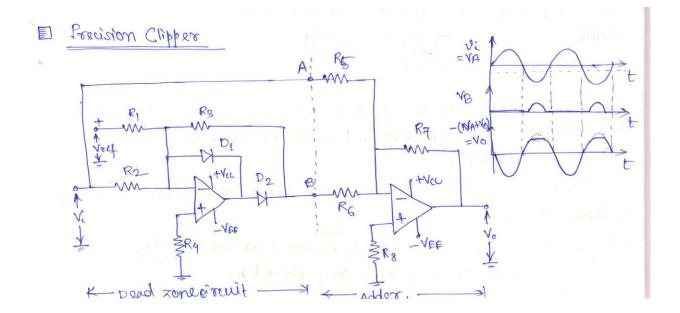

| 5                              | Demonstrate the operation of peak clipper using Zener diodes and Precision                                                 |           |         |               |    |      | [10]   | j C        | C406.3 | L2     |        |         |

|                                | clipper using dead zone circuit with necessary waveforms.                                                                  |           |         |               |    |      |        |            |        |        |        |         |

| 6                              | Discuss the operation of weighted resistor DAC and R-2R ladder DAC with                                                    |           |         |               |    |      |        | [10]       | j C    | C406.6 | L2     |         |

| circuit diagram.               |                                                                                                                            |           |         |               |    |      |        |            |        |        |        |         |

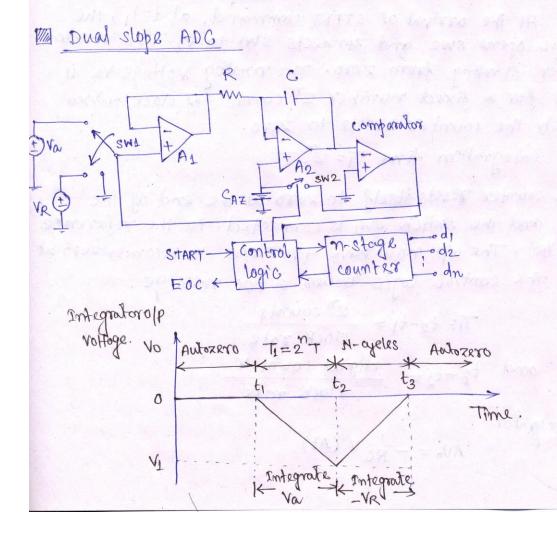

| 7                              | Discuss the operation of successive approximation ADC and dual slope ADC                                                   |           |         |               |    |      |        | [10]       | j C    | C406.6 | L2     |         |

|                                | with circuit diagram                                                                                                       |           |         |               |    |      |        |            |        |        |        |         |

$$3 = \frac{14 \times 5.61 \times 1}{R_1 + 5.61 \times 1}$$

$$3(R_1 + 5.61 \times 1) = \frac{14 \times 6.61 \times 1}{3R_1 + 16.88 \times 1} = \frac{14 \times 6.61 \times 1}{3R_1 + 16.88 \times 1}$$

$$3R_1 + \frac{16.88 \times 1}{R_1 = 61.66 \times 1}$$

$$R_1 = \frac{201 \times (184 \times 1)}{R_1 = 201 \times (184 \times 1)}$$

$$5R_1 = \frac{201 \times (184 \times 1)}{R_2 = 108 \times 1}$$

$$5R_2 = \frac{50.9}{R_2}$$

$$R_2 = \frac{1081}{R_2}$$

Half-ware Rectifier and summing circuit

the above essent is a combination of half-wave rectifier with gain = 2 and an investing adder with gain = 3.9

owning the half-cycle

voltage at terminal A = +Vi while that at terminal B is -2Vi. I produce D, is off and Dz is on ]

A4 College Book

During the origin of the ensuming around, with 14 = 12

$$V_0 = -\frac{R_6}{R_4} \left( V_P + V_P \right)$$

$$= -\frac{R_6}{R_4} \left( V_i - 2V_i \right)$$

$$= -\frac{R_6}{R_4} \left( -V_i \right) = \frac{R_6}{R_4} V_i$$

Ourring -ve half-cycle

$V_A = -V_i$   $V_B = 0$  as D<sub>i</sub> is on and D<sub>2</sub> is off.

consequently the output is.

$$V_0 = -\frac{R_6}{R_4} (V_B + V_B) = -\frac{R_6}{R_4} (-V_i + 0)$$

5.

Back to back zener dioder are used to clip-off the peaks of the output voltage waveform. One diode is forward braned and the other diode is in reverse breakdown region when the output voltage is greate than  $(V_F + V_Z)$ . So, the output voltage cann't exceed  $\pm (V_F + V_Z)$ . As larg as the output voltage is less than this limit, the circuit behaves as inverting amplifier, unaffected by the diodes.

The second circuit is a modification of the first circuit where a resistor Rq is connected in series with R1. Using Rq we can change the limiting voltage.

suppose  $R_1=R_4=R_2$  and  $(V_Z+V_F)=4V$ . With moving the contact of the right side of  $R_4$ ,

With reaving the contact at the left of Rq,  $VR4 = VZ + VF = \pm 4V$

with  $R_2=R_4$ ,  $V_{R2} \neq V_{R4}=\pm 2V$ Givery,  $V_0(max)=\pm 2V=V_{R2}$

This means, by moving the contact the limiting voltage can be changed between ±2 to ±4 volt.

when  $R_4 = R_2$ , the voltage gain of the circuit, =  $-\frac{R_2}{R_1 + R_4}$  until the output limit is reached.

Use: To protect devices that might damage by excessive voltage.

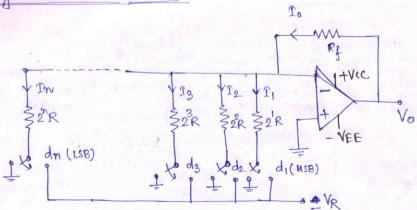

Wa Weighted Resistor DAC

The above circuit uses a summing amplifier with binary weighted resister network. It has n-electronic switches di, d2, ----dn controlled by binary input word. These switches are single pole double through (SPT) type. The reference voltage is (-VR).

If, binary input is 'zero', the switch connects the resistor to the ground. If Up is 1' the switch is connected to -VR.

Applying KCL at the morning terminal we get,

$$T_{0} = \Gamma_{1} + \Gamma_{2} + \Gamma_{3} + \cdots + \Gamma_{N}$$

$$= \frac{V_{R}}{2R} \cdot d_{1} + \frac{V_{R}}{2^{2}R} d_{2} + \cdots + \frac{V_{R}}{2^{n}R} d_{n}$$

or,  $\frac{V_{0}}{R_{f}} = \frac{V_{R}}{R} \left( \frac{d_{1}}{2} + \frac{d_{2}}{2^{2}} + \cdots + \frac{d_{N}}{2^{n}} \right)$

or,  $V_{0} = V_{R} \cdot \frac{R_{f}}{R} \left( d_{1} \cdot 2^{\frac{1}{4}} d_{2} \cdot 2^{\frac{2}{4}} + \cdots + \frac{2^{n}}{2^{n}} d_{n} \right)$

comparing the above equation with the general expression of DAC we get,

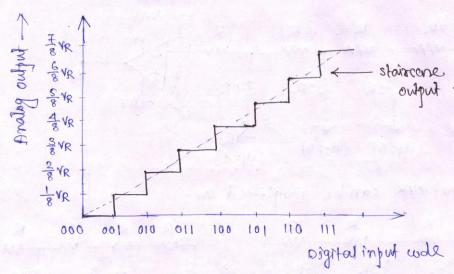

VR=VFS, K=  $\frac{RF}{R}$ If, Rg=R then, K=1, Full scale voltage (VFS)=VR. Vo = VR (d1.2+d2.2+---+dn2<sup>n</sup>) The transfer characteristics of a 3-bit DAC is-

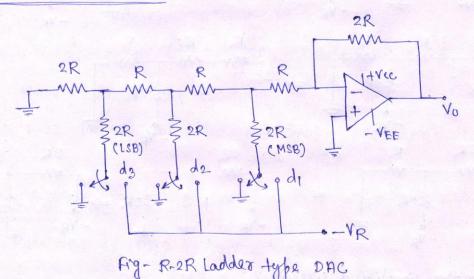

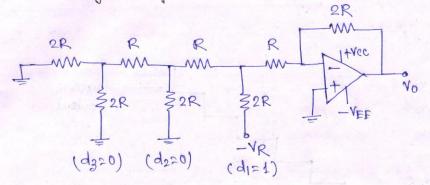

## Z R-2R Lodder DAC

The range for R is 2.5 KD to 10 KD.

For simplicity, consider a 3-bit DAC. where the didads. corresponds to the binary word input to the DAC.

-VR is the reference voltage.

The feedback resistance is 2R. The network consist of R-2R network connected with the op-amp.

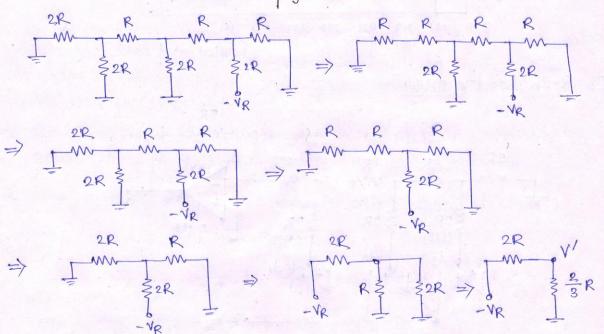

consider the digital imput didada = 100. The execut becomes:

The R-2R network can be simplified on-

From the simplified circuit,

$$V' = \frac{-V_R \cdot \frac{2}{3}R}{2R + \frac{2}{3}R} = -V_R \cdot \frac{\frac{2}{3}R}{\frac{8}{3}R} = -\frac{V_R}{4}$$

we can represent the circuit or -

Applying KCL at the inverting terminal

$$\frac{V_0}{2R} = \frac{-V'}{R}$$

or,  $\frac{V_0}{2R} = \frac{V_R}{4R}$  or,  $\frac{V_0}{2R} = \frac{V_R}{4R}$

$$\frac{V_0}{2R} = \frac{-V}{R}$$

or,

$$\frac{V_0}{2R} = \frac{V_R}{4R}$$

or,

$$V_0 = \frac{V_R}{2}$$

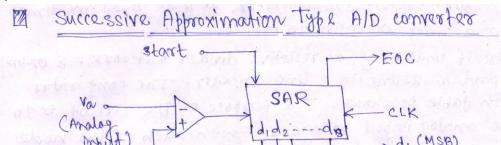

Functional diagram of the successive approximation ADG.

>d8 (LSB)

The conversion sequence for a typical analog input is shown below.

DAG

| correct digital representation | successive approximation resistor output vd at different stages in conversion | comparator |

|--------------------------------|-------------------------------------------------------------------------------|------------|

| 11010100                       | 10000000                                                                      | 1 - V      |

| 11010100                       | 11000000                                                                      | 1          |

|                                | 11100000                                                                      | 0          |

| ent about                      |                                                                               |            |

| is deviled of sight            |                                                                               | 0          |

| obs all ( The width            |                                                                               | 1          |

|                                | 11010110                                                                      | 0          |

|                                | 11010101                                                                      | 0          |

| Secret Roll Park Lo            | 11010100                                                                      |            |

For successive expressionation type ADe, for n-bit conversion such n-clock pulses are required. An eight bit converter would require eight clock pulses to obtain a digital output. The circuit uses a successive approximation resistor (SAR) to find the required value of each bit by total & error.

With the ontival of start command, the SAR sets MSB (d1) = 1 with all other bits to zero, so that the total code is 10000000 The output Vd of the DAC is now compared with analog input Va. If Va is greater than the DAC output Vd, then, 10000000 is less than the correct representation of the analog input. The MSB is left at '1' and the next lower significant bit is made '1' and further tested.

However if va is less than the DAC output then 10000000 is greater than the correct digital representation 30, reset MSB to '0' and next bit is set to'1' and further tested.

After eight cycles, the EOC command is released and the output of SAR gives the correct digital representation of the

The circuit consists of a high input impedance buffer 111, precision integrator A2 and a voltage comparator. The converter first integrates the analog input signal va for a sixed duration of 2<sup>m</sup> clock period. Then it integrates an integrator output is zero. The number N of clock cycles required to return the integrator to zero is proportional to the value of va averaged over the integration period.

to GND and sw2 is closed. Any offset voltage present the A1, A2 comparator Loop after integration, oppears across the copacitor CAZ HII the threshold of the comparator is achieved.

At the arrival of START command, at t=t1, the control logic opens swe and connects swi to va and enables the counter starting from zero. The randog voltage va b integrated for a fixed number 2<sup>m</sup> counts of clock pulses after which the counter resets to zero.

Integration time Ti= 2n. T

The counter resets itself to zero at the end of the interval To and the switch swi is connected to the reference voltage (-VR). The old now have the slape. Vo becomes zero at tets and the control logic issues a foc message.