# CMRIT Library CBCS Scheme

USN SOUSHIE

16/17EVE12

# First Semester M.Tech. Degree Examination, Dec.2017/Jan.2018 Digital VLSI Design

CALRETT LILLIANS

Time: 3 hrs.

Max. Marks: 80

Note: Answer FIVE full questions, choosing one full question from each module.

## Module-1

- a. Derive the MOSFET current equation in different regions of operation and plot the current voltage characteristics of an n-channel MOSFET. (08 Marks)

- What is MOSFET scaling? Explain in brief the types of scaling indicating the effect of scaling on derive characteristics. (08 Marks)

#### OR

- Explain the working of resistance load inverter with necessary circuit diagram and voltage transfer characteristic. Also device the equations for V<sub>OL</sub>, V<sub>OH</sub>, V<sub>IL</sub> and V<sub>IH</sub>. (08 Marks)

- b. Calculate the critical voltage V<sub>OL</sub>, V<sub>OH</sub>, V<sub>IL</sub> and V<sub>IH</sub> and find the noise margins of the depletion load inverter circuit with the following parameter:

$$V_{DD} = 5V$$

,  $V_{TO}(driver) = 1.0V$ ,  $V_{TO(load)} = -3.0V$ ,  $\left(\frac{W}{L}\right)_{Driver} = 2$ ,  $\left(\frac{W}{L}\right)_{Load} = \frac{1}{3}$ ,

$$K_{n(driver)} = k_{n(load)} = 25\mu A/V^2 \gamma = 0.4 V^{\frac{1}{2}}, \ \phi_F = -0.3V$$

(08 Marks)

### Module-2

- a. Draw the circuit of a CMOS inverter and derive the switching threshold (Vth) equation for the same. (06 Marks)

- b. Define propagation delay time and obtain the equations for τ<sub>PHD</sub> and τ<sub>PLH</sub> for CMOS inverter.

CMRIT Liberary

#### OR

- Derive an equation for switching power dissipation of CMOS inverter with necessary circuit diagram and waveforms.

- How to measure the propagation delay of an inverter using ring oscillator? Explain with necessary diagrams and equations.

- With suitable circuit diagrams and equations, explain RC delay model to calculate the interconnect delay.

#### Module-3

- a. With necessary circuit diagrams, explain the following dynamic RAM cells. 4T DRAM, 3T DRAM, 2T DRAM and IT DRAM.

(10 Marks)

- Explain 4bit ×4bit NAND based ROM array with necessary diagrams.

(06 Marks)

機能ない。 ひこく からぬをかき

OR

Briefly explain memory structure of SRAM with read and write circuitry with the help of read and write timing diagrams.

Draw the schematic of flash memory cell and explain.

(06 Marks)

Module-4

With necessary circuit diagram explain enhancement load based rationed, 3bit dynamic shift 7 (08 Marks) register.

b. Discuss the working principle of NORA CMOS logic and zipper CMOS logic with (08 Marks) necessary diagrams.

- What is BiCOMS logic? With neat circuit diagram explain the working of BiCMOS inverter? Also mention the advantages and disadvantages of BiCMOS. (10 Marks)

- b. Draw the BiCMOS circuit for the function  $Y \ni \overline{A(B+C)}$ .

(04 Marks)

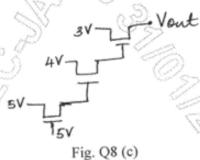

Calculate the value of Vout in the circuit shown in Fig. Q8(c), if threshold voltage of pass (02 Marks) transistor is 0.7V.

Module-5

With relevant circuit diagram and symbolic representation, explain two types of input 9 (08 Marks) circuits.

Explain on-chip clock generation and clock distribution with necessary diagrams. (08 Marks)

a. What is latch up in CMOS? Explain with necessary diagrams and equations? Also discuss 10 (10 Marks) guidelines for avoiding latch up. (06 Marks)

Describe performance modeling procedure with a model.

BANGALORE - SGO 037