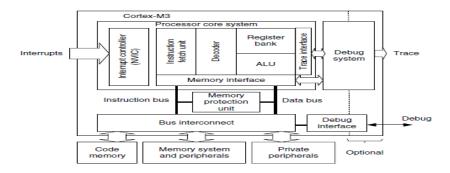

# 1. Describe with neat diagram, the architecture of Cortex M3 Processor.

Ans. The ARM Cortex<sup>TM</sup>-M3 processor, the first of the Cortex generation of processors released by ARM in 2006, Cortex M3 is a ,\$Small,\$Low power,\$Rich interfaces,\$Minimum 3 stage pipeline \$Harvard Architecture.Multiple core buses capable of simultaneous accesses.Tightly integrated interrupt controller with Wake-up Interrupt Controller Interruptible/continuable multiple load and store instructions Supports MPU. 18 x 32-bit registers, Excellent compiler target, Reduced pin count requirements, Efficient interrupt handling, Power management, Efficient debug and development support features, Breakpoints, Watchpoints, Flash Patch support, Instruction Trace Strong OS support User/Supervisor model OS support features Designed to be fully programmed in C (even reset, interrupts and exceptions), ARMv7M Architecture No Cache - No MMU, Debug is optimized for microcontroller applications, Vector table contains addresses, not instructions, DIV instruction, Interrupts automatically save/restore state, Exceptions programmed in C (No Coprocessor 15 - All registers are memory-mapped), Interrupt controller is part of Cortex-M3 macrocell, Fixed memory map, Bit-banding, Non-Maskable Interrupt (NMI), Only one processor status reg, Thumb-2 processing core, Mix of 16 and 32 bit instructions for very high code density, Gives complete Thumb compatibility.

#### 2. Write short notes on Exceptions, Interrupts and Vector Table.

Ans. The Cortex-M3 supports a number of exceptions, including a fixed number of system exceptions and a number of interrupts, commonly called IRQ. The number of interrupt inputs on a Cortex-M3 microcontroller depends on the individual design. Interrupts generated by peripherals, except System Tick Timer, are also connected to the interrupt input signals. The typical number of interrupt inputs is 16 or 32. However, you might find some microcontroller designs with more (or fewer) interrupt inputs. The vector table is an array of word data inside the system memory, each representing the starting address of one exception type.

| economico.          |                |              |                                                                                                                                                          |  |  |  |  |  |  |

|---------------------|----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Exception<br>Number | Exception Type | Priority     | Function                                                                                                                                                 |  |  |  |  |  |  |

| 1                   | Reset          | -3 (Highest) | Reset                                                                                                                                                    |  |  |  |  |  |  |

| 2                   | NMI            | -2           | Nonmaskable interrupt                                                                                                                                    |  |  |  |  |  |  |

| 3                   | Hard fault     | -1           | All classes of fault, when the corresponding fault<br>handler cannot be activated because it is currently<br>disabled or masked by exception masking     |  |  |  |  |  |  |

| 4                   | MemManage      | Settable     | Memory management fault; caused by MPU<br>violation or invalid accesses (such as an instruction<br>fetch from a nonexecutable region)                    |  |  |  |  |  |  |

| 5                   | Bus fault      | Settable     | Error response received from the bus system;<br>caused by an instruction prefetch abort or data<br>access error                                          |  |  |  |  |  |  |

| 6                   | Usage fault    | Settable     | Usage fault; typical causes are invalid instructions<br>or invalid state transition attempts (such as trying to<br>switch to ARM state in the Cortex-M3) |  |  |  |  |  |  |

| 7-10                | _              | _            | Reserved                                                                                                                                                 |  |  |  |  |  |  |

| 11                  | SVC            | Settable     | Supervisor call via SVC instruction                                                                                                                      |  |  |  |  |  |  |

| 12                  | Debug monitor  | Settable     | Debug monitor                                                                                                                                            |  |  |  |  |  |  |

| 13                  | _              | _            | Reserved                                                                                                                                                 |  |  |  |  |  |  |

| 14                  | PendSV         | Settable     | Pendable request for system service                                                                                                                      |  |  |  |  |  |  |

| 15                  | SYSTICK        | Settable     | System tick timer                                                                                                                                        |  |  |  |  |  |  |

| 16-255              | IRQ            | Settable     | IRQ input #0-239                                                                                                                                         |  |  |  |  |  |  |

| Table 3.5 Vector Table D | Table 3.5 Vector Table Definition after Reset |                           |  |  |  |  |  |  |  |  |

|--------------------------|-----------------------------------------------|---------------------------|--|--|--|--|--|--|--|--|

| Exception Type           | Address Offset                                | Exception Vector          |  |  |  |  |  |  |  |  |

| 18-255                   | 0x48-0x3FF                                    | IRQ #2-239                |  |  |  |  |  |  |  |  |

| 17                       | 0x44                                          | IRQ #1                    |  |  |  |  |  |  |  |  |

| 16                       | 0x40                                          | IRQ #0                    |  |  |  |  |  |  |  |  |

| 15                       | 0x3C                                          | SYSTICK                   |  |  |  |  |  |  |  |  |

| 14                       | 0x38                                          | PendSV                    |  |  |  |  |  |  |  |  |

| 13                       | 0x34                                          | Reserved                  |  |  |  |  |  |  |  |  |

| 12                       | 0x30                                          | Debug monitor             |  |  |  |  |  |  |  |  |

| 11                       | 0x2C                                          | SVC                       |  |  |  |  |  |  |  |  |

| 7-10                     | 0x1C-0x28                                     | Reserved                  |  |  |  |  |  |  |  |  |

| 6                        | 0x18                                          | Usage fault               |  |  |  |  |  |  |  |  |

| 5                        | 0x14                                          | Bus fault                 |  |  |  |  |  |  |  |  |

| 4                        | 0x10                                          | MemManage fault           |  |  |  |  |  |  |  |  |

| 3                        | 0x0C                                          | Hard fault                |  |  |  |  |  |  |  |  |

| 2                        | 0x08                                          | NMI                       |  |  |  |  |  |  |  |  |

| 1                        | 0x04                                          | Reset                     |  |  |  |  |  |  |  |  |

| 0                        | 0x00                                          | Starting value of the MSP |  |  |  |  |  |  |  |  |

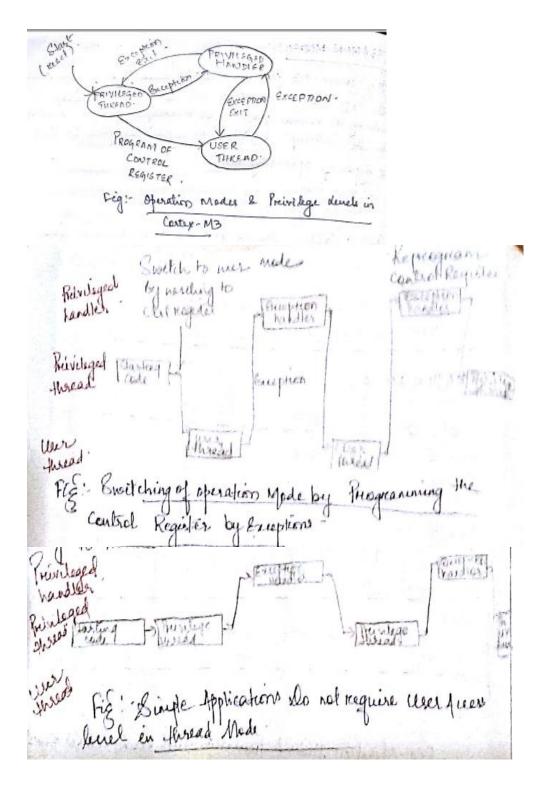

3a. Explain the operating modes of Cortex M3 with the help of neat diagrams indicating the switching of states on the occurrence of exceptions.

```

-> The Contex. M3 processor has a mades & & privilege levels

1> The operation mades determine whether the processor is

kunning a normal prosperan ar kunning an exceptions handler but an interrupt handler or system exceptions handler.

13 2 types of operating modes.

(a) Thread mode

(10 Standler mide.

> The previlege levels provide a mechanism for

Safeguarding memory access to excitical negions as well

as frainding a basic security land model.

1> 2 types of privilege level:

(a) Prievilegedlevel

(b) elver level.

is when the processor is running a main program

(threead mode), it can be either in a preivileged

state or a ever state , but exception handlers can

ranky be in a privileged state.

to When the processor exit reset, it is in thread

made with privileged access reights.

In privileged state, a program has access to all instructions.

by Software in the privileged occess levels can switch the fragram into the user access level using the control

register

```

b. List the applications of Cortex M3.

Low-cost microcontrollers: The Cortex-M3 processor is ideally suited for low-cost microcontrollers, which are commonly used in consumer products, from toys to electrical appliances. It is a highly competitive market due to the many well-known 8-bit and 16-bit microcontroller products on the market. Its lower power, high performance, and ease-of-use advantages enable embedded developers to migrate to 32-bit systems and develop products with the ARM architecture.

Automotive: Another ideal application for the Cortex-M3 processor is in the automotive industry. The Cortex-M3 processor has very high-performance efficiency and low interrupt latency, allowing it to be used in real-time systems. The Cortex-M3 processor supports up to 240 external vectored interrupts, with a built-in interrupt controller with nested interrupt supports and an optional MPU, making it ideal for highly integrated and cost-sensitive automotive applications.

Data communications: The processor's low power and high efficiency, coupled with instructions in Thumb-2 for bit-field manipulation, make the Cortex-M3 ideal for many communications applications, such as Bluetooth and ZigBee.

Industrial control: In industrial control applications, simplicity, fast response, and reliability are key factors. Again, the Cortex-M3 processor's interrupt feature, low interrupt latency, and enhanced fault-handling features make it a strong candidate in this area.

Consumer products: In many consumer products, a high-performance microprocessor (or several of them) is used. The Cortex-M3 processor, being a small processor, is highly efficient and low in power and supports an MPU enabling complex software to execute while providing robust memory protection.

#### 4a Explain the Program Status registers with bit pattern.

I The Pere are divided into 3 status registers.

- · Application PSR -

- · Palinapt PSR.

The 3 PSRs can be accessed together / separatchy using the special register access instructions MSR & MRS. When they are accessed de a scalletime term, the name alpsk & used.

We can read the PSRs using the MRS instruction and An also change the APSR using the MSR instruction, but EPSR 2 TPSR are read-only. For eg:

MRS RO, APSR; Read flag state into RO.

MRI RO, IPSR; Read exception | Theorempt state

MRI RO, EPSR; Read Execution State

MCR APSR, Ro; While flag State.

| AFE N | 2 | - | 1 |   |     |   |  |     |    |      | -    | -   | -      |

|-------|---|---|---|---|-----|---|--|-----|----|------|------|-----|--------|

| 1     |   | C | ٧ | Q |     |   |  |     |    |      |      |     |        |

| 231   |   |   |   |   | ,   |   |  |     | 64 | cep. | 1100 | W É | 3 E C. |

| ens.  |   | + | * |   | 101 | 1 |  | 707 |    |      |      | +   | 1      |

Fig: PSRs in Coretex - M3.

| 3) 30 27 28 | 21 | 16:24 | 220 | 15:30 W.10 | ICLO. | -  | -     |     | L . I | 1 0   |

|-------------|----|-------|-----|------------|-------|----|-------|-----|-------|-------|

| 31 30       | 0  | 15634 | 1   |            | 15.70 |    |       |     |       | 14 0  |

| BENZCV      | 14 | TT    | 1   |            | TET   | Ex | ce.pi | ien | Aleur | bes . |

Fig - Combunid XPSR is Coetex-M3.

Is In ARM assembler, while accessing xPSR (all three PSRs as and), the Symbol PSR is used!

MRS NO, PSR; Read the combined foregram.

MSR PSR, 100; Write the combined frequences

Description of the but fields:

Q > Sticky Saturation Hag.

III / IT > Interrupt - Continuable Instruction bits,

1> Thumb State, always 1; treying to clear this but will cause a fault exception.

Bueption number - Indicates which exception the fromsor is handling.

- \* The Carry flag is used for emigred addition /

- # The Overflow flag is used for signed adolltion /

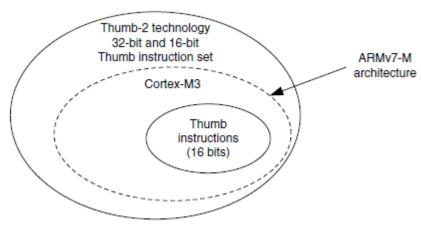

## 4b Explain Thumb2 technology.

The Thumb-2³ technology extended the Thumb Instruction Set Architecture (ISA) into a highly efficient and powerful instruction set that delivers significant benefits in terms of ease of use, code size, and performance (see Figure 1.4). The extended instruction set in Thumb-2 is a superset of the previous 16-bit Thumb instruction set, with additional 16-bit instructions alongside 32-bit instructions. It allows more complex operations to be carried out in the Thumb state, thus allowing higher efficiency by reducing the number of states switching between ARM state and Thumb state.

Focused on small memory system devices such as microcontrollers and reducing the size of the processor, the Cortex-M3 supports only the Thumb-2 (and traditional Thumb) instruction set. Instead of using ARM instructions for some operations, as in traditional ARM processors, it uses the Thumb-2 instruction set for all operations. As a result, the Cortex-M3 processor is not backward compatible with traditional

ARM processors. That is, you cannot run a binary image for ARM7 processors on the Cortex-M3 processor. Nevertheless, the Cortex-M3 processor can execute almost all the 16-bit Thumb instructions, including all 16-bit Thumb instructions supported on ARM7 family processors, making application porting easy.

With support for both 16-bit and 32-bit instructions in the Thumb-2 instruction set, there is no need to switch the processor between Thumb state (16-bit instructions) and ARM state (32-bit instructions). For example, in ARM7 or ARM9 family processors, you might need to switch to ARM state if you want to carry out complex calculations or a large number of conditional operations and good performance is needed, whereas in the Cortex-M3 processor, you can mix 32-bit instructions with 16-bit instructions without switching state, getting high code density and high performance with no extra complexity.

The Thumb-2 instruction set is a very important feature of the ARMv7 architecture. Compared with the instructions supported on ARM7 family processors (ARMv4T architecture), the Cortex-M3 processor instruction set has a large number of new features. For the first time, hardware divide instruction is available on an ARM processor, and a number of multiply instructions are also available on the Cortex-M3 processor to improve data-crunching performance. The Cortex-M3 processor also supports unaligned data accesses, a feature previously available only in high-end processors.

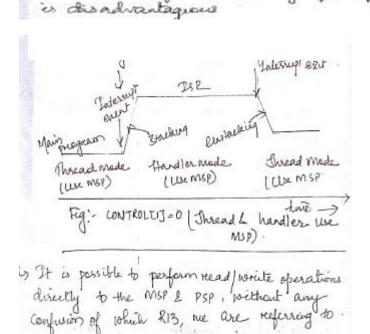

#### 5a Explain the 2-level Stack model in Cortex M3.

In the above assurgement, the main pregram 2 the exception hardless can have deparate stack memory regions which can prevent a stack error in a ever application from Damaging the stack used by the OS-lis When CONTROLTIJ=O, MSP is used for both the I handles made.

In this arrangement, the main frequence & exception hardless share the same Stack memory which is called as default setting after fromer-up and it

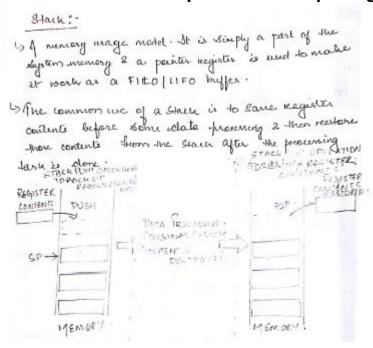

### 5b. What is Stack? Explain the multiple register Stack operation.

Fig: Busic Concept of Stack Memory. Ly Instructions used are DUSH & POP:

Ly ALP Syntam! -

PUSH {RO}; RIB=RIB-4, then Memory [RIB]-[RO].

POP {RO3; Ro= Memory [R13], then R13-R13+4.

is In general black operations are memory write | mead operations well the taddress official by a PP- Date in regulars is somed into stack memory by a PUCH operation I can be restored to regular later by a POP operation.

- to The SP is adjusted automatically in POSH 2 POP SO that multiple data POSH will not cause old stocked data to be exacted.

- is tedow neation are the fixed ALPS describing stack operations in 3 ways:

- (a) For normal uses, for each store (PUSH), there must be a corresponding to read (POP), I the address of the pop operation should notch that of the PUSH-operation for his, the ALP is:

- (b) The PUSH & POP operations can allow multiple load

- to In this case, the ordereing of a negater pop is outon attently neverted by the processor.

b See ALP is:

Main program

; RO. 7, R1-7; RS-2

BL functions. Subneutric 1

functions

possis & RO-R23; Etaze RO, R1, R2 to

; Executing Jack & RO, R1, R2 can

; be changed)

POP & RO-R23; Restore RO, R1, R2

BX LR; Return

; Back to main progress ; Ro= 1, R1= 3, R2-2 ...; near enstructions

ALP Pseudocade! Multiple Register Stack operations

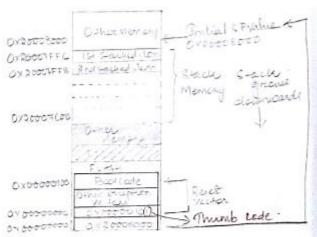

#### 6a. Explain the reset sequence with the help of memory map.

| 6 After the | quexice) -              | a mout, it                  | puil read à nees | À |

|-------------|-------------------------|-----------------------------|------------------|---|

| -kom whe    | evernose?               |                             |                  |   |

| * Address ( | ) x <del>00000000</del> | : Etasteny vo               | July R13 (6P).   |   |

| address of  | pughan 2                | i Kesel Vecto<br>rumtion) : | or [The starms   |   |

| is this yes | تاسلاله ما الم          | alid in th                  | e fellowing      |   |

| shagram     | Felippoola              | Takehirent                  | Instruction      |   |

| Red         | 4. Addus                | 0.0000                      | Tiene            |   |

|             | 14.23.43.<br>Dept. 200  | 11110.                      | Wildhau          |   |

Fig! Reset Segnence

In contex-M3, the initial value for the MSP is fut at the beginning of the memory map fortuned by the vector table which contains vector address value

If The content of the vector table are address values & not branch enstructions, The 1st vector in the vector table is the second piece of data totched by the forcessor after reset

Lifs the Solath operation is contin-M3 is a feel observeding stack (SP decrements before store), the ential SP D'value should be set to the first memory after the lof of the Stack region For eg. - of a stack memory ranges from.

Dx 20007000 to 0x20007FFF(1kg), the initial stack value Should be set to 0x20008000

is The vector table Starts after the onitial St Value.

4) The first vector is the need vector. After the need vector is not fetched, the cortix-M3 can then Start to execute the fragram from the next vector address I begin normal aperation 4. In Cortix, M3, the vector addresses in the vector table should have their dSB set to 1 to endual that they are Thumb cade this is a clustrated in the diagram next.

Tig: - Tritial SP Value & Distrial PC Value Example

1) In the figure, to Indicate the thumb code, the reeset valor individual address became 0x101 whereas the boot rade o'vector address is 0x100.

## 6b. Explain the Control register.

THE CONTROL REGISTER: -Is level to define the frierilige level and the SP Solution

4. This negister has I bite

(2) CONTROLTII: This bit is always 0 in handler made but in hardler made but

- to This but is would be only in thread made & provide ged level. In ever state thander new residing to this bit is not allowed.

- (b) CONTROLTOJ: The bet is breitable only in freveliged. State . One it entre were state, the only went to which back to friends is to trigger an interrupts & change the in exceptionhandler . Summarising both the bits -

& TATUS (FUNCTION)

CONTROLTIJ: Black Status:

J = Alternate Stack is used . 0 : Default (MSP) stack is used if it is in the thread or bore level, the alternate attack is PSP. Sheer is me alternate stack for hardler made pre-this bit was to O when the processes in hardes med.

CONTROLLUI: O = Privileged in Sured mode. 1 = um slate in thread made. If in handler made, the fraction of easter in frivileged level:

To areas this regeter in C:n = - get-control (); It Read the current value of - bet - control () | Set the Control value tox.