| Internal Assesment Test – II   |                           |           |         |            |    |       |        |         |     |

|--------------------------------|---------------------------|-----------|---------|------------|----|-------|--------|---------|-----|

| Sub:                           | LINEAR INTEGRATED CIRCUIT |           |         |            |    | Code: | 15EC46 |         |     |

| Date:                          | 19/ 04 / 2018             | Duration: | 90 mins | Max Marks: | 50 | Sem:  | IV     | Branch: | TCE |

| Answer Any FIVE FULL Questions |                           |           |         |            |    |       |        |         |     |

$\begin{array}{c} \textbf{OBE} \\ \textbf{Marks} \\ \textbf{CO} \quad \textbf{RBT} \end{array}$

Explanation(5 marks)+Frequency Derivation(5 marks)

Explain the working of RC- phase shift oscillator using OPAMP and derive the **[10]** CO4 L4 frequency of oscillation.

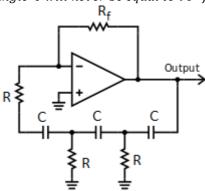

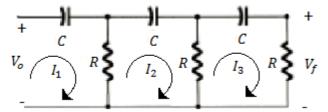

## RC PHASE SHIFT OSCILLATOR:

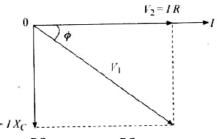

$$A = \frac{V_o}{V_i} = \frac{R}{R + \frac{1}{j\omega C}} = \frac{j\omega RC}{1 + j\omega RC} \ hence \ \theta = \tan^{-1}\left(\frac{\omega RC}{0}\right) - \tan^{-1}\left(\frac{\omega RC}{1}\right)$$

$$=>\theta=\tan^{-1}(\infty)-\tan^{-1}\left(\frac{\omega RC}{1}\right)=>\theta=90^{\circ}-\tan^{-1}(\omega RC)$$

hence when  $\omega=0$  then only we can get  $\theta=90^0$  angle  $\theta$  will never be equal to  $90^0$  for a single RC network

The RC network connected between the amplifier output and input terminal consists of three resistors and capacitors. Resistor  $R_1$  functions as the last resistors in the phase shift network and as the amplifier input resistance. The phase shift network is a phase lead network.

The frequency of the oscillator output depends upon the capacitor and resistor values of the phase shift network.

$$f = \frac{1}{2\pi RC\sqrt{6}}$$

The phase shift network attenuates the amplifier output by a factor 29 i.e.

$$|\beta| = \left| \frac{1}{29} \right|$$

Hence the amplifier must have the voltage gain greater than or equal to 29. If the amplifier gain is less than 29, the circuit will not oscillate. When the gain is substantially greater than 29, the oscillator output waveform is likely to be distorted. A gain just slightly greater than 29 gives a reasonably undistorted sinusoidal waveform.

LOOP1:

$$V_o = I_1 \times \frac{1}{j\omega C} + (I_1 - I_2)R \qquad \qquad = > V_o = I_1 \times \left(\frac{1}{j\omega C} + R\right) - I_2R \qquad --- (1)$$

LOOP2:

$$0 = I_2 \times \frac{1}{j\omega C} + (I_2 - I_3)R + (I_2 - I_1)R \quad => 0 = -I_1R + I_2\left(\frac{1}{j\omega C} + 2R\right) - I_3R \quad --- (2)$$

LOOP3:

$$0 = I_3 \times \frac{1}{j\omega C} + I_3 R + (I_3 - I_2) R => 0 = -I_2 R + I_3 \left(\frac{1}{j\omega C} + 2R\right) - - - (3)$$

$$\left[\left(\frac{1}{i\omega C} + R\right) - R \qquad 0\right]$$

$$\begin{bmatrix} V_o \\ 0 \\ 0 \end{bmatrix} = \begin{bmatrix} \left(\frac{1}{j\omega C} + R\right) & -R & 0 \\ -R & \left(\frac{1}{j\omega C} + 2R\right) & -R \\ 0 & -R & \left(\frac{1}{j\omega C} + 2R\right) \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \\ I_3 \end{bmatrix}$$

By Cramer's Rule:

$$\begin{split} I_{3} &= \frac{\Delta_{3}}{\Delta} \\ \Delta_{3} &= \begin{bmatrix} \left(\frac{1}{j\omega C} + R\right) & -R & V_{o} \\ -R & \left(\frac{1}{j\omega C} + 2R\right) & 0 \\ 0 & -R & 0 \end{bmatrix} = V_{o} \times R^{2} \\ \Delta &= \left(\frac{1}{j\omega C} + R\right) \left\{ \left(\frac{1}{j\omega C} + 2R\right)^{2} - R^{2} \right\} + R \left\{ -R \times \left(\frac{1}{j\omega C} + 2R\right) \right\} \\ \Delta &= \left(\frac{1}{j\omega C} + R\right) \left\{ \frac{1}{j^{2}\omega^{2}C^{2}} + 4R^{2} + \frac{4R}{j\omega C} - R^{2} \right\} + R \left(\frac{-R}{j\omega C} - 2R^{2}\right) \\ \Delta &= \left(\frac{1}{j\omega C} + R\right) \left\{ \frac{1}{j^{2}\omega^{2}C^{2}} + 3R^{2} + \frac{4R}{j\omega C} \right\} + \left(\frac{-R^{2}}{j\omega C} - 2R^{3}\right) \\ \Delta &= \frac{1}{j^{3}\omega^{3}C^{3}} + \frac{3R^{2}}{j\omega C} + \frac{4R}{j^{2}\omega^{2}C^{2}} + \frac{R}{j^{2}\omega^{2}C^{2}} + 3R^{3} + \frac{4R^{2}}{j\omega C} - \frac{R^{2}}{j\omega C} - 2R^{3} \\ \Delta &= \frac{1}{j^{3}\omega^{3}C^{3}} + \frac{6R^{2}}{j\omega C} + \frac{5R}{j^{2}\omega^{2}C^{2}} + R^{3} \\ I_{3} &= \frac{\Delta_{3}}{\Delta} &= \frac{V_{o} \times R^{2}}{\frac{1}{j^{3}\omega^{3}C^{3}} + \frac{6R^{2}}{j\omega C} + \frac{5R}{j^{2}\omega^{2}C^{2}} + R^{3}} = > V_{f} = \frac{V_{o}}{\frac{1}{j^{3}\omega^{3}R^{3}C^{3}} + \frac{6R^{2}}{j\omega^{2}C^{2}} + \frac{5R}{R^{3}}} \\ &= > V_{f} &= \frac{V_{o}}{\frac{1}{j^{3}\omega^{3}R^{3}C^{3}} + \frac{6R^{2}}{j\omega C} + \frac{5R}{j^{2}\omega^{2}C^{2}} + 1} = \frac{V_{o}}{\frac{j}{\omega^{3}R^{3}C^{3}} - \frac{j6}{\omega^{2}R^{2}C^{2}} + 1} \end{aligned}$$

$$=> V_f = \frac{V_o}{\left(1 - \frac{5}{\omega^2 R^2 C^2}\right) + j\left(\frac{1}{\omega^3 R^3 C^3} - \frac{6}{\omega RC}\right)}$$

$$Let \frac{1}{\omega RC} = \alpha \quad hence \quad V_f = \frac{V_o}{(1 - 5\alpha^2) + j(\alpha^3 - 6\alpha)}$$

$$Loop Gain = \beta = \frac{V_f}{V_o} = \frac{1}{(1 - 5\alpha^2) + j(\alpha^3 - 6\alpha)}$$

Loop agin is need hence imaginary part has to be a

Loop gain is real hence imaginary part has to be zero.  $\alpha^3 - 6\alpha = 0 \implies \alpha^3 = 6\alpha = >$

As

$$\alpha = \frac{1}{\omega RC} = \sqrt{6} = \frac{1}{\omega RC} = \omega = \frac{1}{RC\sqrt{6}} = 2\pi f = \frac{1}{RC\sqrt{6}} = f = \frac{1}{2\pi RC\sqrt{6}}$$

$$\beta = \frac{1}{(1 - 5\alpha^2)} = \frac{1}{(1 - 5 \times 6)}$$

$$= -\frac{1}{29} \text{ negative sign indicates that the phase shift is } 180^0$$

$$|\beta| = \left| \frac{1}{29} \right|$$

2

Hence for loop gain to be greater than unity, the gain of the amplifier must be

As the amplifier is the inverting amplifier the gain is

$$A_V = \frac{-R_f}{R_1} \ge 29 => R_f \ge 29R_1$$

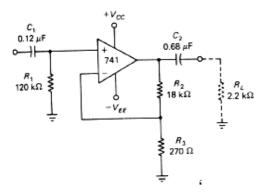

Design a Non-inverting amplifier to be capacitor coupled at input and output. The [10] CO2 load resistor is  $2.2K\Omega$ , lower cut-off frequency is 120Hz. Make necessary modifications to give highest input impedance and determine capacitor values for  $V_i = 15mV \ \ and \ A_V = 66$ .

> General Design (5 marks)+ High impedance circuit

Design (5 marks)

$$I_2 = 100I_{B(max)} = 100 \times 500nA = 50\mu A$$

$$R_3 = \frac{V_{R3}}{I_2} = \frac{V_i}{I_2} = \frac{15mV}{50\mu A} = 300\Omega \approx 270\Omega \text{ (standard register)}$$

$$V_0 = A_V V_i = 66 \times 15 mV = 990 mV$$

$$V_{o} = A_{V}V_{i} = 66 \times 15mV = 990mV$$

$$R_{2} + R_{3} = \frac{V_{o}}{I_{2}} => R_{2} + R_{3} = \frac{990mV}{50\mu A} = 19.8K\Omega => R_{2} + R_{3} = 19.8K\Omega => R_{2}$$

$$= 19.8K\Omega - R_{3}$$

$$=>R_2=19.8K\Omega-270\Omega=>R_2=19.53K\Omega\approx 18K\Omega(standard value)$$

$$R_{max} = \frac{0.1V_{BE}}{I_{B(max)}} = \frac{0.1 \times 0.7}{500nA} = 140K\Omega \approx 120K\Omega \text{ (Standard Value)}$$

$$= 19.8K\Omega - R_{3}$$

$$= > R_{2} = 19.8K\Omega - 270\Omega => R_{2} = 19.53K\Omega \approx 18K\Omega (standard value)$$

$$R_{max} = \frac{0.1V_{BE}}{I_{B(max)}} = \frac{0.1 \times 0.7}{500nA} = 140K\Omega \approx 120K\Omega (Standard Value)$$

$$C_{1} = \frac{1}{2\pi f\left(\frac{R_{1}}{10}\right)} => C_{1} = \frac{1}{2\pi \times 120 \times \left(\frac{120K\Omega}{10}\right)} = 0.11\mu F \approx 0.1\mu F (Standard Value)$$

$$C_2 = \frac{1}{2\pi f R_L} = 0.6 \mu F \approx 0.68 \mu F (Standard Value)$$

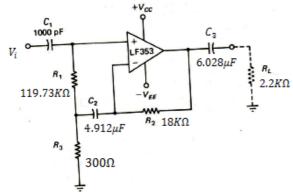

For High Input Impedance:

$$R_1 + R_3 = R_{(\text{max})} = \frac{0.1 V_{BE}}{I_{B(\text{max})}} = \frac{0.1 \times 0.7}{500 nA} = 140 K\Omega \approx 120 K\Omega \text{ (Standard Value)}$$

As

$$R_2 \approx 18K\Omega$$

and  $R_3 \approx 270\Omega$  hence  $R_1=R_{(max)}-R_3=>R_1=120K\Omega-270\Omega=119.73K\Omega$

AS  $Z_{in}$  is very high hence  $C_1$  has to be very small but its capacitance value should be greater than stray capacitance.

$$C_{1} = 1000pF$$

$$X_{C_{3}} = \frac{R_{L}}{10}$$

$$C_{3} = \frac{1}{2\pi f\left(\frac{R_{L}}{10}\right)} => C_{3} = \frac{1}{2\pi \times 120 \times \left(\frac{2.2K\Omega}{10}\right)} => C_{3} = 6.028\mu F$$

$$X_{C_{2}} = R_{3}$$

$$C_{2} = \frac{1}{2\pi f R_{3}} = \frac{1}{2\pi \times 120 \times 270} = 4.912\mu F$$

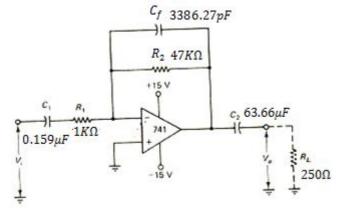

3 The inverting amplifier designed with  $V_o = 2.5V$  and  $A_V = 50$ , is to be capacitor [10] CO2 coupled and to have a signal frequency range of 10Hz to 1KHz. If the load resistance is  $250\Omega$ . Calculate the required capacitor values

$\it R_1$  and  $\it R_2$  resistors can be caluculated from the direct coupled inverting amplifier circ Calculation (5  $I_1 = 100 \times I_{B(max)} = 100 \times 500 nA = 50 \mu A$ marks)+ diagram (5  $V_i = \frac{V_o}{A_V} = \frac{2.5V}{50} = 0.05V$ marks)

$$R_1 = \frac{\dot{V_i}}{I_1} = \frac{0.05}{50\mu A} = 1K\Omega(Standard\ Value)$$

$$R_{2} = \frac{V_{o}}{I_{1}} = \frac{50\mu A}{50\mu A} = 50K\Omega \approx 47K\Omega \text{ (Standard Value)}$$

$$C_{1} = \frac{1}{2\pi f_{L} \left(\frac{R_{1}}{10}\right)} = > C_{1} = \frac{1}{2\pi \times 10 \times \left(\frac{1K\Omega}{10}\right)} = > C_{1} = 0.159\mu F$$

$$C_{2} = \frac{1}{2\pi f_{L} R_{L}} = \frac{1}{2\pi \times 10 \times 250\Omega} = 63.66\mu F$$

$$C_2 = \frac{1}{2\pi f_L R_L} = \frac{1}{2\pi \times 10 \times 250\Omega} = 63.66 \mu F$$

$$C_2 = \frac{1}{2\pi f_L R_L} = \frac{1}{2\pi \times 10 \times 250\Omega} = 63.66 \mu F$$

$$C_f = \frac{1}{2\pi f_H R_2} = \frac{1}{2\pi \times 1KHz \times 47K\Omega} = 3386.27pF$$

- 4 (a) What output voltage would be produced by a D/A converter whose output range is 0 to 10V and whose input binary number is

- **[5]** CO3 L1

- a) 10 (2-bit DAC)

- b) 0110 (4-bit DAC)

- c) 10111100(8-bit DAC)

ANSWER: (5 marks)

a)

$$V_0 = 10\left(\frac{1}{2} \times 1 + \frac{1}{4} \times 0\right) = 5V$$

b)

$$V_0 = 10 \left( \frac{1}{2} \times 0 + \frac{1}{4} \times 1 + \frac{1}{8} \times 1 + \frac{1}{16} \times 0 \right) = 3.75V$$

c)

$$V_0 = 10\left(\frac{1}{2} \times 1 + \frac{1}{2^2} \times 0 + \frac{1}{2^3} \times 1 + \frac{1}{2^4} \times 1 + \frac{1}{2^5} \times 1 + \frac{1}{2^6} \times 1 + \frac{1}{2^7} \times 0 + \frac{1}{2^8} \times 0\right) = 7.34V$$

- (b) Explain the working of A to D converter using successive approximation method.

- [**5**] CO3 L4

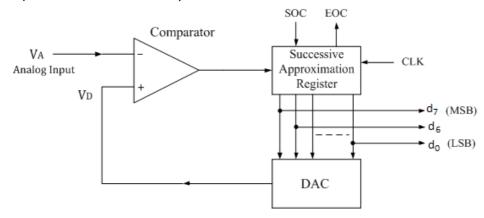

# SUCCESSIVE APPROXIMATION CONVERTER:

Diagram (3 marks)+ Explanation (2 marks)

- 1. The successive approximation technique was a very efficient code search strategy to complete n-bit conversion in just n-clock period.

- 2. E.g. an eight bit converter requires eight clock pulses to obtain a digital output.

- 3. The circuit uses a successive approximation register (SAR) to find the required value of each bit by trial and error.

- 4. With the arrival of START command, the SAR sets the MSB  $d_7=1$  with all other bits to zero, so that the trial code is 10000000.

- 5. The output  $V_d$  of the DAC is now compared with analog input  $V_a$ , if  $V_a$  is greater than  $V_d$ , then 10000000 is less than the correct digital representation. The MSB is remains at '1' and the next lower significant bit is made '1' and further tested.

- 6. However, if  $V_a$  is less than the DAC output, then 10000000 is greater than the current digital representation. So, reset the MSB to '0' and go on to the next lower significant bit.

- 7. This procedure is repeated for all subsequent bits, one at a time, until all the bit position has been tested.

- 8. When DAC output crosses  $V_a$ , the comparator changes state and this can be taken as the end of conversion (EOC) command.

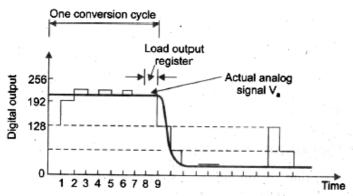

| Correct Digital Representation | Successive Approximation Register output $V_d$ at different stages in the conversion | Comparator Output |

|--------------------------------|--------------------------------------------------------------------------------------|-------------------|

| 11010100(212)                  | 10000000(128)                                                                        | 1                 |

|                                | 11000000(192)                                                                        | 1                 |

|                                | 11100000(224)                                                                        | 0                 |

|                                | 11010000(208)                                                                        | 1                 |

|                                | 11011000(216)                                                                        | 0                 |

|                                | 11010100(212)                                                                        | 1                 |

|                                | 11010110(214)                                                                        | 0                 |

|                                | 11010101(213)                                                                        | 0                 |

|                                | 11010100(212)                                                                        |                   |

The D/A output voltage is seen to become successively closer to the actual analog input voltage

9. It is seen that the DAC output voltage is closer to the actual input voltage. It requires 8 pulses to establish the accurate output regardless the value of the analog input. One additional clock pulse is required to load the output register and reinitialize the circuit.

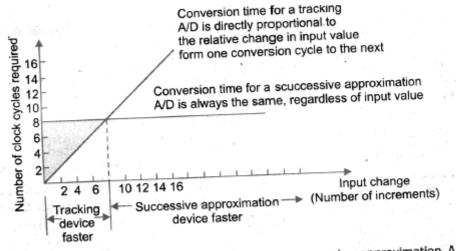

Comparison of conversion times for tracking and successive approximation A/D

- 10. It is seen that successive approximation technique is more versatile. The tracking circuit is faster only for small changes in the input.

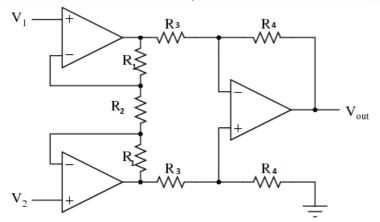

- 5 Explain the instrumentation amplifier with differential input/output which accepts a differential input voltage and amplifies it to produce a differential output using OPAMP

### **INSTRUMENTATION AMPLIFIER:**

Instrumentation amplifier is the front end component of every measuring

[10] CO2 L4

Diagram (5 marks)+ Explanation (5 marks) instrument which receives the signal from the input electrical signal from the transducer. It uses the fact the noise is common to the both output terminals of a transducer across which the output is measured and sent to measuring instrument.

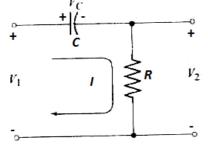

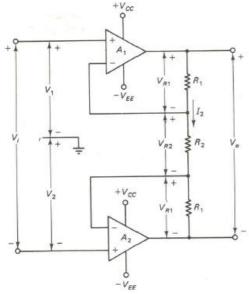

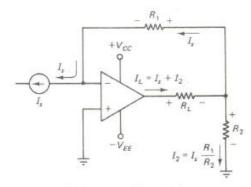

### Differential input differential Output Amplifier:

This circuit accepts a differential input voltage and produces a differential output. The voltage at the junction of  $R_1$  and  $R_2$  is equal to the input voltage. Also, the voltage at the junction of  $R_2$  and  $R_3$  equals input voltage  $V_2$ . The voltage across  $R_2$  is

$$V_{R_2} = V_1 - V_2 = V_i$$

The circuit current through  $R_2$  as  $I_2 = \frac{V_i}{R_2}$

The differential output voltage is

$$V_o = V_{R_1} + V_{R_2} + V_{R_3} = I_2(R_1 + R_2 + R_3) = \frac{V_i}{R_2}(R_1 + R_2 + R_3)$$

The circuit differential voltage gain is

$$A_V = \frac{V_o}{V_i} = \frac{R_1 + R_2 + R_3}{R_2} \quad normally \quad R_1 = R_3 \quad hence \quad A_V = \frac{2R_1 + R_2}{R_2}$$

(Voltage gain can be altered by adjusting a single resistor  $R_2$ )

Suppose 2 inputs are connected together and a common mode noise voltage  $V_n$  is applied to the two. The junction of  $R_1$  and  $R_2$  will be at the same voltage as the noninverting input terminal of  $A_1$  and the junction of  $R_2$  and  $R_3$  will be at the same potential as the non-inverting input of  $A_2$ . That is both resistor junctions will be at  $V_n$ . There will be no current flow through  $R_1$ ,  $R_2$  or  $R_3$  and the output of the amplifier will be  $V_n$ . This means the common mode gain is

[A common mode voltage applied to a differential input and differntial output amplifier]

So common mode signals will be passed through but not amplified by the differential input differential output amplifier.

- 1. The differential input and differential output amplifier is used in conjunction with the difference amplifier. The input impedance of differential input differential output amplifier is extremely high because of the non-inverting amplifier configuration. The input impedance of the differential amplifier is  $R_i = R_1$  at the inverting terminal and  $R_i = (R_3 + R_4)$  at the non-inverting terminal.

- 2. The voltage gain of the differential input and differential output stage can be changed by adjusting only one resistor  $R_2$ . Changing the gain of the differential amplifier requires  $R_2$  and  $R_4$  to be adjusted together to maintain equal amplification of both inputs.

- 3. The common mode gain of the differential input/output amplifier is 1, compared to common mode gain of zero for the difference amplifier.

- 4. The differential input/output amplifier operates with a floating load, while the difference amplifier uses a grounded load.

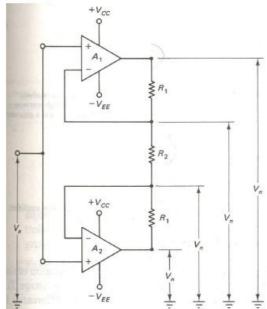

### **Differential Amplifier:**

The instrumentation amplifier is a combination of differential input/output amplifier (stage 1) and difference amplifier (stage 2). The voltage gain of the complete circuit is

$$\begin{split} A_V &= A_{V_1}.\,A_{V_2} \\ Wehere \ A_{V_1} &= \left(1 + \frac{2R_1}{R_2}\right) \ and \ A_{V_2} &= \frac{R_4}{R_3} \\ A_V &= \left(1 + \frac{2R_1}{R_2}\right) \left(\frac{R_4}{R_3}\right) \end{split}$$

Instrumentation amplifier is a combination of the differential input/output amplifier (Stage 1) and difference amplifier (stage 2)

$A_V = \left(1 + \frac{2R_1}{R_2}\right) \left(\frac{R_4}{R_3}\right)$  The overall gain can be controlled by adjustment of  $R_2$

Draw the circuit of OPAMP Astable Multivibrator and explain its operation.

[10] CO3 L2

Diagram (5 marks)+ Explanation (5 marks)

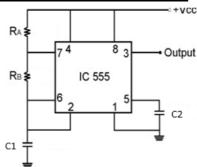

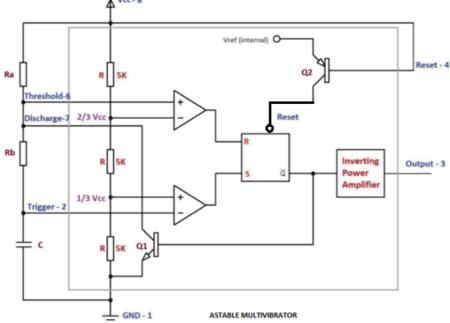

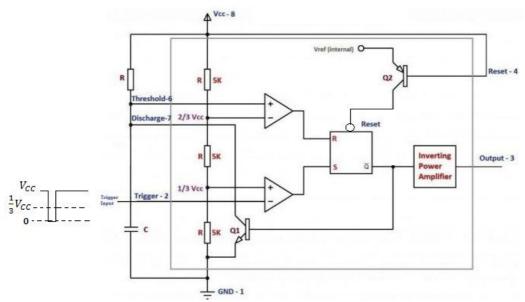

#### ASTABLE MULTIVIBRATOR:

6

### Asymmetric

- 1. When the power supply  $V_{CC}$  is connected, the external timing capacitor C charges towards  $V_{CC}$  with a time constant  $(R_A+R_B)C$ . During this time the upper comparator produces the output as LOW and the lower comparator produces the output as HIGH. Hence the output of the S-R flip-flop is HIGH. i.e. Q=1 (HIGH) and  $\bar{Q}=0$  (LOW). At the same time transistor  $Q_1$  is OFF.

- 2. When the capacitor voltage is just greater than  $\frac{2}{3}V_{CC}$ , the upper comparator produces HIGH output and the lower comparator output is LOW. Hence the output of the S-R flip -flop is LOW. i.e. Q=0 (LOW) and  $\bar{Q}=1$  (HIGH). So the transistor  $Q_1$  is ON and the capacitor starts discharging towards ground through  $R_B$ .

- 3. During the discharge of the capacitor C, as it reaches just less than  $\frac{1}{3}V_{CC}$ , the lower comparator produces the output HIGH and the upper comparator produces the output as LOW. Hence the output of the S-R flip-flop is HIGH. i.e. Q=1 (HIGH) and  $\bar{Q}=0$  (LOW). At the same time transistor  $Q_1$  is OFF, so the capacitor starts charging.

4. The capacitor is thus periodically charged and discharged between  $\frac{2}{3}V_{CC}$  and  $\frac{1}{3}V_{CC}$  respectively.

Capacitor voltage at any instant of time can be calculated as

$$V_{C}(t) = V_{C(final)} + \left[V_{C(initial)} - V_{C(final)}\right]e^{-\frac{t}{\tau}}$$

$$V_{C}(t) = V_{CC} + \left[\frac{1}{3}V_{CC} - V_{CC}\right]e^{-\frac{t}{(R_{A} + R_{B})C}} \quad as \quad \tau = (R_{A} + R_{B})C$$

$$V_{C}(t) = V_{CC} + \left[-\frac{2}{3}V_{CC}\right]e^{-\frac{t}{(R_{A} + R_{B})C}}$$

$$at \quad t = T_{ON} \quad , V_{C}(t) = \frac{2}{3}V_{CC}$$

$$\frac{2}{3}V_{CC} = V_{CC} - \frac{2}{3}V_{CC}e^{-\frac{T_{ON}}{(R_{A} + R_{B})C}} = > \frac{2}{3}V_{CC} - V_{CC} = -\frac{2}{3}V_{CC}e^{-\frac{T_{ON}}{(R_{A} + R_{B})C}}$$

$$= > -\frac{1}{3}V_{CC} = -\frac{2}{3}V_{CC}e^{-\frac{T_{ON}}{(R_{A} + R_{B})C}} = > 1 = 2e^{-\frac{T_{ON}}{(R_{A} + R_{B})C}} = > \frac{1}{2} = e^{-\frac{T_{ON}}{(R_{A} + R_{B})C}}$$

$$= > \ln\left(\frac{1}{2}\right) = -\frac{T_{ON}}{(R_{A} + R_{B})C} = > -0.693 = -\frac{T_{ON}}{(R_{A} + R_{B})C} = > T_{ON} = 0.693(R_{A} + R_{B})C$$

Similarly  $T_{OFF}$  can be derived as  $T_{OFF} = 0.693R_BC$

Duty Cycle,

$$D = \frac{T_{ON}}{T}$$

$$T = T_{ON} + T_{OFF}$$

Duty Cycle

$$D = \frac{T_{ON}}{T_{ON} + T_{OFF}} = \frac{0.693(R_A + R_B)C}{0.693(R_A + 2R_B)C} = \frac{R_A + R_B}{R_A + 2R_B}$$

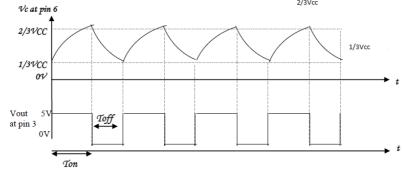

- 7 (a) Design a precision voltage source to provide an output of 9V, the available supply is  $\pm 12V$ . Allow for approximately  $\pm 10\%$  tolerance on the zener voltage.

- [5] CO<sub>2</sub> L<sub>3</sub>

$V_z = \frac{V_o}{2} = \frac{9}{2} = 4.5V$

Diagram(2 marks)+ Calculation (3 marks)

The recommended current for best voltage stability current for zener diode is

$$I_Z = 20mA$$

$$R_1 = \frac{V_o - V_Z}{I_Z} = \frac{9 - 4.5}{20mA} = 225\Omega \approx 220\Omega(Standard Value)$$

For

$$R_2$$

,  $R_3$  and  $R_4$

$$I_2 \gg I_{B(max)}$$

$$I_2 = 100 \times I_{B(max)} = 100 \times 500 nA = 50 \mu A$$

$$I_2 = 100 \times I_{B(max)} = 100 \times 500nA = 50\mu A$$

$R_3 + R_4 = \frac{V_Z + 10\%}{I_2} = \frac{4.5 + 0.45}{50\mu A} = 99K\Omega$

$$R_4 = 20\% \text{ of } (R_3 + R_4) = 20\% \text{ of } 99K\Omega = 19.8K\Omega \approx 20K\Omega (POT)$$

$$R_3 = 99K\Omega - 20K\Omega = 79K\Omega \approx 82K\Omega(Standard Value)$$

$$R_2 = \frac{V_o - (V_Z + 10\%)}{I_2} = \frac{9 - (4.5 + 0.45)}{50\mu A} = 81K\Omega$$

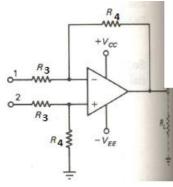

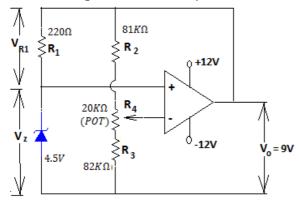

Explain the current amplifier circuit using operational amplifier and do necessary modification to the circuit to make it independent of load resistance.

#### [5] CO<sub>2</sub> L<sub>4</sub>

Diagram(3 marks)+

Explanation (2

Marks)

### Current Amplifier:

In this circuit  $R_2$  has been added to the circuit. The current through  $R_2$  is

$$I_2 = \frac{V_o}{R_2} = \frac{I_S R_1}{R_2}$$

Hence the output current is  $\frac{R_1}{R_2}$  times of the input current and this circuit is a

current amplifier if  $R_1 > R_2$

But if  $R_1 < R_2$  then, the circuit is a current attenuator.

The disadvantage of the circuit is that the current gain/attenuation is dependent on the resistance value of  $R_2$ , which is the load resistance. If the load can be floating (ungrounded), then the circuit will become

(b) Current amplifier with gain independent of load

Here load current

8

$$I_L = I_S + I_2 = I_S + \frac{V_o}{R_2} = I_S + \frac{I_S R_1}{R_2} = > I_L = I_S \left( 1 + \frac{R_1}{R_2} \right)$$

Here the load current is independent of  $R_L$ . Hence the circuit operated as a current amplifier with a gain, which is independent of load resistance.

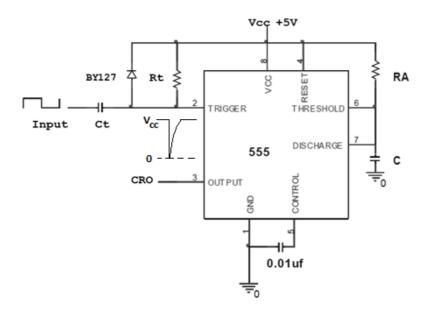

Draw the circuit of OPAMP Monostable Multivibrator and explain its [10] CO3 L2 operation.

## MONOSTABLE OPERATION:

Diagram (5 marks)+ Explanation (5 marks)

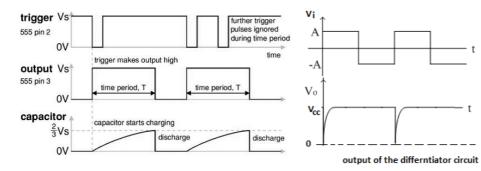

- 1. Initially as the flip-flop output Q=0 (LOW) and  $\bar{Q}=1$  (HIGH). This makes the output LOW and the external timing capacitor  $\mathcal C$  is having zero potential because the transistor  $Q_1$  is ON.

- 2. When trigger is provided, the lower comparator produce the output as HIGH and at the same time the upper comparator produce the output as LOW , Hence the S-R flip-flop becomes SET. i.e.  $Q=1~(HIGH)~and~\bar{Q}=0~(LOW)$ , this makes the output HIGH and the capacitor starts charging exponentially through R towards  $V_{CC}$  with a time constant RC.

- 3. When the capacitor voltage is with in  $V_{\rm C} < \frac{2}{3} V_{\rm CC}$

4. After the time period "T" the capacitor voltage is just greater than  $\frac{2}{3}V_{CC}$ . The lower comparator produces the output as LOW and the upper comparator produces the output as HIGH, hence the S-R flip-flop becomes RESET. i.e. Q=0 (LOW) and  $\bar{Q}=1$  (HIGH), this makes the output LOW and the capacitor starts discharging the capacitor rapidly to ground potential. Capacitor voltage at any instant of time can be calculated as

$$\begin{split} V_C(t) &= V_{CC} \left[ 1 - e^{-\frac{t}{RC}} \right] \\ at \ t &= T_{ON} \ , V_C(t) = \frac{2}{3} V_{CC} \\ \frac{2}{3} V_{CC} &= V_{CC} \left[ 1 - e^{-\frac{T_{ON}}{RC}} \right] = > \frac{2}{3} V_{CC} = V_{CC} - V_{CC} e^{-\frac{T_{ON}}{RC}} = > \frac{2}{3} V_{CC} - V_{CC} = -V_{CC} e^{-\frac{T_{ON}}{RC}} \\ &= > -\frac{1}{3} V_{CC} = -V_{CC} e^{-\frac{T_{ON}}{RC}} = > \frac{1}{3} = e^{-\frac{T_{ON}}{RC}} \\ &= > \ln\left(\frac{1}{3}\right) = -\frac{T_{ON}}{RC} = > -1.1 = -\frac{T_{ON}}{RC} = > T_{ON} = 1.1RC \end{split}$$