### Solutions & Scheme of Evaluation Internal Assessment Test 1 – March.2019

| Sub:  | Linear Integrated circuits |           |        |               |    |      |    | Code:   | 17EC45       |

|-------|----------------------------|-----------|--------|---------------|----|------|----|---------|--------------|

| Date: | 07/03/2019                 | Duration: | 90mins | Max<br>Marks: | 50 | Sem: | IV | Branch: | ECE(A,B,C,D) |

**Note:** Answer Any Five Questions

| Que<br>stion<br># | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Max<br>Mar<br>ks |  |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|--|--|

| 1                 | Explain in detail the basic op-amp internal circuit with a neat diagram and also explain input and output voltage ranges.                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |  |  |  |  |  |  |  |

|                   | <ul> <li>circuit diagram – 4M</li> <li>Explanation – 4M</li> <li>input and output voltage range – 2M</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |  |  |  |  |  |  |  |

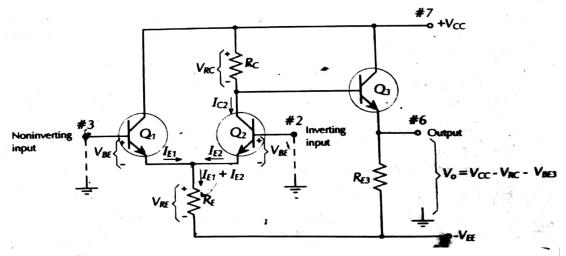

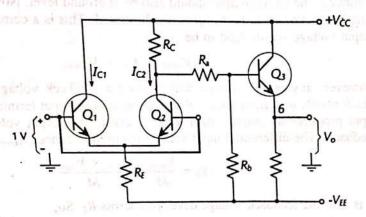

|                   | BASIC OPERATIONAL AMPLIFIER CIRCUIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |  |  |  |  |  |  |  |

|                   | The basic circuit of an operational amplifier is illustrated in Fig. 1-4. Plus and minus supply voltages $(+V_{CC})$ and $-V_{EE}$ are provided, and the two input terminals are grounded. Transistors $Q_1$ and $Q_2$ constitute a differential amplifier, which produces a voltage change at the collector of $Q_2$ when a difference input voltage is applied to the bases of $Q_1$ and $Q_2$ . Transistor $Q_3$ operates as an emitter-follower to provide a low output impedance. As illustrated, the $dc$ output voltage level at terminal # 6 is |                  |  |  |  |  |  |  |  |

|                   | $V_o = V_{CC} - V_{RC} - V_{BE3}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |  |  |  |  |  |  |  |

|                   | or $V_o = V_{CC} - (I_{C2}R_C) - V_{BE}$ (1-1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |  |  |  |  |  |  |  |

|                   | Assume that $Q_1$ and $Q_2$ are matched transistors, that is they have equal $V_{BE}$ levels and equal current gains. Then, with both transistor bases at ground level, the emitter currents are equal, and both $I_{E1}$ and $I_{E2}$ flow through the common emitter resistor, $R_E$ . The total emitter current could be calculated as                                                                                                                                                                                                               |                  |  |  |  |  |  |  |  |

|                   | $I_{E1} + I_{E2} = \frac{V_{RE}}{R_E}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |  |  |  |  |  |  |  |

|                   | With $Q_1$ and $Q_2$ bases grounded,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |  |  |  |  |  |  |  |

|                   | $V_{RE} = V_{EE} - V_{BE}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                  |  |  |  |  |  |  |  |

|                   | so,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |  |  |  |  |  |  |  |

|                   | $I_{E1} + I_{E2} = \frac{V_{EE} - V_{BE}}{R_E} \tag{1-2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |  |  |  |  |  |  |  |

|                   | To investigate the circuit operation, assume that $V_{CC} = +10 \text{ V}$ , $V_{EE} = -10 \text{ V}$ , $R_E = 4.7 \text{ k}\Omega$ , $R_C = 6.8 \text{ k}\Omega$ , and all transistors have $V_{BE} = 0.7 \text{ V}$ .                                                                                                                                                                                                                                                                                                                                 |                  |  |  |  |  |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |  |  |  |  |  |  |  |

With both input terminals at ground level,

Eq. 1-2,

$$I_{E1} + I_{E2} = \frac{V_{EE} - V_{BE}}{R_E} = \frac{10 \text{ V} - 0.7 \text{ V}}{4.7 \text{ k}\Omega}$$

$$\approx 2 \text{ mA}$$

therefore,

$$I_{E1} = I_{E2} = 1 \text{ mA}$$

and

$$I_{C2} \approx I_{E2} \approx 1 \text{ mA}$$

Eq. 1-1,

$$V_o = V_{CC} - (I_{C2}R_C) - V_{BE}$$

$$\approx 10 \text{ V} - (1 \text{ mA} \times 6.8 \text{ k}\Omega) - 0.7 \text{ V}$$

$$\approx 2.5 \text{ V}$$

If a positive-going voltage is applied to the noninverting input terminal,  $Q_1$  base is pulled up by the input voltage, and its emitter terminal tends to follow the input signal. Since  $Q_1$  and  $Q_2$  emitters are connected together, the emitter of  $Q_2$  is also pulled up by the positive-going signal at the noninverting input terminal. The base voltage of  $Q_2$  is fixed at ground level so the positive-going movement at its emitter causes a reduction in its base-emitter voltage  $(V_{BE2})$ . The result of the reduction in  $V_{BE2}$  is that its emitter current is reduced and consequently its collector current is reduced.

For convenience, assume that the positive-going input at the base of  $Q_1$  reduces  $I_{C2}$  by 0.2 mA, (i.e., from 1 mA to 0.8 mA). This gives a new level of output voltage.

Eq. 1-1,

$$V_o = V_{CC} - (I_{C2}R_C) - V_{BE}$$

= 10 V - (0.8 mA × 6.8 k $\Omega$ ) - 0.7 V

$\approx 3.9$  V

The output voltage has changed from +2.5 V to +3.9 V, a change of +1.4 V. It is seen that a positive-going signal at the noninverting input terminal has produced a positive-going output voltage.

Now consider what occurs when the noninverting terminal is grounded and a positive-going input is applied to the inverting input terminal. In this case,  $Q_2$  base is pulled up, the base-emitter voltage of  $Q_2$  is increased, and that of  $Q_1$  is reduced by a similar amount. This results in an increase in  $I_{E2}$  and a consequent increase in  $I_{C2}$ .

Once again, for convenience, assume that a 0.2 mA change occurs in  $l_{c2}$ . Thus,  $I_{c2}$  is increased from 1 mA to 1.2 mA by the positive-going voltage at the inverting input terminal. The output voltage can now be calculated as

Eq. 1-1,

$$V_o = V_{CC} - (I_{C2}R_C) - V_{BE}$$

= 10 V - (1.2 mA × 6.8 k $\Omega$ ) - 0.7 V

$\approx$  1.1 V

For  $V_s = \pm 15V$ Input range  $\pm 13V$ Output swing  $\pm 14V$

- 2 a) 741 op-amp is used in a non inverting amplifier with a voltage gain of 50. Calculate the typical output voltage that would result from a common mode input with a peak level of 100 mv.

- CMRR= 31623 2M

- $V0(cm) = 158 \mu V 3M$

Soln: Given

$$Av = 50$$

$V_{i(cm)} = 100 \text{ mV}$

WKT Applical value of CMRR for 741 op-amp is 90 dB.

$$(CMRR)_{dB} = 20 \log CMRR$$

$$CMRR = antilog \left[ \frac{(CMRR)_{dB}}{20} \right] = antilog \left[ \frac{90}{20} \right] = 31,623$$

$$V_{0(cm)} = \frac{V_{i(cm)}}{CMRR} \cdot A_{V} = \frac{100 \text{ m}}{31,623} \times 50 = 158 \,\mu\text{V}$$

$$\overline{V_{0(cm)}} = 158 \,\mu\text{V}$$

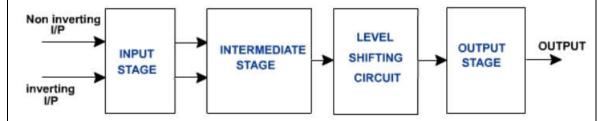

b) With a neat block diagram, explain the general stages of an op-amp IC.

- Block diagram 2M

- Explanation 3M

10 M

#### BLOCK DIAGRAM REPRESENTATION OF A TYPICAL OPAMP:

#### [BLOCK DIAGRAM OF A TYPICAL OPAMP]

#### **INPUT STAGE:**

- 1. The input stage is the dual input balanced output differential amplifier.

- 2. This stage provides most of the voltage gain of the amplifier.

- 3. It also establishes the input resistance of the OPAMP.

#### INTERMEDIATE STAGE:

- 1. The intermediate stage is usually another differential amplifier which is driven by the output of the first stage.

- 2. In most amplifiers the intermediate stage is dual input and unbalanced (Single ended) output.

#### LEVEL SHIFTING CIRCUIT:

1. Because direct coupling is used, the DC voltage at the output of the intermediate stage is above ground potential. Therefore, generally the level shifting circuit is used after the intermediate stage to shift the DC level of the output voltage downward to zero voltage with respect to ground.

#### **OUTPUT STAGE:**

- 1. The output stage is usually the emitter follower circuit.

- 2. The output stage increases the output voltage swing and raises the current supplying capability of the OPAMP.

- 3. The output stage provides low output resistance.

- Analyze a voltage follower circuit implemented using a 741 op-amp. Find the minimum and 3 a) maximum input and output impedances with feedback.

$$\begin{array}{c|cccc} AOLmin=50,\!000 & \parallel & Zi=2 \ M\Omega \\ AOLmax=2,\!00,\!000 \parallel & Zo=75 \ \Omega \\ \end{array}$$

- Zin 2M

- Zout 2M

Solm:

$$\omega \cdot R \cdot T$$

$Z_0 = 75\Omega$   $M = 2,00,000$  (from  $B = 1$  for  $VF$  (1+ MB) (1+200000)

$$Z_{\text{out}} = 0.004\Omega$$

- b) Design a direct coupled inverting amplifier with gain 50 and output voltage amplitude is to be 2.5 V

- I1 =  $50\mu$ A, Vi=50 mv, R3=1K $\Omega$  1M each

- R1= 1K $\Omega$ , R2 = 50K $\Omega$  1.5M each

Soln: Given:

$$Av = 50$$

$V_0 = 3.5V$

$$Av = \frac{V_0}{Vin} \Rightarrow Vin = \frac{V_0}{Av} = 50 \text{ mV}$$

$$Et I_1 = 100I_{Emax} = 100(500n) = 50\mu A$$

$$Vin = \frac{I_1}{R_1} \Rightarrow R_1 = \frac{Vin}{I_1} = \frac{50m}{50\mu} = 1K\Omega$$

$$R_2 = \frac{V_0}{I_1} = \frac{3.5}{50\mu} = 50 K\Omega$$

$$R_3 = R_1 || R_2 = 50 K || 1K\Omega = 1K\Omega$$

$$R_3 = 1K\Omega$$

$$R_3 = 1K\Omega$$

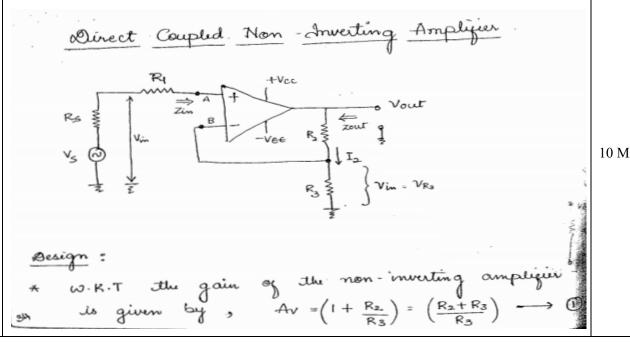

- a) Draw an ideal non inverting amplifier using op-amp and derive the expression for its close loop gain.

- Circuit diagram 2M

- Derivation 3M

For Bipolar op-amp, Select the potential diagram current (Fa) to be much larger than the man input bias curent Is (max) i.e I2 = 100 IB(max) --- 2 For BIFET op-amp, largest resistor value is girst Selected as IMA potential divider resistor values are determined using Vin , Vout and Is  $R_3 = \frac{V_{R3}}{I_2} = \frac{V_{in}}{I_2} \longrightarrow 3 \left[ \text{?? } V_{R3} = V_{in} \right]$ \* Vout appears across R, and R3 i.e  $\left(R_2 + R_3\right) = \frac{\text{Vout}}{I_*} \longrightarrow \text{(f)}$ Finally to equalize the IBR voltage drops at the input iterminals. R1 = R2 || R3 Re is not much larger than the Source resistance Re should be determined from, (Rs+R1) = R2 11 R3 Define i) PSRR ii) slew rate iii) output impedance

b)

iv) Input offset voltage v) Input offset current

5 X 1M = 5M

• Each definition 1M

Power Supply Voltage Rejection / (PSRR or SVRR) Variation in -Vee change the output vallage which has same effect as that of input voltage change. This can be limited using constant current source [Reper not] \* Even with this circuity, variations in vcc and Vec produces some change in output. \* PSRR is a measure of how effective the ap-amp is in dealing with variations in supply voltage \* of variation of IV in Vac or Vee causes the culput to by 10 mv, thin PSRR is 10 mv per valt. PSRR = Vo(vip) Vs(Tip) for 741 op-amp, typical value of PSRR = 30 pv/v Slew Rate \* Show rate of an op-amp is the maximum rate at which the output voltage can change \* when slew rate is too slow, distortion results. 1/µs \* consider a voltage follower circuit and sine wave is applied as an input to the circuit. Alar wave results because op-amp output simply cannot move fast enough to jollow the sinewave input. a= Dt b = DV

for 741 op-amp, typical Slew rate SR = 0.5 1/ usec

### Output donpedance

\* Like Zin, Zout is also affected by -ve feedback

Zout = Zo

(1+MB)

where, Zo = ap-amp of impedance orithaut - ve feedback

M = open boop gain of op-amp.

B = feedback factor.

Zout = autput impedance ey circuit.

output impedance, typical value to = 75.2

## Input offset and Output offset voltage.

consider op-amp basic circuit as voltage follower where output follows the input. (Vo = Vin)

\* For a output voltage to be exactly equal to the input voltage, a and a needs to be matched.

applying KVL.  $V_{in} - V_{Be_1} + V_{Be_2} = V_0$  when  $Q_1$  and  $Q_2$  are modeled transistors,  $V_{Be_1}$  and  $V_{Be_2}$  equal and when  $V_{in} = 0$ ,  $V_{in} = V_0 = 0$

\* when a and a ou not perfectly matched say,

VBC1 = 0.7V and VBC0 = 0.6V, Vin = 0

Vo = 0 -0.7 +0.6 = -0.1

This unwanted output voltage is known as output offset vilg To make this vo=0, the input needs to be raised to +0.1v, this is known as Input offset voltage.

\* Note: For IHI ap-Amp

Input offset voltage: Typical value Vios = 1m1V

when smitter Base voltages  $V_{BE1} \neq V_{BE2}$  and current gain  $h_{Fe_1} \neq h_{Fe_2}$

W.K.T Ic = B. IB

\* Even though both transistors have equal levels of  $I_c$ ,  $I_B$  of one transistor may vary from the other. i.e.  $A_L$   $I_{B_1} = 1 \mu A$ ,  $I_{B_2} = 1.2 \mu A$

\* The difference in these two input current levels is known as input offset current

even when  $R_1=R_2$ ,  $I_{i0}$  produces rinequal vity drop across these resistors and this difference in voltage drop behaves as a differential input voltage which produces an output offset voltage.

Note: For 7411 op-amp, Typical value Iio = 200nA

Input Offset Current

$$V_d = V_{R_1} - V_{R_2}$$

$V_d = I_{B_1}R_1 - I_{B_2}R_2$

Explain common mode voltage, common mode voltage gain and CMRR for op-amp. Show that  $V_{o(cm)} = \frac{V_{i(cm)}}{CMRR} \times A_{CL}$  for non inverting amplifier.

- VC, Ac, CMRR 1M Each

- Derivation 7M

## Common Mode Rejection

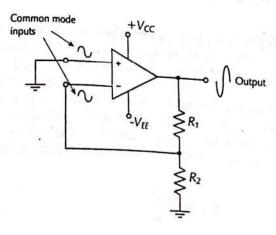

Refer again to the basic operational amplifier circuit in Fig. 1-9(b) reproduced in Fig. 2-3 with the feedback connection from output to input deleted. The two input terminals are connected together and both are raised to 1 V above ground level. This is known as a common mode input. Note that there is no differential input; both input terminals are at the same potential. So ideally the output should be zero.

Figure 2-3 Basic op-amp circuit with the two input terminals connected together, and a common mode input voltage applied. The common mode rejection ratio (CMRR) is the open-loop gain divided by the common mode gain. CMRR = M/A<sub>cm</sub>.

Because the base voltages of  $Q_1$  and  $Q_2$  are raised to 1 V above ground, the voltage drop across emitter resistor  $R_E$  is increased by 1 V, and, consequently,  $I_{C1}$  and  $I_{C2}$  are increased. The increased level of  $I_{C2}$  produces an increased voltage drop across resistor  $R_C$ , which results in a change in the output voltage at the emitter of  $Q_3$ . Similarly, if a -1 V common mode input is applied,  $I_{C2}$  falls, and again a change is produced at the circuit output. So, as well as the open-loop (differential input) gain M, each op-amp has a common mode voltage gain  $A_{cm}$ . The common mode gain is the output voltage change due to the common mode input divided by the common mode input voltage.

$$A_{cm} = \frac{V_{o(cm)}}{V_{i(cm)}}$$

10 M

The above discussion refers to the basic operational amplifier circuit. A practical operational amplifier has additional circuitry, such as the constant current tail in Fig. 1-5(a), to minimize the effects of common mode inputs. However, even with such circuitry, common mode signals still have some effect on the output. The success of the op-amp in rejecting common mode inputs is defined in the common mode rejection ratio (CMRR). This is the ratio of the open-loop gain M to the common mode gain  $A_{cm}$ .

$$CMRR = \frac{M}{A_{cm}} \tag{2-1}$$

The CMRR is usually expressed as a decibel quantity on the op-amp data sheet.

$$CMRR = 20 \log \frac{M}{A_{cm}} dB$$

(2-2)

The effect of op-amp common mode gain is modified by feedback, just as the open-loop differential gain is modified by feedback to give a closed-loop gain. Consider the noninverting amplifier circuit in Fig. 2-4. With the input terminal grounded, the circuit output should also be at ground level. Now suppose a sine wave signal is picked up at both inputs, as illustrated. This is a common mode input. The output voltage should tend to be

$$V_{o(cm)} = A_{cm} \times V_{i(com)}$$

However, any output voltage will produce a feedback voltage across resistor  $R_2$ , which results in a differential voltage at the op-amp input terminals. The differential input produces an output which tends to cancel the output voltage that caused the feedback. The differential input voltage required to cancel  $V_{o(cm)}$  is,

$$V_d = \frac{V_{o(cm)}}{M} = \frac{A_{cm} \times V_{i(cm)}}{M}$$

$V_d$  is also the feedback voltage developed across  $R_2$ . So,

$$V_d = \frac{V_{o(cm)} \times R_2}{R_1 + R_2}$$

Figure 2-4 A common mode input voltage appears at both input terminals. It is amplified by the common mode gain, but the gain is affected by negative feedback.

\* As Rs is much smaller than Zin, there call be no significant close in signal and all Vin appears at input terminal.

Vin: \( \frac{Vs \ Zin}{R\_S + \ Zin} \)

\* actual output of op-amp is,

\( \frac{Vout}{Vout} = \frac{Vin}{I - \frac{1}{M}} \)

\* As Re is much greater than Zout, entire output of ap-amp is obtained across Re i.e. \( V\_L = Vout \)

thus there is no any signal loss.

\( V\_L = \frac{Vout \ RL}{R\_L + Zout} \)

(as Zout is less)

\( V\_L = Vout \)

\( \frac{Vout}{R\_L + Zout} \)

(as Zout is less)

\( V\_L = Vout \)

\( \frac{Vout}{R\_L + Zout} \)

\( \frac{Vout}{R\_L + Zout}

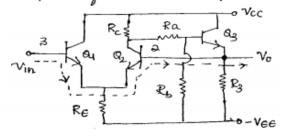

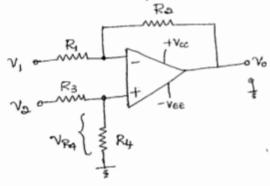

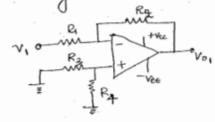

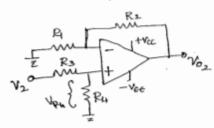

- b) Sketch an op-amp directly coupled difference amplifier circuit. Derive an equation for the output voltage and explain the operation.

- Circuit diagram 2M

- derivation -2M

- explanation 2M

# Difference Amplijar

Difference Amplifier amplifier the difference between two input signals. At has a inputs connected at both inverting as well as non-inverting terminal

the analysis of the above circuit can be done by using superposition theorem.

case i) when input at non inverting terminal  $u_1$  grounded i-e  $V_2 = 0$  and  $V_1$  is acting.

\* The circuit behaves like typical inverting ampliques.

gain Av - - Re Ri

$$V_{01} = Av \cdot V_1 = -\frac{Ra}{R_1} V_1 \longrightarrow \overline{D}$$

case ii) when input at inverting terminal is grounded i.e  $V_1 = 0$  and  $V_2$  is acting.

\* The circuit is simply a non inverting amplifier.

... gain Av : 1+ B2

R1

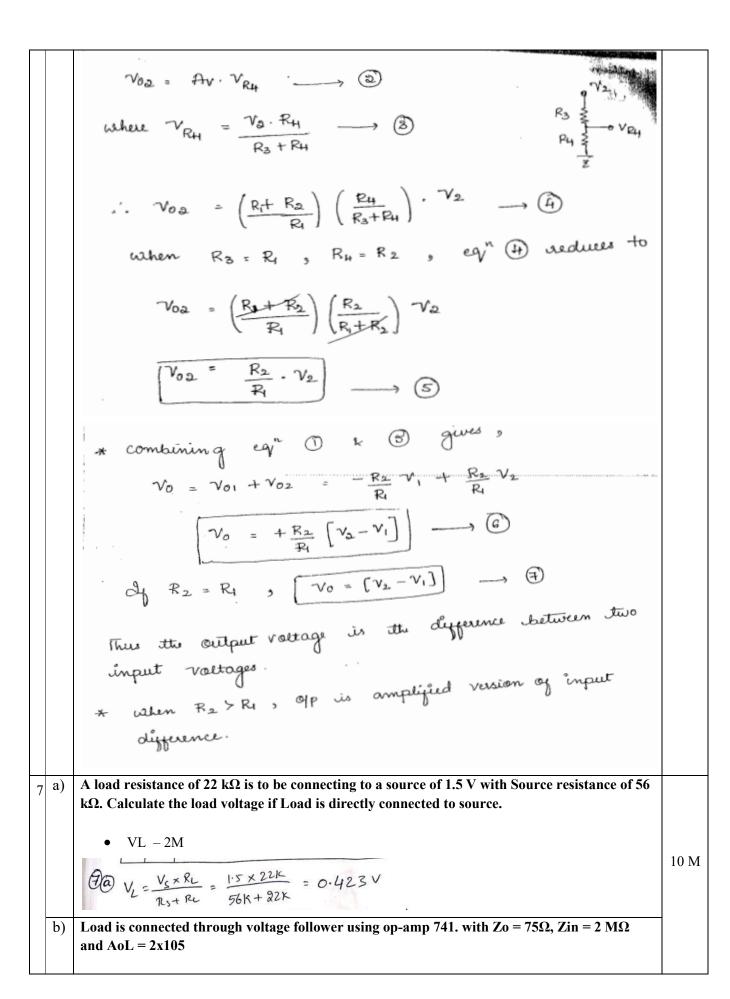

• Vi, Vo, Zout, VL - each 2M

$$\frac{76}{R} V_{L} = \frac{V_{S} \times R_{L}}{R_{S} + R_{L}} = \frac{1.5 \times 22 K}{56 K + 32 K} = 0.423 V$$

$$\frac{7}{R_{S} + R_{L}} = \frac{1.5 \times 22 K}{56 K + 32 K} = 0.423 V$$

$$\frac{7}{R_{S} + R_{L}} = \frac{75}{1 + 2 \times 10^{5}} = 3.75 \times 10^{5} V$$

$$V_{I} = \frac{V_{S} \times Z_{Iw}}{R_{S} + Z_{Iw}} = \frac{1.5 \times 4 \times 10^{11}}{56 K + 4 \times 10^{11}} = 1.499 \approx 1.5 V$$

$$V_{O} = V_{I} \left(1 - \frac{1}{R_{OL}}\right) = 1.5 \left(1 - \frac{1}{2 \times 10^{5}}\right) \approx 1.5 V$$

$$V_{O} = V_{I} \left(1 - \frac{1}{R_{OL}}\right) = 1.5 \left(1 - \frac{1}{2 \times 10^{5}}\right) \approx 1.5 V$$