### Scheme Of Evaluation and Solution Internal Assessment Test 1 – March 2019

| Sub:  | ARM MICROCONTROLLER & EMBEDDED SYSTEM |           |         |               |    | Sec  | A  |         |     |

|-------|---------------------------------------|-----------|---------|---------------|----|------|----|---------|-----|

| Date: | 5 / 03 / 2019                         | Duration: | 90 mins | Max<br>Marks: | 50 | Sem: | VI | Branch: | TCE |

**Note:** Answer Any Five Questions

|   | Description                                                                                                                          | Marks Di                        | stribution        |      |

|---|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------|------|

| 1 | Explain interrupts and oprocessor.  Definition/ theory of interrupts and oprocessor.  Tabulation of Any 7 interrupts and oprocessor. |                                 | 3M<br>7M          | 10 M |

| 2 | List and explain the ap processor.  5 application each carry 2                                                                       | plications of Cortex M3         | 10M               | 10 M |

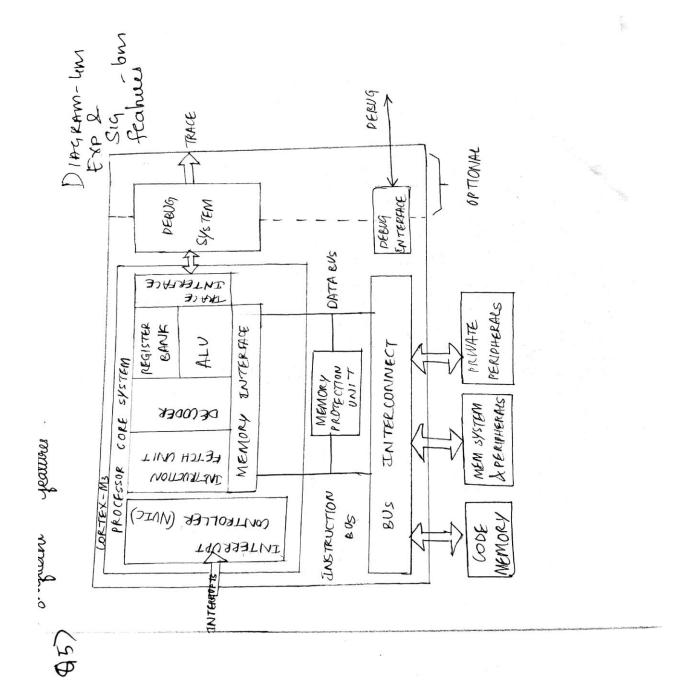

| 3 | Draw and explain the Cort significant features  Drawing of cortex M3 core  Explain  Any 5 significant features                       | ex M3 core and list out its     | 3 M<br>2 M<br>5 M | 10 M |

| 4 | both GPRs and SPRs).  GPRS SPRs                                                                                                      | of Cortex M3 in detail(         | 4 M<br>6M         | 10 M |

| 5 | Explain stack memory of processor with necessary di  Push  pop                                                                       | operations on Cortex M3 agrams. | 5M<br>5 M         | 10 M |

| 6 | List and give details of difficortex (processor family an  4 versions each 2.5Marks                                                  |                                 | 10M               | 10 M |

Exceptions are numbered 1 to 15 for system exceptions and the next 240 for external interrupt inputs (Total 256 entries in vector table)

Most of the exceptions have programmable prioxity, and a few have fixed prioxity.

The value of the current running exception is indicated by the special register Ifse or from the NVIC'S Interrupt Control state Register.

| 141.00              | 2,000              |              |                                                                    |

|---------------------|--------------------|--------------|--------------------------------------------------------------------|

| Exception<br>Number | Exception<br>Type  | Príority.    | Description                                                        |

| I.                  | Reset              | -3(Highest   | Reset                                                              |

| 2                   | NMI                | -2           | Nonmaskable interrupt                                              |

| 3                   | Hardfault          |              | (external NME "1p) All fault condition, if the cooresponding fault |

| 4.                  | MenMarage<br>fault | Programmable | handler is not enabled.                                            |

| 5·                  | Bu fault           | Programmable | Bus evior like Brefitch                                            |

| 6 -                 | Wage fault         | p!           | aboat                                                              |

|                     |                    |              | acees aprocessor.                                                  |

| 7-10 | Resorved                 | NIA           | -                                      |

|------|--------------------------|---------------|----------------------------------------|

| 13   | SVCall                   | 1             | System Service call                    |

| 12.  |                          |               | Debug Monistor.                        |

| 13   | Reserved                 | NA            | ,                                      |

| 14   | PendSV                   | Programmable  | Bygge Pendakle request                 |

| 1:5. | SYSTICK                  | Brogrammake   | for System device<br>System Tick Tinur |

| 16.  | External<br>Interrupt #0 | Programmable  | External Interrupt                     |

| 17.  | External<br>interrupt #1 | Programmable  | External Interrupt                     |

| 7.00 | 6 6 P                    |               |                                        |

| 256  | External Introd          | Peragrammable | External Interrupt.                    |

The processor will need to locate the starting address of the exception handler when an exception is being landled. This information is stored in the vector table.

Exception Vector Table After Paver Up.

| Exception    | c Vector Table | the state of the s |

|--------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | Scuption       | Value (Word Size)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Address      | Number         | MSPInitial Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OX.0.0000000 | -              | P. Avector (Pro gram courter inter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x/0000000k  | 1              | " who stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 0000000008   | 2              | NMI lander starting address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| anomoro e    | 8              | other bandler starting adobus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BALL 000     |                | other rename                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

(a) Love-cost micro-controller: 5) Ind ideally waited for low each amerro-5- Applications 26) controller telich are commonly used in appliances products gram dags to elictrical The many will prown 8-bit & 16-bit market on the market (b) Automotive: to the last very high purformance efficiency & love intercept Lastray allowing it to be used in real - time system in the automotion industry.

H supports & 10 external victorial interrupts

with a built in interrupt controller with

makiting it ideal for highly in teyra ted

L cost - smalline automotive application. Coupled with thumb- a instruction for Bit - Fild manipulation make the CORTEX HS ideal for many communication application. (d) Andus/wal connel: Anthe processor's interrupts for features

Los lating & enhands Foult. Finding Estatum make the another codicide to low the process of the control of the

• These fourthooks are highly carlyinostle to allow the oster.

M3 Proceeds to address a wide rauge of application on the more charles aligned with the system requesiments. . The other M3 che and the integrated components have been spendially designed to meet the requisiments of minimal member into content and too bourse ine Costoc M3 proceeds, based on the ARMUTM arditection posipherally to enable integrated applitutes like internet central, mensey protection and system debug and bace. has a hierarchial standage it integrates the central processed che, called the conside, with consumption

**CUNDAMENTALS**

bit data batt, 32 bit regists bout, and 32 bit moning . The process has a how and and itectuse which wear that - The obtains is a 22 bit misophoceus it has a 32 interface.

system bootober the after M3 phocos has obtioned children that aequire mbe memby un the carre trave and as a result of this, the perfermance of the processes increases because data as it has a repossole instruction bus and rate but This allows influtions and data accesses to take blace at so not affect the instruction fibeline

"F-- To train what (MPU) and it is possible to us

The Obser Ms process includes a number of fixed includes includes a number of fixed broad debugging conferents. These combenents broids depuging operation supports & features, such as breatheants & watchbourts. an esternal cacho if its required

のアスノンツ

<u>х</u>

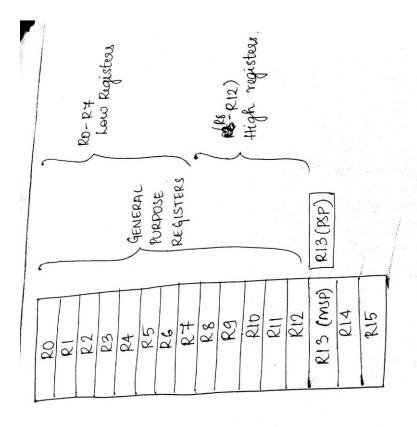

The cortex-M3 processor has registers, RO through RIS, RIS is banked with only one copy of the RIS visible at a time.

Ro-RIZ are 32 bit GPR's for data operations where et RO-RIZ (High rugisters). R8-RIZ (High rugisters). Some of the 16-bit thumb instructions can only access a subset of these registers (it, how registers) in RO-RIZ General Puspose Registers.

213 : Stack Pointes :-

The 2 stack pointers are : i) main stack Pointer Pi] Process Stack Pointer These banked out registers become active only when the processor changes moder. time. The banked out registels are not currently They are banked so that only one is visible at a active and ear mot in thre oraccessible. The wortex-ms contains 2 stad pointers

MSP: Also called as the SP main in arm document. This is the default SP. It is used by the OS as kund, exception handles and all application codes that require priviledged access.

PSP: Also called as SP\_process in ARM controlled \

documentation. This is used by base level application code (when not running an exception handler).

The duality of SP allows & seperate stack memories to be set up when using the register - name &13, one can only access the current SP, the other one is assermaccessible unless one uses special instruction to move to special register from general purpose register (MSR) and move special register to general purpose.

It is used to store the return program counter when a sub-voutine or a function is called when a sub-routine is called, the return address is stored in the link register. It holds the address to return to when a function call completes.

It is the current program address. This register

can be written to control the program flow. SPECIAL REGISTERS:îi] The cortex-M3 processor has a no. of special ngisteu: Program status sigisteri: Provides with metic & logic processing flags (zero flug of carry flag), oricution status & evenent executing intosupt number Introdupt/Exception Mark Registers (PRIMASK 6) FAULTMASK & BASEPRI) :when hard fault happens, the address in is no longer In main manny, but has bun socapped PRIMASK: Disable all Introupts, except the NMI has fault. When has fault occurs, blood of memory had to be suturned from the pagefile insted of physical. FAULTMASK: Disable all interrupts except the MING BASEPRI: Disable all interrupts of specific prior or low priority wal ro Define priviledged status and stack pointer selec CONTROL REGISTER:-

c)

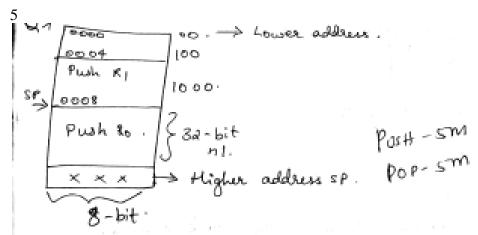

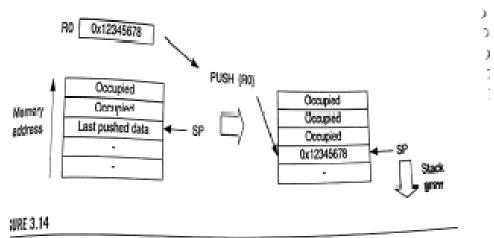

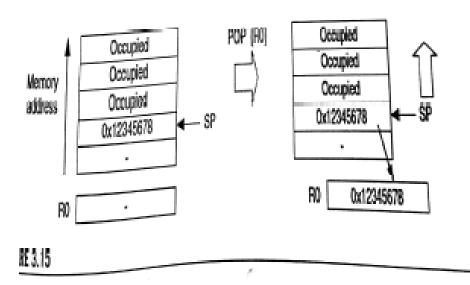

Push : Decrements 3P by 4. POP : Increments 3P by 4.

Push {ROG; RI3=RI3-4, then memory [RI3]=RO POP {ROG; Ro=memory [RI3], then RI3=RI3+4

Multiple registers can be pushed & poped in

Eg: Push. { Ro, Ri} Push { Ro- R7, R12, R83

Costex M3 Contains & Stack pointers (R13). They are banked so that only one is visible at a time.

\* Main Stack Pointer (MSP): The default stack points

\* Process Stack pointer (PSP) - Used by user applications

(code.

|                                |               |               |                 | register.          |

|--------------------------------|---------------|---------------|-----------------|--------------------|

| Greneral-purpose Low Registus. |               |               |                 | the stack Register |

| neral-puopose<br>segistus      | High ragistus | Link segiolis | Program counter | gr (way 8          |

| Name , Ro                      | RIZMSP RISINS | RIG. Link     | R15 Progra      | Fig: Diagram       |

# Basic Operations of the Stack

· 3.6.2 Cortex-M3 Stack Implementation

```

; R0 = X, R1 = Y, R2 = Z

functionl

Subroutine

function1

PUSH

{RO} ; store RO to stack & adjust SP

PUSH

{R1} ; store R1 to stack & adjust SP

{R2} ; store R2 to stack & adjust SP

...; Executing task (RO, R1 and R2

; could be changed)

POP

(R2); restore R2 and SP re-adjusted

POP

{R1} ; restore R1 and SP re-adjusted

POP

{R0} ; restore R0 and SP re-adjusted

- BX

LR ; Return

```

; Back to main program R0 - X, R1 - Y, R2 = Z ... ; next instructions

Main program

### FIGURE 3.12

Stack Operation Basics: Multiple Register Stack Operation.

...; next instructions

...; next instructions

Main program

```

Subroutine

BL function 1

PUSH {RO-R2, LR}; Save registers

; including link register

...; Executing task (RO, R1 and R2

; could be changed)

POP {RO-R2, PC}; Restore registers and

; return

; Back to main program

; RO = X, R1 = Y, R2 = Z

```

rtex-M3 Stack PUSH Implementation.

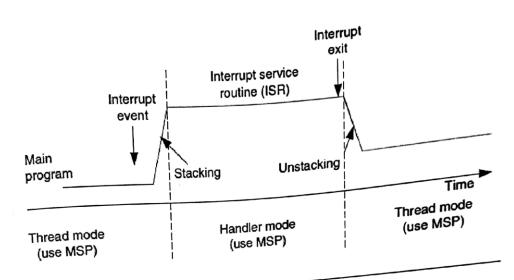

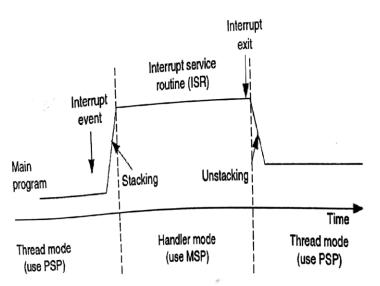

### 3.6.3 The Two-Stack Model in the Cortex-M3

CONTROL[1]=0: Both Thread Level and Handler Use Main Stack. FIGURE 3.16

FIGURE 3.17

CONTROL[1]=1: Thread Level Uses Process Stack and Handler Uses Main Stack.

It is possible to perform read/write operations directly to the MSP and PSP, without any confusion of which R13 you are referring to. Provided that you are in privileged level, you can access MSP and psp values:

```

x = get_MSP(); // Read the value of MSP

__set_MSP(x); // Set the value of MSP

x = get_{PSP()}; // Read the value of PSP

_set_PSP(x); // Set the value of PSP

```

In general, it is not recommended to change current selected SP values in a C function, as the stack memory could be used for storing local variables. To access the SPs in assembly, you can use the MRS

## and MSR instructions:

```

MRS RO, MSP ; Read Main Stack Pointer to RO

MSR MSP, RO; Write RO to Main Stack Pointer

MRS RO, PSP; Read Process Stack Pointer to RO

MSR PSP, RO; Write RO to Process Stack Pointer

```

dro withe Aprople to dest good for high performance open application Pladform The Raprofile is destigned for high and combided septem in which weal time performance is readed. ( ) The M profile is designed for deeply embedded microladroller type Seystom. 5m - Versions 5m - proplet & Arch Versions the cheek. ( ) A profile (ARHVI-A): - Application processes which are designed to harndle to uplen applications such as high and embedded operating systems (OS), there processes "Trequiring the highest processing power , withral many sylle ( ) R profile (dRM v T - R) = Real done, high performance, processors taggeted primarily at the higher and of the th real firme marked - Those applications; such as his and breaking system ghard dine wordsallers

( ) Marofile (Affer of - M): Frozenson targeting low cool application in which processing effecting is important & use one cultications will as industrial located application Enduly real him control system Background of ARM of ARM architecture Arlhetecture And Stecture VS/VSC Architecture v414T A-FV >04Hiculin) Costee AB ARM1136, 1176 717-R (400) EL (1915-1-184 ARM926,946, Example & ARMATONI, Michelectre

966 Intel XScale

water - 40

MI (FPGIF)

¥7-M

Interception - M3

92:0 T Entelstrong ARM