CO

CO<sub>3</sub>

**5M**

**5M**

RB T L2

Marks

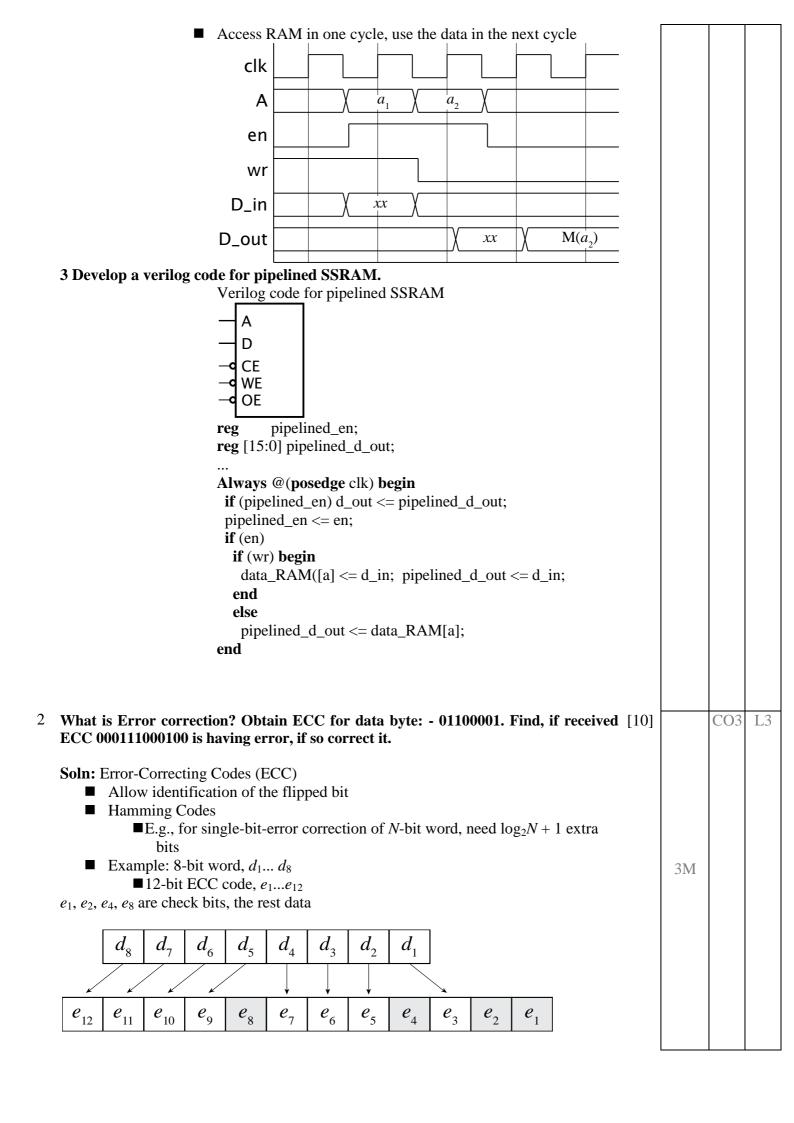

[10]

#### Internal Assesment Test – II/SCHEME AND SOLUTIONS

| Sub:  | DSDV                 | Code: 15EC663 |         | 63         |    |      |    |         |        |          |  |  |

|-------|----------------------|---------------|---------|------------|----|------|----|---------|--------|----------|--|--|

| Date: | / 04 / 2019          | Duration:     | 90 mins | Max Marks: | 50 | Sem: | VI | Branch: | Open E | Elective |  |  |

|       | Answer all Questions |               |         |            |    |      |    |         |        |          |  |  |

|       |                      |               |         |            |    |      |    |         |        | OBE      |  |  |

## 1 Explain synchronous and asynchronous Static RAMs.

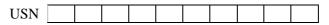

# SOLN:- Asynchronous SRAM

- a. Data stored in 1-bit latch cells

- b. Address decoded to enable a given cell

- c. Usually use active-low control inputs

- d.Not available as components in ASICs or FPGAs

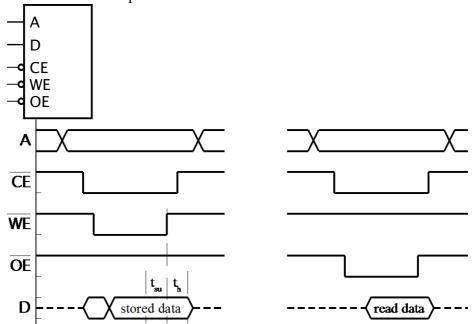

#### Synchronous SRAM

- a. Clocked storage registers for inputs

- b. address, data and control inputs

- c. stored on a clock edge

- d. held for read/write cycle

#### Flow-through SSRAM

no register on data output

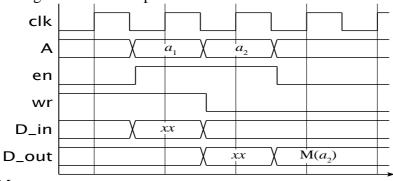

#### Pipelined SSRAM

- Data output also has a register

- More suitable for high-speed systems

4M3M

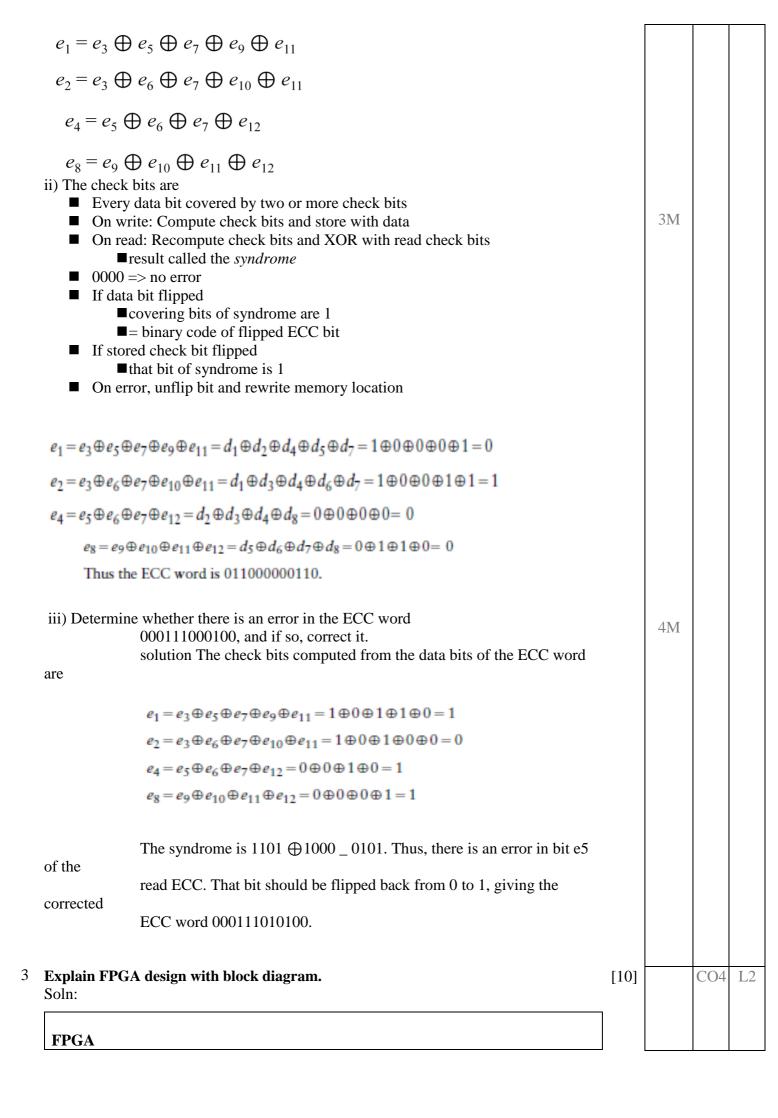

The basic elements within logic blocks are small 1-bit-wide asynchronous RAMs called lookup tables (LUTs). The LUT address inputs are connected to the inputs of the logic block. The content of an LUT determines the values of a Boolean function of the inputs. By programming the LUT content differently, we can implement any Boolean function of the inputs. The logic blocks also contain one or more flipflops and various multiplexers and other logic for selecting data sources and for connecting data to adjacent logic blocks. The logic block contains two such slices, together with a small amount of additional logic. Each slice consists of two 4-input LUTs, each of which can be programmed to implement any function of the four inputs. The carry and control logic consists of circuitry to combine the LUT outputs, an XOR gate and an AND gate for implementing adders and multipliers, as well as multiplexers that can be used to implement a fast carry chain.

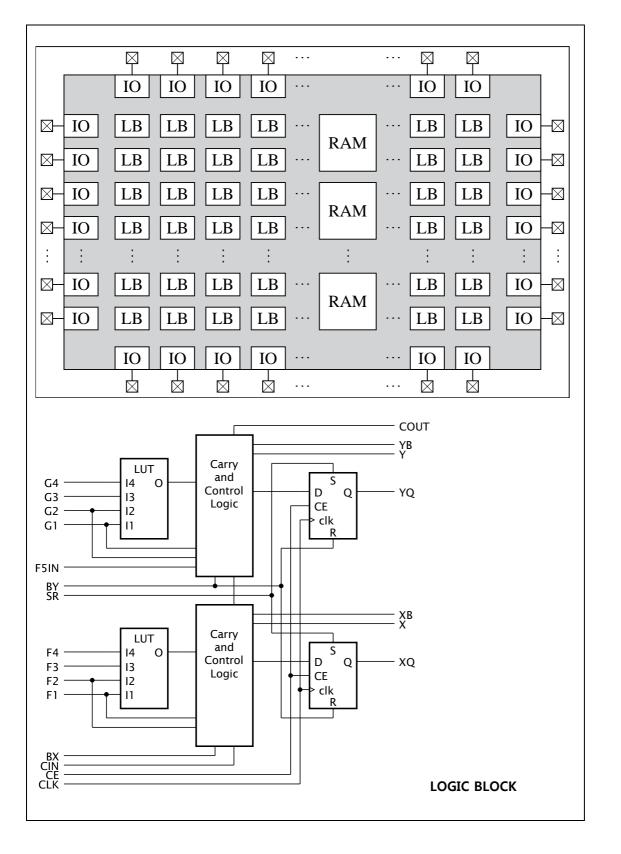

The I/O block of an FPGA is typically organized as shown. The select inputs of the multiplexers are programmed to control whether the output is registered or combinational. The top flip-flop and multiplexer control the high-impedance state of the tristate driver that drives the pin as an output, and the middle flip-flop and multiplexer drive the output value. The output driver is programmable, allowing selection of logic levels (regular 5V TTL, low voltage TTL, or others) and control of the slew rate, that is, rate of voltage change at the output.

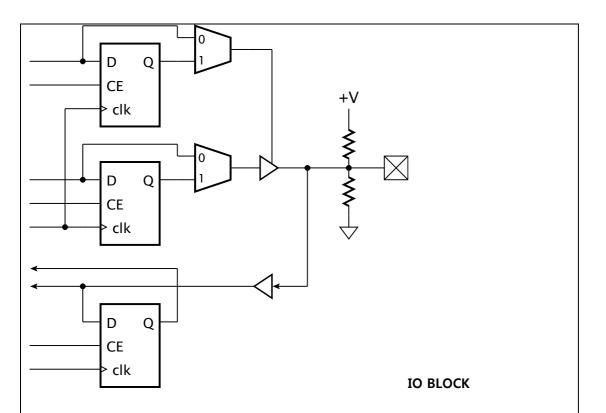

4 Explain the working of SAR Based ADC with example.

[10] CO4 L3

3M

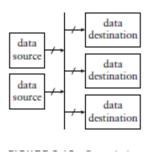

- Use multiplexer(s) to select among data sources

- Can partition to aid placement on chip

#### Multiplexed buses

8.3 Parallel

### Distributed multiplexed bus

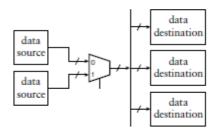

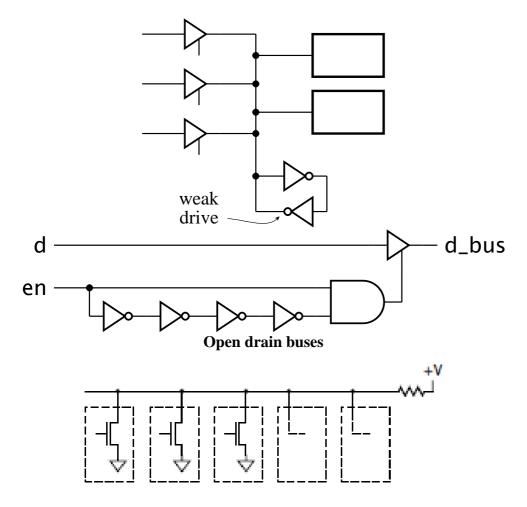

- Use tristate drivers for data sources

- Can "turn-off" (Hi-Z) when not supplying data

- Simplified bus wiring

#### **Tristate buses**

2M

2M

2M

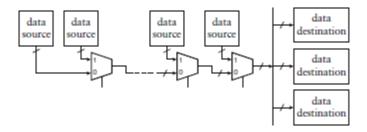

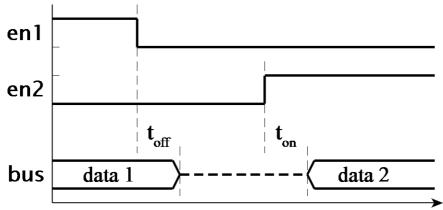

- Floating bus can cause spurious switching

- Use pull-up resistors or weak keepers

- Need to avoid driver contention

- Dead cycle between turn-off and turn-on

- Or delayed enable

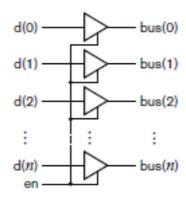

- Bus is 0 if any driver pulls it low

- If all drivers are off, bus is pulled high

- Wired-AND

- Can also use open-collector drivers