## VTU QP SOLUTION- 2018-19 May-AEC-17EE34

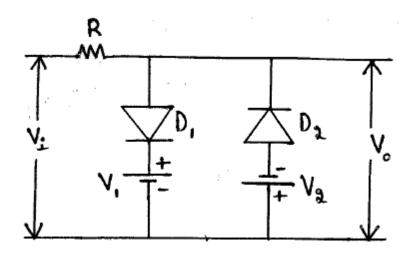

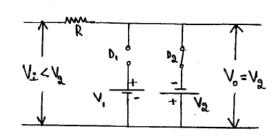

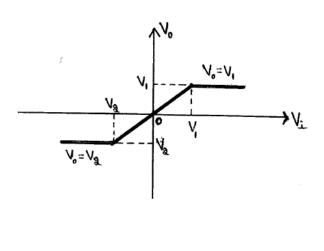

1a. Draw a double ended clipper circuit and explain its working principle with transfer characteristics.

During the half Cycle

\* Diode Da is always neverse bias & acts as open Ckt.

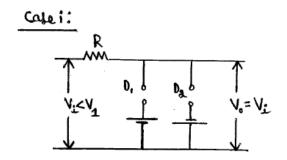

Case: When  $V: < V_1$ , diode D, is hereafte big & acts as open (kt. Thus of  $V_0 = V_1$ )

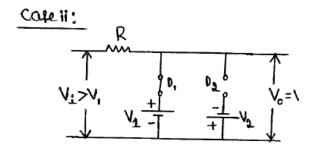

Case ii: When  $V_1 > V_1$ , diode  $D_1$  is followed bias it att as Short (kt. Thus of  $V_0 = V_1$

During - ve half cycle

\* Diode D. is always neverthe bias & acts as open CKt.

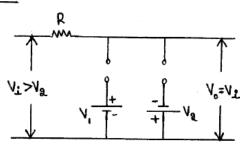

Caki: When Vi>Vg, diode Dz is Trenebyte bias & alts as open (kt.

Thus of Vo=Vi

Case ii: When  $V_1 < V_2$ , diode  $D_2$  is founded bing a acts as Short UKE.

Thus olp Vo=V2

## Case:

## Cate ii:

## Ilo Wanefarms:

## Thansfer Characteristics:

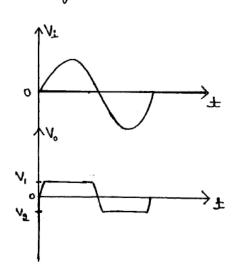

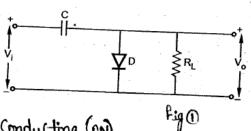

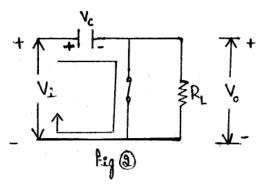

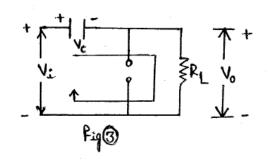

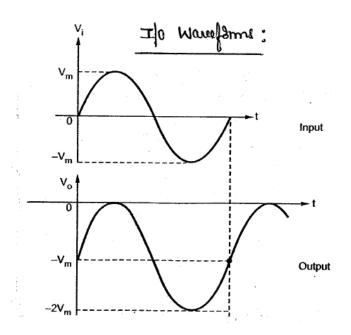

1b. Draw and explain the working of clamper circuit which clamps the positive peak of a signal to zero.

\* A-ve clamper is a CKt which addr -ve DC restage to the Ilp Signal.

Step 1:

Find the Capacita voltage when the diode is Conducting (ON).

\* During the half cycle, diode 'D' is followed biased & conducts. Now capacita 'C' changes with the polarity as Shown in Fig 3.

Applying KVL to the CKt, we get

Now Vi= Vm

$$V_c = V_m \longrightarrow 0$$

Step 2:-

Find the ofp voltage When would is UFF.

\* During -ve half cycle, diode 'D' is hereoffe biased a acts as open Circuit & its equivalent CK+ is Shown in Fig 3

Applying KVL to the (Kt, we get

$$V_{1} - V_{c} - V_{0} = 0$$

$$V_{2} - V_{c} \longrightarrow 3$$

Substituting ear 1) in eq 12, we get

old roltages:

| Pa Vi | Vo=Vi-Vm          |

|-------|-------------------|

| 0     | 10=-1m            |

| Vm    | V <sub>0</sub> =0 |

| -Vm   | Nº = -31/w        |

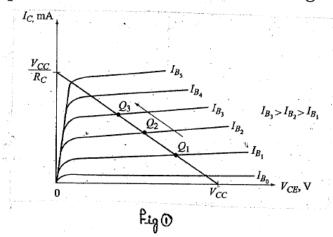

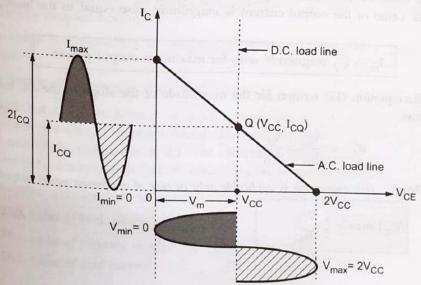

1c. With suitable graph, explain the significance of operating point.

WKT the load line is constructed on the output characteristics.

## \* Effect of IB :-

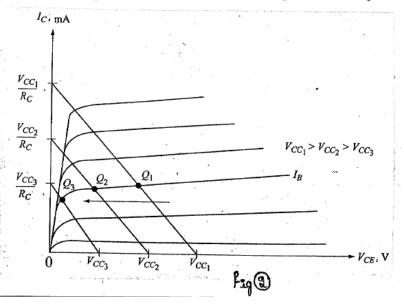

If the value of  $I_B$  is changed by varying the value of  $R_B$ , the Q-point moves up or down the load-line as shown in figure 1.

## \* Effect of Vcc :-

If  $R_c$  is **fixed** and  $V_{cc}$  varied, the load line shifts as shown in figure 2. Now the **Q-point varies horizontally** on the  $I_{BO}$  line.

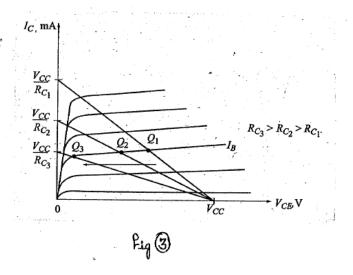

## \* Effect of Rc:

If Vcc is kept constant and Rc is changed, keeping base current I<sub>B</sub> fixed, the Q-point moves to the left into saturation as shown in figure 3.

2a. Derive the expression for stability factor for fixed bias circuit, with respect  $I_{co}$ ,  $V_{BE}$  and  $\beta$ .

I) For fixed-bias cht, the base current is given by  $\text{IB} = \frac{\text{Vcc-VBE}}{\text{RB}} \rightarrow \text{1} .$

Differentiating eq. 1 Nov to  $\underline{Ic}$ , we get  $\underline{dIB} = 0 \rightarrow 2$ .

Sub Eq 3 in istability factor equation

$$S = \frac{(1+\beta)}{1-\beta(\frac{dIB}{dIC})} = \frac{(1+\beta)}{1-\beta(0)} = \frac{1+\beta}{1}$$

a)

$$S' = S(NBE) = \frac{dIc}{dNBE}$$

$$\mathbb{IB} = \frac{V_{CC} - V_{BE}}{R_B} \longrightarrow \mathbb{O}.$$

$$M \cdot K \cdot T$$

Ic =  $\beta IB \rightarrow 2$

bub eq 1) in Eq 3 (Is value)

$$Ic = \beta \left( \frac{V_{CC} - V_{BE}}{R_B} \right)$$

differentiating eq 3 N.7. to VBE, we get

$$\frac{dIc}{dVBE} = 0 - (1) \frac{B}{RB} = -\frac{B}{RB}$$

W.K-T

$\beta = \frac{1c}{1c}$

IB = IC

$$s' = \frac{dIC}{dVBE} = \frac{-B}{RB}.$$

3)

$$S'' = S(\beta) = \frac{dIC}{d\beta} = \frac{\Delta IC}{\Delta \beta}$$

$$\Im \beta = \sqrt{\frac{CC - NBE}{RB}} - \Omega.$$

$$\left(\frac{\mathcal{I}c}{\beta}\right) = \frac{\sqrt{cc - 1/86}}{\sqrt{8}}$$

$$\therefore \quad \Im c = \beta \left( \frac{\kappa_B}{\Lambda cc - \Lambda e^E} \right) \quad \Rightarrow \mathfrak{D} \quad .$$

$$W \cdot K \cdot T$$

$S(\beta) = \Delta JC \rightarrow 3$ .

At temperature

$$T_1$$

,  $\beta = \beta_1$ ,  $T_C = J_{C_1}$

At temperature  $T_2$ ,  $\beta = \beta_2$ ,  $J_C = J_{C_2}$

Then, Eq @ can be written as

$$\mathcal{I}_{C_1} = \beta_1 \left( \frac{V_{CC} - VBE}{RB} \right) \rightarrow (A)$$

$$\text{My } \mathcal{J}_{C_2} = \beta_2 \left( \frac{\text{VCC} - \text{VBE}}{\text{RB}} \right) \longrightarrow \text{ (5)} .$$

$$\frac{\mathcal{I}_{C_2}}{\mathcal{I}_{C_1}} = \frac{\beta_2(1)}{\beta_1(1)} \rightarrow 0$$

Subtracting eq. 6 by 1 on both sides.

$$\frac{\mathbf{I}_{c_2}}{\mathbf{I}_{c_1}} - \mathbf{1} = \frac{\beta_2}{\beta_1} - \mathbf{1}$$

$$\frac{\mathcal{I}_{c_2} - \mathcal{I}_{c_1}}{\mathcal{I}_{c_1}} = \frac{\beta_2 - \beta_1}{\beta_1}$$

$$\frac{\Delta \text{ Ic}}{\text{Ic}_1} = \frac{\Delta \beta}{\beta_1}$$

$$\frac{\Delta C}{\Delta \beta} = \frac{C1}{\beta_1}$$

$$\Delta I_{C} = I_{C_{2}} - I_{C_{1}}$$

$$\Delta \beta = \beta_{2} - \beta_{1}$$

b. A voltage divider biased circuit has  $R_1=39k\Omega$ ,  $R_2=82k\Omega$ ,  $R_c=3.3k\Omega$ ,  $R_E=1k\Omega$  and  $V_{CC}=18V$ . The Silicon transistor used has  $\beta=120$ . Find Q-point and stability factor.

(08 Marks)

$$R = 39KA$$

$R = 82KA$

$R = 33KA$

$R_0 = 190$

$R_0$

$R$

$$V_{T} = \left(\frac{R_{2}}{R_{1} + R_{2}}\right) V_{CC} = 12 \cdot 19 V \cdot \left| k_{B} = \frac{R_{1}R_{2}}{R_{1} + R_{2}} = 26 \cdot 43 K R \right|$$

$$k_{VL} + 6 \log O \rightarrow V_{T} - \frac{1}{2} R_{0} - V_{0E} - \frac{1}{E} R_{E} = 0$$

$$V_{T} - I_{0} k_{3} - V_{0E} - (1+\beta) k_{E} I_{0} = 0$$

$$I_{1} = \frac{V_{T} - V_{0E}}{R_{0} + (1+\beta) k_{E}} = \frac{11.49}{24.147430}$$

$$I_{3} = \frac{11.49}{R_{0} + (1+\beta) k_{E}} = \frac{11.49}{24.147430}$$

$$I_{4} = \frac{11.49}{R_{0} + (1+\beta) k_{E}} = \frac{11.49}{24.147430}$$

$$I_{5} = \frac{11.49}{R_{0} + (1+\beta) k_{E}} = \frac{11.49}{24.147430}$$

$$I_{6} = \frac{11.49}{R_{0} + (1+\beta) k_{E}} = \frac{11.49}{24.147430}$$

$$I_{7} = \frac{11.49}{R_{0} + (1+\beta) k_{E}} = \frac{11.49}{R_{0} + (1+\beta) k_{E}}$$

$$I_{7} = \frac{11.49}{R_{0} + (1+\beta) k_{E}} = \frac{11.49}{R_{0} + (1+\beta) k_{E}}$$

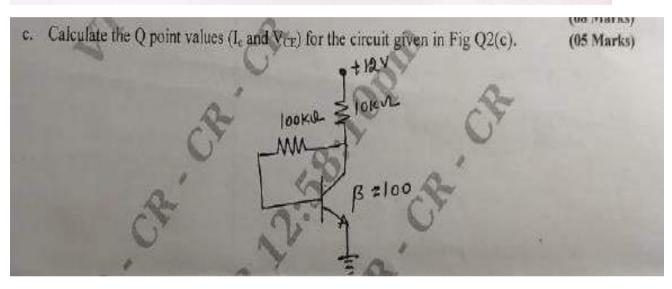

$$\frac{I_{0}}{R_{B} + (I+\beta)R_{c}} = \frac{12-0.7}{100 \times 10^{3} + (I+100)(10 \times 10^{3})} = \frac{10.18 MA}{100 \times 10^{3} + (I+100)(10 \times 10^{3})}$$

$$f_{c} = \beta I_{n} = 100 \times 10.18 MA = 1.018 MA$$

$$V_{CE} = V_{CC} - (I_{B} + I_{C})R_{C} = 1.7182 V$$

### 3a. State and prove Miller's theorem.

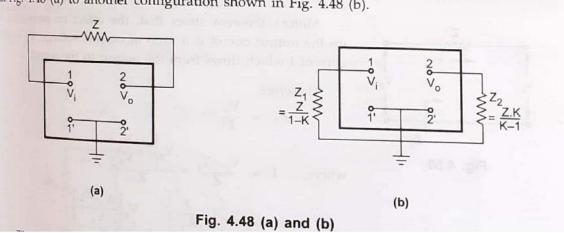

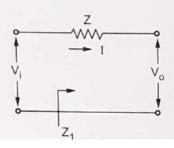

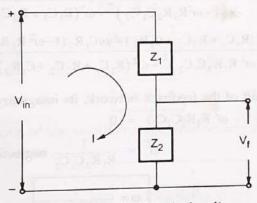

In general, the Miller theorem is used for converting any circuit having configuration of Fig. 4.48 (a) to another configuration shown in Fig. 4.48 (b).

The Fig. 4.48 shows that, if Z is the impedance connected between two nodes, node 1 and node 2, it can be replaced by two separate impedances  $Z_1$  and  $Z_2$ ; where  $Z_1$  is The V and V.

The  $V_i$  and  $V_o$  are the voltages at the node 1 and node 2 respectively. The values of not necessary to know the values of  $V_i$  and  $V_o$  to calculate the values of  $Z_1$  and  $Z_2$ .

The values of impedances Z1 and Z2 are given as

$$Z_1 = \frac{Z}{1 - K}$$

and

$$Z_2 = \frac{Z \cdot K}{K - 1}$$

## 4.5.2 Proof of Miller's Theorem

Miller's theorem states that, the effect of resistance Z  $_{00}$  the input circuit is a ratio of input voltage  $V_i$  to the current] which flows from the input to the output.

Therefore,

$$Z_1 = \frac{V_i}{I}$$

Fig. 4.49

$$I = \frac{V_i - V_o}{Z} = \frac{V_i \left[1 - \frac{V_o}{V_i}\right]}{Z}$$

$$= \frac{V_i [1 - A_v]}{Z}$$

$$\therefore Z_1 = \frac{V_i}{I} = \frac{Z}{1 - A_v} = \frac{Z}{1 - K} \quad \because \quad \frac{V_o}{V_i} = A_v = K$$

Miller's theorem states that, the effect of resistance on the output circuit is a ratio of output voltage  $V_o$  to the current I which flows from the output to the input.

Therefore,

$$Z_2 = \frac{V_o}{I}$$

where,

$$I = \frac{V_o - V_i}{Z} = \frac{V_o \left[1 - \frac{V_i}{V_o}\right]}{Z}$$

$$= \frac{V_o \left[1 - \frac{1}{A_v}\right]}{Z} = \frac{V_o \left[\frac{A_v - 1}{A_v}\right]}{Z}$$

$$\therefore Z_2 = \frac{V_o}{I} = \frac{Z}{\left[\frac{A_v - 1}{A_v}\right]} = \frac{ZK}{K - I} \quad \because \quad \frac{V_o}{V_i} = A_v = K$$

3b. Starting from fundamentals define h-parameters and obtain h-parameter equivalent circuit of common emitter configuration.

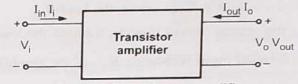

Let us consider transistor amplifier as a black box as shown in the Fig. 4.9.

Fig. 4.9 Transistor amplifier

Here, I; : is the input current to the amplifier

Vi : is the input voltage to the amplifier

Io: is the output current of the amplifier and

Vo : is the output voltage of the amplifier

As we know transistor is a current operated device, input current is an independent variable. The input current,  $I_i$  and output voltage  $V_o$  devices the input voltage  $V_i$  as well as the output current  $I_o$ . Hence input voltage  $V_i$  and output current  $I_o$  are the dependent variables, whereas input current  $I_i$  and output voltage  $V_o$  are independent variables. Thus we can write

$$V_{i} = f_{1} (I_{i}, V_{o}) \qquad \dots (1)$$

$$I_{o} = f_{2} (I_{i}, V_{o}) \qquad \dots (2)$$

This can be written in the equation form as follows

$$V_i = h_{11} I_i + h_{12} V_o$$

$$I_o = h_{21} I_i + h_{22} V_o$$

The above equations can also be written using alphabetic notations,

$$V_i = h_i \cdot I_i + h_r \cdot V_o$$

$$I_o = h_f \cdot I_i + h_o \cdot V_o$$

## Definitions of h-parameter

The parameters in the above equation are defined as follows:

$\left. h_{11} = \frac{V_i}{I_i} \right|_{V_0=0}$  = Input resistance with output short-circuited, in ohms.

$h_{12} = \frac{V_1}{V_0}\Big|_{I_1=0}$  = Fraction of output voltage at input with input open circuited.

This parameter is ratio of similar quantities, hence unitless

$h_{21} = \frac{I_0}{I_1}\Big|_{V_0=0}$  = Forward current transfer ratio or current gain with output

short circuited.

This parameter is a ratio of similar quantities, hence unitless.

$h_{22} = \frac{I_o}{V_o}\Big|_{I_{i=0}}$  = Output admittance with input open-circuited, in mhos.

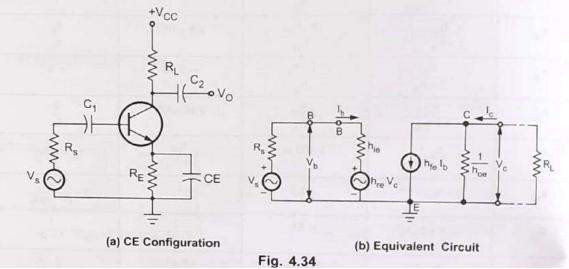

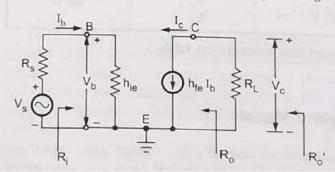

## 4.4.1 CE Configuration

Let us consider the common emitter amplifier and it's h-parameter equivalent circuit for the amplifier, as shown in the Fig. 4.34.

Since  $1/h_{oe}$  is in parallel with  $R_L$  and  $R_C$  if  $1/h_{oe} >> R_L \parallel R_C$ , then  $h_{oe}$  may be neglected. If we neglect  $h_{oe}$ , the collector current  $I_c$  is given by  $I_c = h_{fe} I_b$ . Under these conditions the magnitude of the voltage of the generator in the emitter circuit is,

$$h_{re} \mid V_{ce} \mid \ = \ h_{re} \ I_{c} \ (R_{L} \parallel R_{C}) = h_{re} h_{fe} \ I_{b} \ (R_{L} \parallel R_{C})$$

Since  $h_{re}h_{fe} \approx 0.01$ , this voltage may be neglected in comparison with the  $h_{ie}I_{b}$  drop

across  $h_{ie}$ , provided that  $R_L \parallel R_C$  is not too large. We therefore conclude that if the load resistance  $R_L \parallel R_C$  is small, it is possible to neglect the parameters  $h_{re}$  and  $h_{oe}$  in the h-parameter equivalent circuit. Fig. 4.35 shows the approximate h-parameter equivalent circuit.

3c. Compare the characteristics of CB,CE and CC configurations.

factor

Current gain

Voltage gain

**Applications**

8.

9.

10.

4.7 Comparison of Transistor Configurations

#### Sr.No. Characteristic Common Base Common Collector Common Emitter 1. Input resistance Very low (20 Ω) Low $(1 k\Omega)$ High (500 kΩ) 2. Output resistance Very high (1MΩ) High (40 $k\Omega$ ) Low (50 Ω) 3 Input current $I_B$ IB 4. Output current $I_{C}$ I, 5. Input voltage applied Emitter and Base Base and Emitter Base and Collector between 6. Output voltage taken Collector and Base Emitter and Collector Collector and Emitter between 7. Current amplification

4a. Derive an expression for input impedance, voltage gain, current gain and output impedance of emitter follower circuit using h-parameter model for transistor.

Less than unity

Medium

As a input stage of

multistage amplifier

b. For the transistor connected in CE configuration, determine A<sub>v</sub>, A<sub>I</sub>, R<sub>I</sub> and R<sub>o</sub> using complete hybrid equivalent model.

Given R<sub>L</sub> = R<sub>o</sub> = IkΩ h<sub>ie</sub> = 1kΩ, h<sub>ee</sub> = 2×10<sup>-4</sup>, h<sub>fe</sub> = 100 and h<sub>oe</sub> = 20μA/V

c. A transistor in CE mode has be parameters.

High

(20 to few hundreds)

Medium

For audio signal am-

plification

High

(20 to few hundreds)

For impedance matching

$$A_{1} = \frac{-h_{fe}}{1 + h_{oe}R_{L}} = \frac{-100}{1 + 20 \times 10^{-6} \times 1 \times 10^{3}}$$

Input resistance

$$R_{i} = h_{ie} + h_{re}A_{i}R_{L} = 1000 + 2 \times 10^{-4} \times -98 \times 1000$$

$$= 980.4 \Omega$$

$$A_{v} = \frac{A_{i}R_{L}}{R_{i}} = \frac{-98 \times 1000}{1000}$$

$$= -98$$

$$Y_{0} = h_{0e} - \frac{h_{fe}h_{re}}{h_{ie} + R_{S}} = 20 \times 10^{-6} - \frac{100 \times 2 \times 10^{-4}}{1000 + 1000}$$

$$= 1.9 \times 10^{-5}$$

## Output resistance

$$R_o = \frac{1}{Y_o} = \frac{1}{1.9 \times 10^{-5}} = 52.64 \text{ kg}$$

$n_{\text{fe}} = 20 \, \text{m}_{\text{fe}} = 100 \text{ and } h_{\text{od}} = 20 \, \mu\text{A/V}$ c. A transistor in CE mode has h-parameters (08 Marks)  $h_{ie}=1.1k\Omega v$   $h_{ie}=2\times10^4,~h_{ie}=100$  and  $h_{oe}=25\mu A/V.$  Determine the equivalent CB (04 Marks)

$$\rightarrow h_{fb} (1+h_{fe}) = -h_{fe}$$

$$\rightarrow h_{fb} = -h_{fe} = -0.99$$

$$1+h_{fc} = -0.99$$

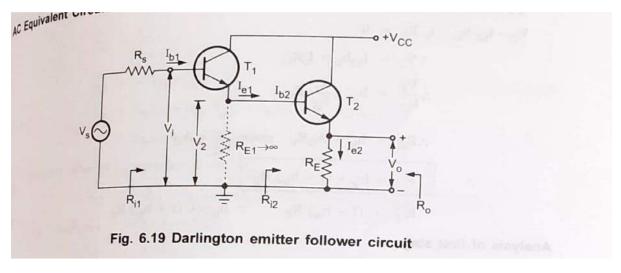

5a. Draw the circuit of Darlington emitter follower. Derive the expression for current gain using its ac equivalent circuit.

Assume that the load resistance  $R_L$  is such that  $R_L$   $h_{oe} < 0.1$ , therefore we can use approximate analysis method for analysing second stage.

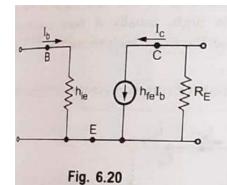

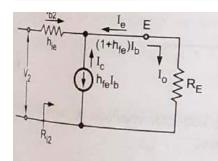

Fig. 6.20 shows approximate h-parameter (AC) equivalent circuit for common emitter configuration.

The same circuit can be redrawn by making collector common to have approximate h-parameter equivalent circuit for common collector configuration as shown in Fig. 6.21.

Fig. 6.21

# alysis of second stage:

$$A_{i2} = \frac{I_o}{I_b} = -\frac{I_e}{I_b} = \frac{I_b + h_{fe} I_b}{I_b} = \frac{I_b (1 + h_{fe})}{I_b}$$

$$A_{i2} = 1 + h_{fe}$$

$$A_{i1} = \frac{I_{b2}}{I_{b1}}$$

$$A_{i1} = \frac{I_{e1}}{I_{b1}}$$

$$I_{e1} = -(I_{b1} + I_{c1})$$

$$I_{c1} = h_{fe}I_{b1} + h_{oe} V_{ce1} = h_{fe}I_{b1} + h_{oe} (-I_{b2} R_{L1})$$

$$= h_{fe}I_{b1} + h_{oe} I_{e1} R_{L1}$$

$$(4)$$

- 5b. What are the advantages of negative feedback amplifiers. Explain briefly.

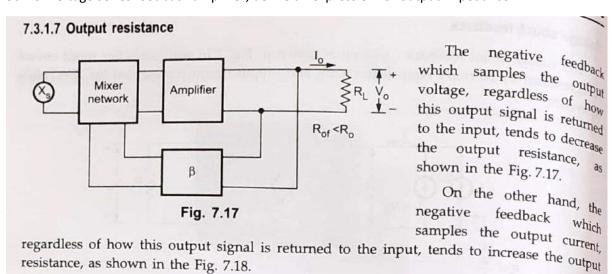

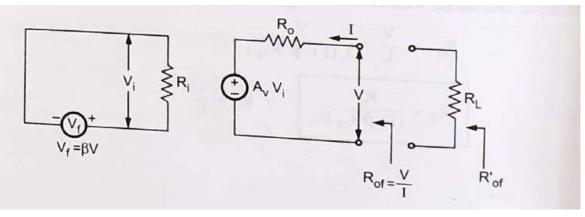

- 5c. For voltage series feedback amplifier, derive an expression for output impedance.

Mixer network Amplifier R<sub>of</sub> >R<sub>o</sub>

Now, we see the effect of negative feedback on output resistance in different topologies (ways) of introducing negative feedback and obtain  $R_{\rm of}$  quantitatively.

## Voltage series feedback

In this topology, the output resistance can be measured by shorting the input source  $V_{\rm s}$  = 0 and looking into the output terminals with  $R_{\rm L}$  disconnected, as shown in the

Applying KVL to the output side we get,

$$A_{v}V_{i} + IR_{o} - V = 0$$

$$I = \frac{V - A_{v}V_{i}}{R_{o}}$$

The input voltage is given as

$$V_i = -V_f = -\beta V \quad \because V_s = 0 \qquad ... (33)$$

The input voltage is given as

$$I = \frac{V + A_v \beta V}{R_o}$$

$$I = \frac{V + A_v \beta V}{R_o}$$

$$= \frac{V (1 + \beta A_v)}{R_o}$$

$$R_{of} = \frac{V}{I} = \frac{R_o}{(1 + \beta A_v)} \qquad ... (34)$$

Note: Here

$$A_v$$

is the open loop voltage gain without taking  $R_L$  in account,

$$R_{of}' = R_{of} \parallel R_L$$

$$= \frac{R_{of} \times R_L}{R_{of} + R_L} = \frac{\left(\frac{R_o}{1 + \beta A_v}\right) \times R_L}{\frac{R_o}{(1 + \beta A_v)} + R_L}$$

$$= \frac{R_o R_L}{R_o + R_L (1 + \beta A_v)} = \frac{R_o R_L}{R_o + R_L + \beta A_v R_L}$$

Dividing numerator and denominator by (Ro + RL)we get

$$R'_{of} = \frac{\frac{R_o R_L}{R_o + R_L}}{1 + \frac{\beta A_v R_L}{R_o + R_L}}$$

$$R'_{of} = \frac{R'_{L}}{1 + \beta A_{v}} \qquad \therefore R'_{o} = \frac{R_{o}R_{L}}{R_{o} + R_{L}} \text{ and } A_{v} = \frac{A_{v}R_{L}}{R_{o} + R_{L}}$$

Note: Here  $A_v$  is the open loop voltage gain taking  $R_T$  into account.

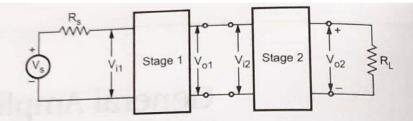

6a. Explain the need of cascading amplifier. Draw and explain the block diagram of two stage cascade amplifier. or multistage amplifiers.

## 6.1.1 Need for Cascading

For faithful amplification amplifier should have desired voltage gain, current gain and it should match its input impedance with the source and output impedance with the load. Many times these primary requirements of the amplifier cannot be achieved with single stage amplifier, because of the limitation of the transistor/FET parameters. In such situations more than one amplifier stages are cascaded such that input and output stages provide impedance matching requirements with some amplification and remaining middle

In short we can say that,

- · When the amplification of a single stage amplifier is not sufficient, or,

- · When the input or output impedance is not of the correct magnitude, for a particular application two or more amplifier stages are connected, in cascade. Such amplifier, with two or more stages is also known as multistage amplifier.

or a multistage amplifier.

## 6.2 Cascade Connections

# 6.2.1 Two Stage Cascaded Amplifier

Fig. 6.1 shows the block diagram of two stage cascaded amplifier. These stages are stage.

Stage.

Fig. 6.1 Block diagram of two stage cascade amplifier

As shown in the Fig. 6.1  $V_{i1}$  is the input of the first stage and  $V_{o2}$  is the output of the second stage. Therefore  $V_{o2}/V_{i1}$  is the overall voltage gain of two stage amplifier and it can be given as,

$$A_V = \frac{V_{o2}}{V_{i1}}$$

$$= \frac{V_{o2}}{V_{i2}} \frac{V_{i2}}{V_{i1}}$$

We know that,

$$V_{o1} = V_{i2}$$

$$\therefore A_V = \frac{V_{o2}}{V_{i2}} \frac{V_{o1}}{V_{i1}}$$

$$= A_{V2} A_{V1}$$

So that, we can say the voltage gain of multistage amplifier is the product of voltage gains of the individual stages.

In the block diagram of two-stage amplifier we have not considered the biasing arrangements for simplicity. Now, with primary understanding we will see the two stage amplifier with biasing arrangements and we will analyse its performance with the help of h-parameters.

b. A given amplifier arrangement has the following voltage gains  $A_{v_1} = 10$ ,  $A_{v_2} = 20$  and  $A_{v_3} = 40$ . Calculate the overall voltage gain and determine the total voltage gain in dBs.

$$Av = Av_1 \cdot Av_2 \cdot Av_3$$

$$= 10 * 20 * 40 = $000$$

$$Av_1 (dB) = 20 \log 10 = 20$$

$$Av_2 (dB) = 20 \log 20 = 26$$

$$Av_3 (dB) = 20 \log 40 = 32$$

c. An amplifier with negative feedback has a voltage gain of 120. It is found that without feedback an input signal of 60mV is required to produce a particular output, whereas with feedback the input signal must be 0.5V to get the same output. Find voltage gain (A<sub>V</sub>) and β of the amplifier.

(06 Marks)

Given

$$Avf = 120$$

$$Av = \frac{V_0}{V_s} = \frac{V_0}{60 \text{ mV}}$$

and  $AVf = \frac{V_0}{0.5} \rightarrow V_0 = 0.5 \times 120 = 60V$ .

$$AV = \frac{V_0}{V_s} = \frac{60}{60 \text{ mV}} = 1000$$

From  $Avf = \frac{Av}{HAVB} \rightarrow \boxed{\beta = 0.00737}$

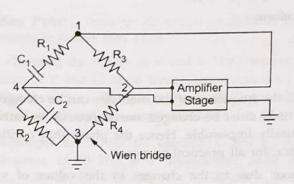

7a. Derive an expression for frequency of oscillations of Wien Bridge oscillator.

### 9.6 Wien Bridge Oscillator

Generally in an oscillator, amplifier stage introduces 180° phase shift and feedback network introduces additional 180° phase shift, to obtain a phase shift of 360° ( $2\pi$  radians) around a loop. This is required condition for any oscillator. But Wien bridge oscillator uses a noninverting amplifier and hence does not provide any phase shift during amplifier stage. As total phase shift required is  $0^\circ$  or  $2 n\pi$  radians, in Wien bridge type no phase shift is necessary through feedback. Thus the total phase shift around a loop is  $0^\circ$ . Let us study the basic version of the Wien bridge oscillator and its analysis.

Fig. 9.12 Basic circuit of Wien bridge oscillator

Fig. 9.13 Feedback network of Wien bridge oscillator

A basic Wien bridge used in this oscillator and an amplifier stage is shown in the Fig. 9.12.

The output of the amplifier is applied between the terminals 1 and 3, which is the input to the feedback network. While the amplifier input is supplied from the diagonal terminals 2 and 4, which is the output from the feedback network. Thus amplifier supplied its own input through the Wien bridge as a feedback network.

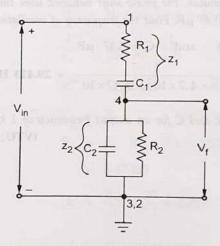

The two arms of the bridge, namely R<sub>1</sub>, C<sub>1</sub> in series and R<sub>2</sub>, C<sub>2</sub> in parallel are called **frequency** sensitive arms. This is because the components of these two arms decide the frequency of the oscillator. Let us find out the gain of the feedback network. As seen earlier input V<sub>in</sub> to the feedback network is

between is 1 and 3 while output  $V_f$  of the feedback network is between 2 and 4. This is shown in the Fig. 9.13. Such a feedback network is called **lead-lag network**. This is because at very low frequencies it acts like a lead while at very high frequencies it acts like lag network.

## 9.6.1 Derivation for Frequency of Oscillations

Now from the Fig. 9.13, as shown,

$$Z_{1} = R_{1} + \frac{1}{j\omega C_{1}} = \frac{1 + j\omega R_{1} C_{1}}{j\omega C_{1}}$$

$$Z_{2} = R_{2} \parallel \frac{1}{j\omega C_{2}} = \frac{R_{2} \times \frac{1}{j\omega C_{2}}}{R_{2} + \frac{1}{j\omega C_{2}}}$$

$$= \frac{R_{2}}{1 + j\omega R_{2} C_{2}} \qquad \dots (1)$$

Replacing  $j\omega = s$ ,

$$Z_1 = \frac{1 + s R_1 C_1}{s C_1}$$

and

$$Z_2 = \frac{R_2}{1 + s R_2 C_2}$$

Fig. 9.14 Simplified circuit

$$I = \frac{I}{Z_1 + Z_2}$$

$$V_f = I Z_2$$

$$V_f = \frac{V_{in} Z_2}{Z_1 + Z_2}$$

$$\beta = \frac{V_f}{V_{in}} = \frac{Z_2}{Z_1 + Z_2}$$

Substituting the values of  $Z_1$  and  $Z_2$ ,

$$\beta = \frac{\left[\frac{R_2}{1+sR_2C_2}\right]}{\left[\frac{1+sR_1C_1}{sC_1}\right] + \left[\frac{R_2}{1+sR_2C_2}\right]}$$

$$\beta = \frac{sC_1R_2}{(1+sR_1C_1)(1+sR_2C_2) + sC_1R_2}$$

$$= \frac{sC_1R_2}{1+s(R_1C_1 + R_2C_2) + s^2R_1R_2C_1C_2 + sC_1R_2}$$

$$= \frac{sC_1R_1}{1+s(R_1C_1 + R_2C_2 + C_1R_2) + s^2R_1R_2C_1C_2}$$

Replacing s by

$$j\omega$$

,  $s^2$ ,  $= -\omega^2$

$$\therefore \beta = \frac{j\omega C_1 R_2}{(1-\omega^2 R_1 R_2 C_1 C_2) + j\omega (R_1 C_1 + R_2 C_2 + C_1 R_2)} \dots (3)$$

Rationalising the expression,

$$\beta = \frac{j\omega C_1 R_2 \left[ (1 - \omega^2 R_1 R_2 C_1 C_2) - j\omega (R_1 C_1 + R_2 C_2 + C_1 R_2) \right]}{\left( 1 - \omega^2 R_1 R_2 C_1 C_2 \right)^2 + \omega^2 (R_1 C_1 + R_2 C_2 + C_1 R_2)^2}$$

$$\beta = \frac{\omega^2 C_1 R_2 (R_1 C_1 + R_2 C_2 + C_1 R_2) + j\omega C_1 R_2 (1 - \omega^2 R_1 R_2 C_1 C_2)}{\left( 1 - \omega^2 R_1 R_2 C_1 C_2 \right)^2 + \omega^2 (R_1 C_1 + R_2 C_2 + C_1 R_2)^2} \dots (4)$$

To have zero phase shift of the feedback network, its imaginary part must be zero.

$$\omega \left(1 - \omega^2 R_1 R_2 C_1 C_2\right) = 0$$

$$\omega^2 = \frac{1}{R_1 R_2 C_1 C_2} \text{ neglecting zero value.}$$

$$\omega = \frac{1}{\sqrt{R_1 R_2 C_1 C_2}}$$

$$f = \frac{1}{2\pi \sqrt{R_1 R_2 C_1 C_2}} \qquad ...(5)$$

This is the frequency of the oscillator and it shows that the components of the quency sensitive arms are the deciding factors, for the frequency.

In practice,  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$  are selected.

$$f = \frac{1}{2\pi\sqrt{R^2 C^2}}$$

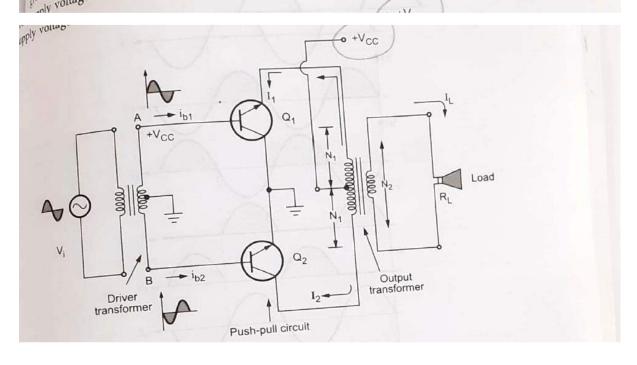

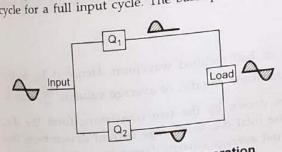

7b. Explain the operation of class B push pull amplifier. Prove that the maximum efficiency of class B configuration is 78.5%.

## 8.11 Push Pull Class B Amplifier

The push pull circuit requires two transformers, one as input transformer called driver transformer and the other to connect the load called **output transformer**. The input signal is applied to the primary of the driver transformer. Both the transformers are centre tapped transformers. The push pull class B amplifier circuit is shown in the Fig. 8.25.

In the circuit, both  $Q_1$  and  $Q_2$  transistors are of n-p-n type. The circuit can use both  $Q_1$  and  $Q_2$  of p-n-p type. In such a case, the only change is that the supply voltage must be  $-V_{CC}$ , the basic circuit remains the same. Generally the circuit using n-p-n transistors is used. Both the transistors are in common emitter configuration.

The driver transformer drives the circuit. The input signal is applied to the primary of transformer. The centre tap on the secondary of the driver transformer is driver transformer tap on the primary of the output transformer is connected to the primary voltage + V<sub>CC</sub>.

## Fig. 8.25 Push pull class B amplifier

With respect to the centre tap, for a positive half cycle of input signal, the point A shown on the secondary of the driver transformer will be positive. While the point B will be negative. Thus the voltages in the two halves of the secondary of the driver transformer will be equal but with opposite polarity. Hence the input signals applied to the base of the

The transistor Q<sub>1</sub> conducts for the positive half cycle of the input producing positive transistors  $Q_1$  and  $Q_2$  will be  $180^\circ$  out of phase. half cycle across the load. While the transistor Q2 conducts for the negative half cycle of the input producing negative half cycle across the load. Thus across the load, we get a full cycle for a full input cycle. The basic push pull operation is shown in the Fig. 8.26. When point A is positive, the

Fig. 8.26 Basic push pull operation

transistor Q1 gets driven into an active region while the transistor Q2 is in cut-off region. While when point A is negative, the point B is positive, hence the transistor Q2 gets driven into an active region while the transistor Q1 is in cut-off region.

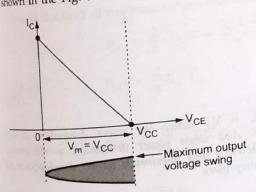

The efficiency of the class B amplifier can be calculated using the basic equation. 111.5 Efficiency

$$\% \eta = \frac{P_{ac}}{P_{DC}} \times 100 = \frac{\left(\frac{V_m I_m}{2}\right)}{\frac{2}{\pi} V_{CC} I_m} \times 100$$

$$\therefore \qquad \boxed{ \% \eta = \frac{\pi}{4} \frac{V_{\rm m}}{V_{\rm CC}} \times 100 }$$

... (7)

From the equation (7), it is clear that as the peak value of the collector voltage  $V_{m}$ 8.11.6 Maximum Efficiency increases, the efficiency increases. The maximum value of  $V_m$  possible is equal to  $V_{CC}$  as shown in the Fig. 8.30.

$$V_{m} = V_{CC} \text{ for maximum } \eta$$

$$\therefore \% \eta_{max} = \frac{\pi}{4} \times \frac{V_{CC}}{V_{CC}} \times 100$$

$$= 78.5 \%$$

Key Point: Thus the maximum possible theoretical efficiency in case of push pull class B amplifier is 78.5 % which is much higher than the transformer coupled class A amplifier.

For practical circuits it is upto 65 to 70 %.

Key Point: Practically the collector-emitter voltage of transistor is neglected as small. But reduces by Vonces and becomes if  $V_{CE\,(min)}$  is given then maximum collector voltage  $V_m$  reduces by  $V_{CE\,(min)}$  and becomes  $V_m = V_{CE\,-}V$  $V_{\rm m} = V_{\rm CC} - V_{\rm CE\,(min)}$  under maximum efficiency condition.

The power dissipation by both the transistors is the difference between a.c. power put and de-8.11.7 Power Dissipation output and d.c. power input.

er input.

$$P_{d} = P_{DC} - P_{ac} = \frac{2}{\pi} V_{CC} I_{m} - \frac{V_{m} I_{m}}{2}$$

A crystal has following parameters. L = 0.3344H, C = 0.065pF,  $C_m$  = 1pF and R = 5.5k $\Omega$ . (08 Marks) Calculate: i) Series resonance frequency ii) Parallel resonance frequency. (04 Marks)

L = 03344H | C = 0.065 × 10<sup>12</sup>F | Cm = 1×10<sup>12</sup>F

R = 5.5 k.r.

$$t_3 = \frac{1}{2\pi \sqrt{Lc}} = 1.08 \text{ MHz}$$

$$Ceq = \frac{CmC}{Cm+C} = 0.06458 * 10^2 \text{ F}$$

$$t_p = \frac{1}{2\pi \sqrt{L Ceq}} = 1.084 \text{ MHz}$$

8a. Explain the operation of class A transformer coupled power amplifier and prove that the maximum efficiency of is 50%.

## 8.8 Transformer Coupled Class A Amplifier

As stated earlier, for maximum power transfer to the load, the impedance matching i necessary. For loads like loudspeaker, having low impedance values, impedance matching is difficult using directly coupled amplifier circuit. This is because loudspeaker resistance in in the range of 3 to 4 ohms to 16 ohms while the output impedance of series fed directly coupled class A amplifier is very much high. This problem can be eliminated by using transformer to deliver power to the load.

Key Point: The transformer is called an output transformer and the amplifier is called transformer coupled class A amplifier.

gefore studying the operation of the amplifier, let us revise few concepts regarding the transformer.

### 8.8.7 Efficiency

The general expression for the efficiency remains same as that given by equations (24) and (25) in section 8.7.

$$\% \ \eta \ = \ \frac{P_{ac}}{P_{dc}} \times 100 = \frac{(V_{max} - V_{min})(I_{max} - I_{min})}{8 \, V_{CC} I_{CQ}} \times 100$$

## 8.8.8 Maximum Efficiency

Assume maximum swings of both the output voltage and output current, to calculate maximum efficiency, as shown in the Fig. 8.20.

Fig. 8.20 Maximum voltage and current swings

Using equation (25) of section 8.7,

$$\% \eta_{\text{max}} = \frac{(2V_{\text{CC}} - 0)(2I_{\text{CQ}} - 0)}{8 V_{\text{CC}} I_{\text{CQ}}} \times 100$$

$$= \frac{4 V_{\text{CC}} I_{\text{CQ}}}{8 V_{\text{CC}} I_{\text{CQ}}} \times 100 = 50 \%$$

8c. Explain the principle of operation of oscillator and the effect of loop gain on the output of oscillator.

### 9.3 Barkhausen Criterion

Fig. 9.2 Inverting amplifier

Consider a basic inverting amplifier with an open loop gain A. The feedback network attenuation factor β is less than unity. As basic amplifier is inverting, it produces a phase shift of 180° between input and output as shown in the Fig. 9.2.

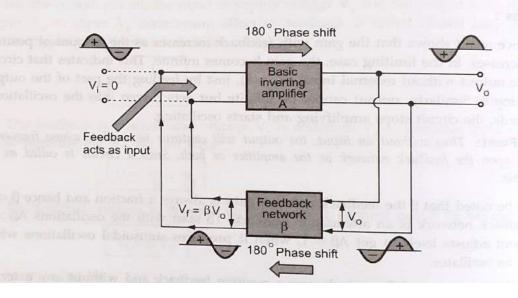

Now the input V<sub>i</sub> applied to the

amplifier is to be derived from its output Vo using feedback network.

But the feedback must be positive i.e. the voltage derived from output using feedback network must be in phase with  $V_i$ . Thus the feedback network must introduce a phase shift of  $180^\circ$  while feeding back the voltage from output to input. This ensures positive feedback.

The arrangement is shown in the Fig. 9.3.

## Fig. 9.3 Basic block diagram of oscillator circuit

Consider a fictitious voltage V<sub>i</sub> applied at the input of the amplifier. Hence we get,

$$V_o = A V_i$$

...(1)

The feedback factor  $\beta$  decides the feedback to be given to input,

$$V_f = \beta V_o$$

...(2)

Oscillators

substituting (1) into (2) we get,

$V_f = A \beta V_i$

For the oscillator, we want that feedback should drive the amplifier and hence V<sub>f</sub> must

for the oscillator, we want that feedback should drive the amplifier and hence

$$A \beta = 1$$

and  $A \beta = 1$

And the phase of V<sub>f</sub> is same as V<sub>i</sub> i.e. feedback network should introduce 180° phase shift in addition to 180° phase shift introduced by inverting amplifier. This ensures positive

In this condition,  $V_f$  drives the circuit and without external input circuit works as an oscillator.

The two conditions discussed above, required to work the circuit as an oscillator are called Barkhausen Criterion for oscillation.

9a. With the help of neat diagram, explain the working and characteristics of N- channel JFET.

## 10.1:1 Characteristics Parameters of JFET

The important characteristics parameters of JFET are as follows:

- Transconductance (g<sub>m</sub>)

- Input resistance and capacitance

- Drain to source resistance (r<sub>d</sub>)

- Amplification factor (µ)

- Power Dissipation (P<sub>D</sub>)

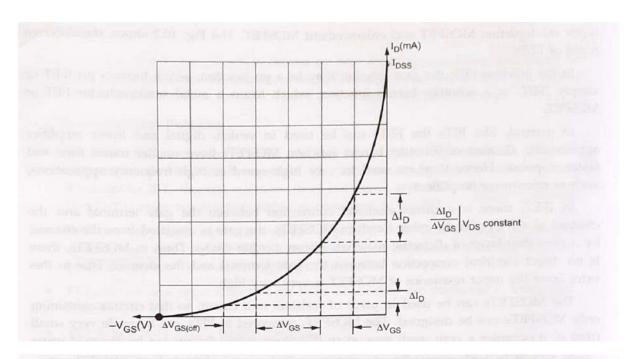

#### 10.1.1.1 Transconductance

The transconductance, gm, is the change in the drain current for given change in gate to source voltage with the drain to source voltage constant as shown in Fig. 10.3.

Looking at Fig. 10.3, we can say that it is the slope of the transfer characteristic. Since the slope varies, gm also varies. gm has a greater value near the top of the curve than it does near the bottom. The transconductance g m is defined as

$$g_{m} = \frac{\Delta I_{D}}{\Delta V_{GS}}\Big|_{V_{DS \text{ constant}}} \qquad ... (1)$$

Fig. 10.3 Transconductance  $g_m$  varies depending on the bias point  $(V_{GS})$

The transconductance  $g_m$  is also called **mutual conductance**. The practical unit for  $g_m$  is mS (millisiemen) or mA/V. For given  $g_m$ , we can calculate an approximate value for  $g_m$  at any point on the transfer characteristic curve using the following equation

$$g_{m} = g_{mo} \left[ 1 - \frac{V_{GS}}{V_{GS(off)}} \right] \qquad \dots (2)$$

where  $g_{mo}$  is the value of  $g_{m}$  for  $V_{GS}$  = 0, and is given by,

$$g_{mo} = \frac{-2 I_{DSS}}{V_p} \qquad \dots (3)$$

This can be proved as given below. We know that,

$$I_{D} = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{p}} \right]^{2}$$

...(3a)

Differentiating this equation with respect to VGS we get,

$$\begin{split} g_m &= \frac{\Delta\,I_D}{\Delta\,V_{GS}} = \frac{-\,2\,I_{DSS}}{V_p}\,\left[1 - \frac{V_{GS}}{V_p}\right] \\ &= \,g_{mo} \bigg[\,1 - \frac{V_{GS}}{V_p}\,\bigg] \qquad \text{where} \quad g_{mo} = \frac{-\,2\,I_{DSS}}{V_p} \end{split}$$

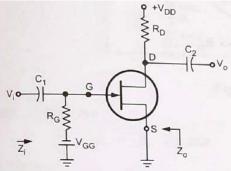

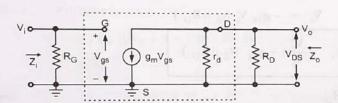

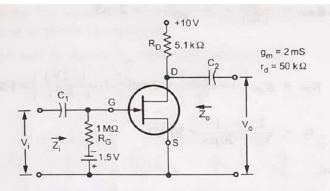

9b. Determine Zi, Zo and Av for JFET common source amplifier with fixed bias configuration using AC equivalent circuit.

## 10.7 Common Source (CS) Configuration

In common source amplifier circuit input is applied between gate and source and output is taken from drain and source. In the following sections we see the low frequency equivalent circuits for common source configuration with different biasing techniques.

## 10.7.1 JFET with Fixed Bias

Fig. 10.48 shows common source amplifier with fixed bias. The coupling capacitor  $C_1$  and  $C_2$  which are used to isolate the dc biasing from the applied ac signal act as short circuits for the ac analysis.

Fig. 10.48 Common source JFET amplifier with fixed bias

Fig. 10.48 shows the low frequency equivalent model for the common source amplifier circuit with fixed bias. It is drawn by replacing:

- All capacitors and dc supply voltages with short circuits and

- JFET with its low frequency equivalent circuit.

Fig. 10.49 AC equivalent model for the common source amplifier circuit with fixed bias

Now, we see the input impedance output impedance and voltage gain of the above model.

### Input impedance Z; :

Looking into Fig. 10.48 we can say that,

$$Z_i = R_G \qquad \dots (1)$$

### Output Impedance Z<sub>o</sub>:

The output impedance  $Z_o$  is the impedance measured looking from the output side with input voltage  $(V_i)$  equal to 0. As  $V_i = 0$ ,

$$V_{gs} = 0$$

and hence  $g_m V_{gs} = 0$ .

The replaced Fig. 10.4

The  $g_m V_{gs} = 0$  allows current source to be replaced by an open circuit, as shown in the Fig. 10.49. Therefore the output impedance is

$$Z_o = R_D || r_d$$

... (2)

Fig. 10.50

If the resistance r<sub>d</sub> is sufficiently large compared to R<sub>D</sub>, then we say that the output impedance is approximately equal to RD.

## Voltage Gain $\mathbf{A}_{\mathbf{v}}$ :

The voltage gain A  $_{v}=\frac{V_{ds}}{V_{gs}}=\frac{V_{o}}{V_{i}}$

Looking at Fig. 10.48 we can write

$$V_{o} = -g_{m} V_{gs} (r_{d} || R_{D})$$

... (4)

As we know  $V_i = V_{gs}$  we can write

$$V_{o} = -g_{m} V_{i} (r_{d} || R_{D})$$

(6)

$$V_{o} = -g_{m} V_{i} + Q_{m} V_{i}$$

$$A_{v} = \frac{V_{o}}{V_{i}} - g_{m} (r_{d} || R_{D})$$

... (6)

and if

$$r_d \gg R_D$$

, ... (7)

$$A_v \approx -g_m R_D$$

... (7)

9c. Write down the differences between BJT and JFET.

| 6  | Input resistance                  | Less compare to JFET.                                                                                                                          | High compare to BJT.                                                                                                                                                 |

|----|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | Size                              | Bigger than JFET.                                                                                                                              | Smaller in construction than BJT thus making them useful in integrated - circuits (IC).                                                                              |

| 8  | Sensitivity                       | Higher sensitivity to changes in the applied signals.                                                                                          | Less sensitivity to changes in the applied voltage.                                                                                                                  |

| 9  | Thermal stability                 | Less                                                                                                                                           | More                                                                                                                                                                 |

| 10 | Thermal runaway                   | Exists in BJT, because of cumulative effect of increase in $I_{\mathbb{C}}$ with temperature, resulting increase in temperature in the device. | Does not exist in JFET, because drain resistance $r_d$ increases with temperature, which reduces $l_D$ , reducing the $l_D$ and hence the temperature of the device. |

| 11 | Relation between input and output | Linear                                                                                                                                         | Non-linear                                                                                                                                                           |

| 12 | Ratio of o/p to i/p               | $\frac{\Delta I_{C}}{\Delta I_{B}} = \beta$                                                                                                    | $\frac{\Delta I_{D}}{\Delta V_{GS}} = g_{m}$                                                                                                                         |

| 13 | Thermal noise                     | More in BJT as more charge carriers cross junctions.                                                                                           | Much lower in JFET as very few charge carriers cross the junction.                                                                                                   |

| 14 | Gain bandwidth product            | High                                                                                                                                           | Low                                                                                                                                                                  |

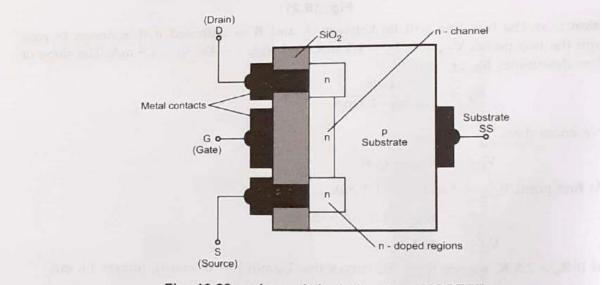

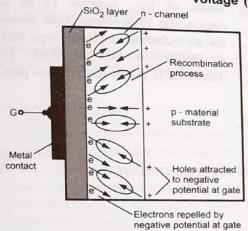

10a. With the help of neat diagram, explain the construction, working and characteristics of Nchannel depletion type MOSFET.

## 10.3.1 Depletion MOSFET (D-MOSFET)

## 10.3.1.1 Construction of n-channel MOSFET

The Fig. 10.22 shows the basic construction of n-channel depletion type MOSFET. Two highly doped n regions are diffused into a lightly doped p type substrate. These two highly doped n regions represent source and drain. In some cases substrate is internally connected to the source terminal.

The source and drain terminals are connected through metallic contacts to n-doped regions linked by an n-channel as shown in the Fig. 10.22. The gate is also connected to a metal contact surface but remains insulated from the n-channel by a very thin layer of dielectric material, silicon dioxide (SiO2). Thus, there is no direct electrical connection between the gate terminal and the channel of a MOSFET, increasing the input impedance of the device.

Fig. 10.22 n-channel depletion-type MOSFET

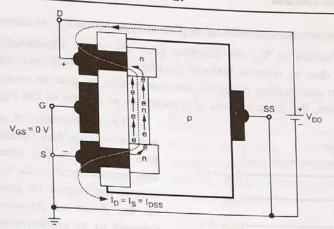

## 10.3.1.2 Operation, Characteristics and Parameters of n-channel MOSFET

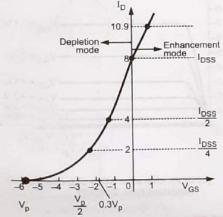

On the application of drain to source voltage,  $V_{DS}$  and keeping gate to source voltage to zero by directly connecting gate terminal to the source terminal, free electrons from the n-channel are attracted towards positive potential of drain terminal. This establishes current through the channel to be denoted as  $I_{DSS}$  at  $V_{GS}=0$  V, as shown in the Fig. 10.23.

Fig. 10.23 n-channel depletion-type MOSFET with  $\rm V_{GS}$  = 0 V and an applied voltage ( $\rm V_{DD}$ )

Fig. 10.24 Reduction in free electrons in the n-channel due to negative potential at the gate

Fig. 10.25 Transfer characteristics for an n-channel depletion type MOSFET

If we apply negative gate voltage, the negative charges on the gate repel conduction electrons from the channel, and attract holes from the p type substrate. This initiates recombination of repelled electrons and attracted holes as shown in the Fig. 10.24.

The level of recombination between electrons and holes depends on the magnitude of the negative voltage applied at the gate. This recombination reduces the number of free electrons in the n-channel for the conduction, reducing the drain current.

In other words we can say that, due to recombinations, n-channel is depleted of some of its electrons, thus decreasing the channel conductivity. The greater the negative voltage applied at the gate, the greater the depletion of n-channel electrons. The level of drain current will reduce with increasing negative bias for  $V_{GS}$  as

shown in the transfer characteristics of depletion type MOSFET (as shown in Fig. 10.25).

For positive values of  $V_{GS}$  the positive gate will draw additional electrons from the p-type substrate due to reverse leakage current and establish new carriers through the collisions between accelerating particles. Because of this, as gate to source voltage increases in positive direction, the drain current also increases as shown in the Fig. 10.25.

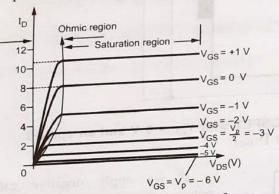

Fig. 10.26 Drain characteristics for an n-channel depletion type MOSFET

The application of a positive gate to source voltage has "enhanced" the level of free carriers in the channel compared to that encountered with  $V_{\rm GS}=0$  V. For this reason the region of positive gate voltages on the drain or transfer characteristics is referred to as enhancement region and the region between cut-off and the saturation levels of  $I_{\rm DSS}$  referred to as depletion region. Fig. 10.26 shows drain characteristics for an n-channel depletion type MOSFET. It is similar to that of JFET. The only difference is that it has positive part of  $V_{\rm GS}$ .

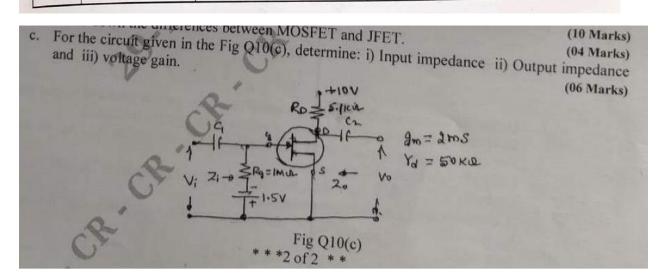

9b. Write down the differences between MOSFET and JFET.

# 10.3.2.4 Comparison Comparison of JFET and MOSFET

|            | Parameter         | JFET                         | MOSFET                                |

|------------|-------------------|------------------------------|---------------------------------------|

| Sr.<br>No. |                   |                              | A) n-channel depletion type           |

| 1.         | Types             | a) n-channel<br>b) p-channel | MOSFET                                |

|            |                   | b) p-chame                   | B) p-channel depletion type<br>MOSFET |

|            | P THE SAME NAME.  | es predictiffs to            | C) n-channel enhancement type         |

|            | again to the like | CIVE OF                      | D) p-channel enhancement type MOSFET  |

| alog Election |           |                                                  |                                                                                         |  |

|---------------|-----------|--------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| 2.            | Symbols   |                                                  | n-channel Depletion type                                                                |  |

| 3.            | Operation | oS oS n-channel p-channel  Operated in depletion | n-channel p-channel Enhancement type  Operated in depletion and                         |  |

| 4.            | mode      | mode. High (> 10 M Ω)                            | enhancement mode.  Very high (> 10,000 MΩ)                                              |  |

| 5.            | impedance | Gate is not insulated from channel               | Gate is insulated from channel by a layer of SiO <sub>2</sub> .                         |  |

| 6.            | Channel   | Channel exists permanently.                      | Channel exists permanently in depletion type MOSFET, but no in enhancement type MOSFET. |  |

Fig. 10.51

Solution: i) We have

$$Z_i = R_G = 1 M\Omega$$

ii) We have

$$Z_{o} = r_{d} || R_{D} = 50 K || 5.1 K = 4628 \Omega$$

iii) Voltage Gain  $A_v$ : We have

$$A_v = -g_m (r_d || R_D) = -2 \text{ mS } (50 \text{ K} || 5.1 \text{ K}) = -2 \text{ mS } (4628)$$

= -9.256