## Third Semester B.E. Degree Examination, Aug./Sept.2020 **Analog Electronic Circuits**

Time: 3 hrs

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Module-1

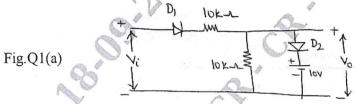

For the clipper circuit shown in fig. Q1(a), the input is Vi = 50 Sinwt. Calculate and plot to 1 scale the transfer characteristic, indicating slopes and intercept. (10 Marks)

b. An emitter bias circuit has  $R_C = 2K \Omega$ ,  $R_E = 680 \Omega$ ,  $V_E = 2.1V$ ,  $V_{CE} = 7.3V$ ,  $I_B = 20\mu A$ . Find V<sub>CC</sub>, R<sub>B</sub> & β. (05 Marks)

What is meant by transistor biasing? Compare different biasing methods used for transistor biasing with respect to stability (05 Marks)

OR

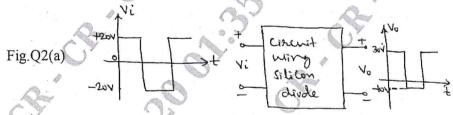

Design a suitable circuit represented by the box shown below. Which has input and output waveforms as indicated in fig. Q2(a). (08 Marks)

- Find the operating point for the voltage divider bias circuit with  $\beta = 80$  and  $V_{BE} = 0.6$ V. Find the new operating point when β changes to 100 and V<sub>BE</sub> changes to 0.25V. Given  $V_{CC} = 15V$ ,  $R_1 = 100 \text{ K}\Omega$ ,  $R_2 = 18K\Omega$ ,  $R_C = 4.7K\Omega$  and  $R_E = 1K\Omega$ . (08 Marks)

- Explain the circuit of a transistor switch being used as an inverter.

(04 Marks)

Module-2

- Draw the hybrid small signal model of a transistor. Mention the advantages of 3 h – parameters. (04 Marks)

- b. Derive the expression for A<sub>V</sub>, A<sub>I</sub>, Z<sub>i</sub> and Z<sub>o</sub> for CE fixed bias configuration using complete hybrid equivalent model. (10 Marks) (06 Marks)

- State and prove Miller's theorem.

CMRIT LIBRARY BANGALORE - 560 037

OR Derive the expressions for Z<sub>i</sub>, Z<sub>o</sub>, A<sub>V</sub> and A<sub>I</sub> for CB – configuration of transistor using approximate hybrid equivalent model. (10 Marks)

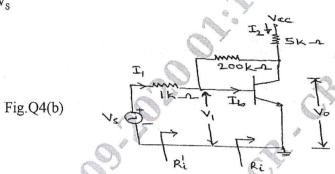

- b. The circuit shown in fig.Q4(b) uses transistor with  $h_{ie}=1100\Omega$  ,  $h_{fe}=50$  ,  $h_{oe}=0.025\times 10^{-3}~\textrm{T}~,~h_{re}=2.5\times 10^{-4}.~Calculate~~R_{i}=\frac{V_{l}}{I_{b}}~,~~R_{i}^{'}=\frac{V_{l}}{I_{l}}~,~~A_{V}=\frac{V_{0}}{V_{l}}~~and$

- $A_{VS} = \frac{V_o}{V_S} \, .$

(10 Marks)

Module-3

- 5 a. Explain with the help of circuit, what is cascade connection? What are the advantages of this connection? (06 Marks)

- b. What is negative feedback in amplifiers? Show that negative feedback increases the bandwidth of an amplifier. (08 Marks)

- c. An amplifier with negative feedback has a voltage gain of 100. It is found that without feedback, an input signal of 50mV is required to produce a given output. Where as with feedback the input signal must be 0.5V for the same output. Determine the value of A and β.

OR

- 6 a. With appropriate h parameters equivalent circuit, obtain the expression for Z<sub>i</sub>, Z<sub>o</sub>, A<sub>v</sub> for a Darlington emitter follower. (10 Marks)

- b. Derive expression Z<sub>if</sub> and Z<sub>of</sub> for voltage series feedback amplifier. (10 Marks)

Module-4

- 7 a. Discuss the different types of power amplifiers. (04 Marks)

- b. Show that the maximum percentage efficiency for a series fed class A amplifier is 25%.

(10 Marks)

- c. A Quartz crystal has L=0.12H, C=0.04 PF,  $C_M=1$  PF and R=9.2 K $\Omega$ . Find i)  $f_s$  and ii)  $f_p$ . (06 Marks)

OR

- 8 a. State and explain the Barkhemsen's criterion to obtain sustained oscillations. (06 Marks)

- b. With the help of circuit diagram, explain the working principle of R<sub>c</sub> = phase shift oscillator, with relevant equations. (08 Marks)

- c. A class B amplifier provides a 20V peak signal to a  $16\Omega$  load and a power supply of  $V_{CC} = 30V$ . Determine the input power, output power and circuit efficiency. (06 Marks)

Module-5

- 9 a. Draw the JFET amplifier using fixed bias configuration. Derive Z<sub>i</sub>, Z<sub>o</sub> and A<sub>v</sub> using small signal model. (08 Marks)

- b. Compare JFET and MOSFET. (04 Marks)