Third Semester B.E. Degree Examination, Jan./Feb. 2021

17EE35

5

table and characteristic equation.

6 a. Draw and explain universal shift Registers.

(12 Marks)

b. Design and draw Mod 6 Asynchronous counter.

(08 Marks)

(10 Marks)

Module-4

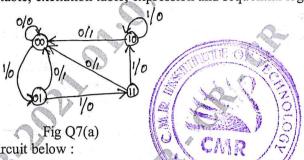

7 a. Construct the sequential logic circuit of following state diagram using JKFF. Clearly show the state table, transition table, excitation table, expression and sequential logic diagrams.

WOOLLORE

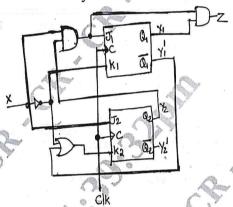

- b. Analyze the sequential circuit below:

- ) Derive the state table

- ii) Sketch the transition state diagram

- iii) Describe in words the functionality of the circuit

Fig Q7(b)

(10 Marks)

OR

8 a. Design Mod 4 synchronous up down counter using JKFF.

(10 Marks)

b. Design a synchronous counter that counts the following sequence

(10 Marks)

Module-5

9 a. What are the different VHDL Descriptions?

(05 Marks)

- b. Write the VHDL program for Half Adder in

- i) Behavioral Descriptions

- ii) Structural Descriptions

- iii) Dataflow Descriptions

(15 Marks)

OR

10 a. Explain the structure of Data-flow Descriptions.

(07 Marks)

b. What are the different operators and data types in VHDL?

(08 Marks)

c. Compare VHDL and Verilog.

(05 Marks)

\* \* \* \*