# Visvesvaraya Technological University Belgaum, Karnataka-590 018

A Project Report on

## "AN INTELLIGENT SUVEILLANCE SYSTEM BASED ON MOTION DETECTION"

Project Report submitted in partial fulfillment of the requirement for the award of the degree of

# Bachelor of Engineering

Electrical & Electronics Engineering Submitted by Santosh Kumar N A(1CR16EE415) Devanshu kumar(1CR15EE026) ABHISHEK KUMAR RAY(1CR14EE001) ARMAN KUMAR(USN- 1CR15EE013)

Under the Guidance of

Ms. Lokasree B S

Assistant professor, Department of Electrical & Electronics Engineering CMR Institute of Technology

CMR Institute of Technology, Bengaluru-560 037

**Department of Electrical & Electronics Engineering**

## 2019-2020

i

#### CMR INSTITUTE OF TECHNOLOGY DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING AECS Layout, Bengaluru-560 037

# Certificate

Certified that the project work entitled "AN INTELLIGENT SUVEILLANCE SYSTEM BASED ON MOTIon DETECTION" carried out by Mr Arman kumar (1CR15EE013) and Mr **DEVANSHU** Kumar(1CR15EE026) Mr ABHISHEK KUMAR RAY(1cr14ee001) SANTHOSH KUMAR N A(1cr16ee415) are bonafied students of CMR Institute of Technology, Bengaluru, in partial fulfillment for the award of Bachelor of Engineering in Electrical & Electronics Engineering of the Visvesvaraya Technological University, Belgaum, during the year 2019-2020. It is certified that all corrections/suggestions indicated for Internal Assessment have been incorporated in the Report deposited in the departmental library.

The project report has been approved as it satisfies the academic requirements inSignature of the GuideSignature of the HODSignature of the Principal

Ms.lokasree B S, Assistant Professor EEE Department CMRIT, Bengaluru

Dr. K. Chitra Professor & HOD EEE Department CMRIT, Bengaluru

------

Signature & Date

-----

Dr. Sanjay Jain Principal, CMRIT, Bengaluru

#### External Viva

Name of the Examiners

- 1.

- 2.

#### CMR INSTITUTE OF TECHNOLOY DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING AECS Layout, Bengaluru-560 037

## DECLARATION

We, [Mr. Arman kumar (**1CR15EE013**) Mr. **DEVANSHU** and Kumar(1CR15EE026, Mr ABHISHEK KUMAR RAY(1cr14ee001) SANTHOSH KUMAR N A(1cr16ee415) hereby declare that the report entitled "AN INTELLIGENT SUVEILLANCE SYSTEM BASED ON MOTION DETECTION" has been carried out by us under the guidance of Ms. Lokasree B S, Assistant Professor, Department of Electrical & Electronics Engineering, CMR Institute of Technology, Bengaluru, in partial fulfillment of the requirement for the degree of BACHELOR OF ENGINEERING in ELECTRICAL & ELECTRONICS ENGINEERING, of Visveswaraya Technological University, Belagaum during the academic year 2019-20. The work done in this report is original and it has not been submitted for any other degree in any university.

Place: Bengaluru Date:

# **Abstract**

Surveillance is a common technology nowadays. By general it means a mechanism to monitor the behavior, activities, or another changing information. Most technology used by implementing a CCTV device in watched area.

A CCTV consist of video devices, PC to monitor the video real time, and human as person who monitor the area. The weakness occurs from that kind of mechanism, it needs a human to watch every time. And the cost is very expensive for building it.

Thus, an infrared movement detection sensor called PIR (passive infrared) Sensor can be utilized.

Passive infrared (PIR) sensors are very popular as they are massproduced at very low cost. Most commonly they have been used for in-building and homes applications to detect presence and movement in order to directly switch lights and appliance. Passive infrared (PIR) sensors are very popular as they are mass-produced at very low cost. Most commonly they have been used for in-building and homes applications to detect presence and movement in order to directly switch lights and appliances. In contrast to other sensors such as ultrasound rangers or infrared light distance sensors, PIRs have very low power consumption.

## **ACKNOWLEDGEMENT**

The satisfaction and euphoria that accompany the successful completion of any task would be incomplete without the mention of people, who are responsible for the completion of the project and who made it possible, because success is outcome of hard work and perseverance, but stead fast of all is encouraging guidance. So with gratitude we acknowledge all those whose guidance and encouragement served us to motivate towards the success of the project work.

We take great pleasure in expressing our sincere thanks to **Dr. Sanjay Jain**, **Principal, CMR Institute of Technology, Bengaluru** for providing an excellent academic environment in the college and for his continuous motivation towards a dynamic career. We would like to profoundly thank **Dr. B Narasimha Murthy**, Vice-principal of CMR Institute of Technology and the whole **Management** for providing such a healthy environment for the successful completion of the project work.

We would like to convey our sincere gratitude to **Dr. K Chitra**, **Head of Electrical** and Electronics Engineering Department, CMR Institute of Technology, Bengaluru for her invaluable guidance and encouragement and for providing good facilities to carry out this project work.

We would like to express our deep sense of gratitude to Lokasree B S, Assistant Professor, Electrical and Electronics Engineering, CMR Institute of Technology, Bengaluru for his/her exemplary guidance, valuable suggestions, expert advice and encouragement to pursue this project work.

We are thankful to all the faculties and laboratory staffs of Electrical and Electronics Engineering Department, CMR Institute of Technology, Bengaluru for helping us in all possible manners during the entire period.

Finally, we acknowledge the people who mean a lot to us, our parents, for their inspiration, unconditional love, support, and faith for carrying out this work to the finishing line. We want to give special thanks to all our friends who went through hard times together, cheered us on, helped us a lot, and celebrated each accomplishment.

Lastly, to the Almighty, for showering His Blessings and to many more, whom we

didn't mention here.

### CONTENTS

| Title Page                         | i      |

|------------------------------------|--------|

| Certificate                        | ii     |

| Declaration                        | iii    |

| Abstract                           | iv     |

| Acknowledgements                   | V      |

| Contents                           | vi-vii |

| Chapter 1: INTRODUCTION            | 9–10   |

| Chapter 2: LITERATURE REVIEW       | 11-22  |

|                                    | 1      |

| Chapter 3: METHODOLOGY             | 23-48  |

| 3.1 Block diagram                  | 24-25  |

| 3.2 Hardware methodology           | 26-40  |

| 3.3 Software methodology           | 41-47  |

| Chapter 4: RESULTS AND DISCUSSIONS | 48     |

| Chapter 5: | REFERENCES | 49 |

|------------|------------|----|

|------------|------------|----|

## LIST OF ABBREVIATIONS AND SYMBOLS

#### Internet of Things

The Internet of Things is a collection of interrelated computing devices, mec hanical and digital machines, objects, animals or individuals that have uniqu e identifiers and the ability to transfer data over a network without needing h uman-to-human or computer-to-computer interaction.

#### PIR

A **passive Infrared sensor** (**PIR sensor**) is an electronic that measures <u>infrared</u> (IR) light radiating from objects in its field of view. They are most often used in <u>PIR-based motion detectors</u>

#### MC AVR

An embedded system is a system which is going to do a predefined specified task is the embedded system and is even defined as combination of both software and hardware. A general-purpose definition of embedded systems is that they are devices used to control, monitor or assist the operation of equipment, machinery or plant. "Embedded" reflects the fact that they are an integral part of the system. At the other extreme a general-purpose computer may be used to control the operation of a large complex processing plant, and its presence will be obvious .All embedded systems are including computers or microprocessors. Some of these computers are however very simple systems as compared with a personal computer .The very simplest embedded systems are capable of performing only a single function or set of functions to meet a single predetermined purpose.

## **CHAPTER 1**

# **INTRODUCTION**

Surveillance is a common technology nowadays. By general it means a mechanism to monitor the behavior, activities, or another changing information. Most technology used by implementing a CCTV device in watched area. A CCTV consist of video devices, PC to monitor the video real time, and human as person who monitor the area. The weakness occurs from that kind of mechanism, it needs a human to watch every time. And the cost is very expensive for building it. Thus, an infrared movement detection sensor called PIR (passive infrared) Sensor can be utilized. Passive infrared (PIR) sensors are very popular as they are mass-produced at very low cost. Most commonly they have been used for inbuilding and homes applications to detect presence and movement in order to directly switch lights and appliances. In contrast to other sensors such as ultrasound rangers or infrared light distance sensors, PIRs have very low power consumption.

#### Fig 1.1 AN INTELLIGENT SUVEILLANCE SYSTEM BASED ON MOTION DETECTION

## **CHAPTER 2**

## **LITERATURE SURVEY**

**Bashar Alathari et al. [1]** considered the problem of automated position estimation using the electronic circuit of inexpensive binary motion sensors. They present simulation and experiments with Passive Infrared (PIR) motion sensors that suggest our current estimator. Fritzing software simulator is used to test and draw the circuits of the system. The proposed design worked efficiently during the experiments and shown high performance with 360 degrees of det Sanjana Prasad et al. [2] The proposed home security system captures information and transmits it via a 3G Dongle to a Smart phone using web application. Raspberry pi operates and controls motion detectors and video cameras for remote sensing and surveillance, streams live video and records it for future playback. It can also find the number of persons located with the help of the Infrared sensor..

**R Ismail et al.** [3] used PIR and IR and designed a robot. The hardware was integrated in one application board as embedded system design. The software was developed using C++ and compiled by Arduino IDE 1.6.5. The main objective of this project is to provide simple guidelines to the polytechnic students and beginners who are interested in this type of research. **Cheng huang tesai et al.** [4] present a way to reduce the standby power consumption of a PIR-sensor-based lighting device. Generally, although a PIR-sensor-based lighting device will turn on when motion is detected and turn off when the motion is no longer present, this device still consumes 1-3 W of power when the lamp is off. In this design the device consumes 0.004 W when the light is turned off, and it is not only easy to set up but also inexpensive. K. N. Ha et al. [5] presents a novel non-terminal-based approach using an array of pyroelectric infrared sensors (PIR sensors) that can detect residents. The feasibility of the system is evaluated experimentally on a test bed Automatic system

Four motors are used for the purpose like movement of robot, water pump.

Relays are used to drive water pumps and motor cleaners. LM293D IC is used for motor wheel drive. All the details is shown on LCD. Such criteri a are compatible with some of the behaviors expected to be programmed i nto the robot. This consists of four dedicated wipers fixed to the board. One of the wipers is cylindrical, and the others are geometrically square. The flat wipers are mounted symmetrically at the bottom of the Platform, positioned in' V' shape to ensure efficient cleaning and dust collection. The roller wipers are mounted with proper ties and driver motor at the end of the platform. Using wet wiping method, cleaning is rendered effective. This device uses a small bottle which carries water within it. That ensures a full surface cleaning. Only the front wipers are rendered watery. It means that the rear wiper removes the water from the surface.

The robot works in both autonomous and manual mode, along with additio nal features such as precise time scheduling and bagless dirt containers wit h auto-

dirt disposal function. This work can be very useful in the development of human life style.

The proposed design is in dual mode operation. In one of the modes, the r obot is fully autonomous and makes decisions based on the outputs of infr arot proximity sensors, ultrasonic sensors and tactile sensors after Arduino (mega) controller is processed and the actuators are controlled (2 DC encoder motors) by the H-bridge driving circuitry.

The robot can also be used to clean a particular area of a room by manuall y monitoring it from a laptop using the Visual Studio Graphical User Inte rface (GUI). (C# programming language) via Bluetooth connectivity.

The following figure shows the working model of CLEAR:

The base of the body comprises of acrylic sheet, two encoder motors along with Teflon tires having O-rings on them for avoiding friction, two ball casters of adjustable height having frictionless steel balls, aluminium angular brackets and aluminium holders for two lead acid batteries of 12V and 1.2Ah rating.

A DC geared motor, sprockets for moving chain from geared motor to spi nning brush and two aluminum rods for supporting vacuum cleaner mech anism and dirt compartment are included in the cleaning system.

Components are installed at the bottom of the acrylic sheet, so that the ce nter of gravity is lower and the robot is stable

In some of the vacuum cleaners, AT89S52 Micro-Controller manages both hardware and software operations.

RF modules were used for remote (manual) and robot wireless communica tion with a range of 50 m. This robot is equipped for obstacle detection an d automated water sprayer pump with IR sensor. It uses four motors, two f or cleaning, one for water pumping and one for wheels. Dual relay circuit used to drive the motors one for water pump and another for cleaner. All the operations themselves are managed in the automatic mode robot and the lane changes in case of hurdle detection and moves back. The keypad is used in manual mode to accomplish the intended task and to run robot. The RF module was used to transmit and receive information between remote and robot, and to display information on the LCD relevant to hurdle detection.

Unlike other floor cleaner robots this is not a vacuum cleaner robot; it performs sweeping and mopping operation. Detachable mop is used for mopping. Robot performs all of the operations itself in automatic mode. First, the robot begins, moves forward and carries out cleaning operation. These have been used to track obstacles and to clear hurdle IR sensors.

If any obstacle is detected then the robot will automatically change the lan e,will not stop and will start cleaning. This assumes zig-zag trajectory.

For the convenience of the user, automatic water sprayer is attached whic h automatically sprays water for mopping, so no need to reattach wet clot h for mop-

ing.Four motors have been used to perform valued operations such as mo ving the device, water pumping and cleaning.

Relays are used to operate water pumps and engine cleaners. LM293D IC is used for motor wheel driving.

All the details is displayed on LCD. In manual mode, the robot is controll ed by the user itself. RF module have been used to transmit and receive the signal

In the manual mode, if any hurdle is detected, then signal of hurdle detection is displayed on the LCD of remote via RF module.

All the information displayed on LCD. In the manual mode, user itself operates the robot. RF module have been used to transmit and receive the signal to operate the robot through remote. In the manual mode, if any hurdle detected, then signal of hurdle detection displayed on the LCD of remote via RF module.

pathway. Direction does it take depends on where the bumper makes contact. For example, if a vacuum enters an object with its bumper's left side, it will generally turn right because the object has been determined to be to its left. And maneuvering around items can often leave uncleaned swaths of concrete.

Some manufacturers take different approaches to obstacles, literally, to minimize this. For example, an iRobot Roomba can slow as its encounters an obstacle. "The beauty of Roomba is that we handle things softly, because what we find is that you can move through soft items such as curtains and bed skirts," said Ken Bazydola, product management director for iRobot. This gives us better coverage .

13

dict whether our vacuum cleaner has completely cleaned our room or not"

Whereas in our proposed work we can conform ourselves that our floor has been cleaned by vacuum cleaner completely because in our project we will be using range of interest which will help our vacuum cleaner in determining the obstacles and selecting proper path to move.

## PIR SENSORS

A **passive Infrared sensor** (**PIR sensor**) is an electronic <u>sensor</u> that measures <u>infrared</u> (IR) light radiating from objects in its field of view. They are most often used in <u>PIR-based motion detectors</u>.

#### **Operating Principle**

All objects above <u>absolute zero</u> emit <u>heat</u> energy in the form of infrared radiation (infrared light). Usually infrared light is invisible to the <u>human eye</u>, but it can be detected by electronic devices designed for such a purpose.

The term *passive* in this instance refers to the fact that PIR devices do not generate or radiate any energy for detection purposes. They work entirely by detecting the energy given off by other objects.

Construction

Infrared radiation enters through the front of the sensor, known as the *sensor face*. At the core of a PIR sensor is a <u>solid state</u> *sensor* or set of sensors, made from <u>pyroelectric</u> materials -- materials which generate energy when exposed to heat. Typically, the sensors are approximately 1/4 inch square, and take the form of a <u>thin film</u>. Materials commonly used in PIR sensors include <u>gallium nitride</u> (GaN), <u>caesium nitrate</u> (CsNO<sub>3</sub>), <u>polyvinyl fluorides</u>, derivatives of <u>phenylpyrazine</u>, and <u>cobalt phthalocyanine</u>. The sensor is often manufactured as part of an <u>integrated circuit</u>.

#### **PIR based motion detector**

A PIR-based <u>motion detector</u> is used to sense movement of people, animals, or other objects. They are commonly used in <u>burglar alarms</u> and automatically-activated <u>lighting</u> systems. They are commonly called simply "PIR", or sometimes "PID", for *passive infrared detector*.

#### Operation

Strictly speaking, individual PIR sensors do not detect motion; rather, they detect abrupt changes in temperature at a given point. As an object, such as a <u>human</u>, passes in front of the background, such as a <u>wall</u>, the temperature at that point will rise from <u>room temperature</u> to <u>body temperature</u>, and then back again. This quick change triggers the detection. Moving objects of identical temperature will not trigger detection.

PIDs can be equipped with more than one internal sensing element so that, with the appropriate electronics, it can detect the apparent direction of movement. As an object passes in front of adjacent sensors in turn, this implies the direction of movement. This may be used by on-board electronics to reduce false alarms, i.e., by requiring adjacent sensors to trip in succession. It may also be used to signal the direction of movement to a monitoring apparatus.

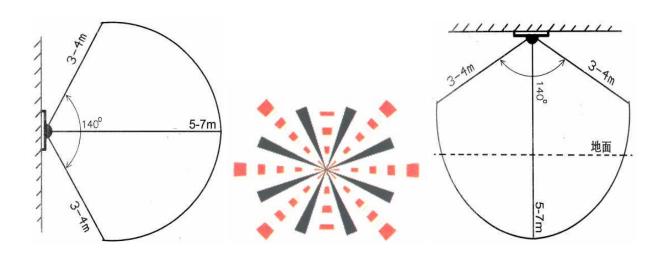

PIDs come in many configurations for a wide variety of applications. The most common models have numerous Fresnel lenses or mirror segments, an effective range of about thirty feet, and a field of view less than 180 degrees. Models with wider fields of view, including 360 degrees, are available -- typically designed to mount on a ceiling. Some larger PIDs are made with single segment mirrors and can sense changes in infrared energy over one hundred feet away from the PID. There are also PIDs designed with reversible orientation mirrors which allow either broad coverage (110° wide) or very narrow "curtain" coverage, or with individually selectable segments to "shape" the coverage.

#### **Differential detection**

Pairs of sensor elements may be wired as opposite inputs to a differential amplifier. In such a configuration, the PIR measurements cancel each other so that

the average temperature of the field of view is removed from the electrical signal; an increase of IR energy across the entire sensor is self-cancelling and will not trigger the device. This allows the device to resist false indications of change in the event of being exposed to brief flashes of light or field-wide illumination. (Continuous high energy exposure may still be able to saturate the sensor materials and render the sensor unable to register further information.) At the same time, this differential arrangement minimizes common-mode interference, allowing the device to resist triggering due to nearby electric fields. However, a differential pair of sensors cannot measure temperature in this configuration, and therefore is only useful for motion detection.

#### **Product design**

The PIR sensor is typically mounted on a <u>printed circuit board</u> containing the necessary electronics required to interpret the signals from the sensor itself. The complete assembly is usually contained within a housing, mounted in a location where the sensor can cover area to be monitored.

The housing will usually have a plastic "window" through which the infrared energy can enter. Despite often being only <u>translucent</u> to visible light, infrared energy is able to reach the sensor through the window because the plastic used is <u>transparent</u> to infrared radiation. The plastic window reduces the chance of foreign objects (dust, insects, etc.) from obscuring the sensor's field of view, damaging the mechanism, and/or causing <u>false alarms</u>. The window may be used as a filter, to limit the wavelengths to 8-14 micrometres, which is closest to the infrared radiation emitted by humans. It may also serve as a focusing mechanism; see below.

#### Focusing

Different mechanisms can be used to focus the distant infrared energy onto the sensor surface.

#### Lenses

The <u>plastic window covering</u> may have multiple facets molded into it, to focus the infrared energy onto the sensor. Each individual facet is a <u>Fresnel lens</u>.

#### MC AVR

#### **Embedded System**

An embedded system is a system which is going to do a predefined specified task is the embedded system and is even defined as combination of both software and hardware. A general-purpose definition of embedded systems is that they are devices used to control, monitor or assist the operation of equipment, machinery or plant. "Embedded" reflects the fact that they are an integral part of the system. At the other extreme a general-purpose computer may be used to control the operation of a large complex processing plant, and its presence will be obvious .All embedded systems are including computers or microprocessors. Some of these computers are however very simple systems as compared with a personal computer. The very simplest embedded systems are capable of performing only a single function or set of functions to meet a single predetermined purpose. In more complex systems an application program that enables the embedded system to be used for a particular purpose in a specific application determines the functioning of the embedded system. The ability to have programs means that the same embedded system can be used for a variety of different purposes. In some cases a microprocessor may be designed in such a way that application software for a particular purpose can be added to the basic software in a second process, after which it is not possible to make further changes. The applications software on such processors is sometimes referred to as firmware .The simplest devices consist of a single microprocessor (often called a "chip"), which may itself be packaged with other chips in a hybrid system or Application Specific Integrated Circuit (ASIC). Its input comes from a detector or sensor and its output goes to a switch or activator which (for example) may start or stop the operation of a machine or, by operating a valve, may control the flow of fuel to an engine.

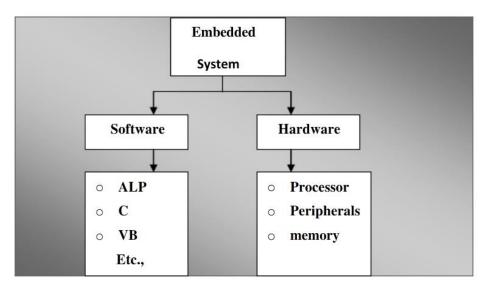

As the embedded system is the combination of both software and hardware

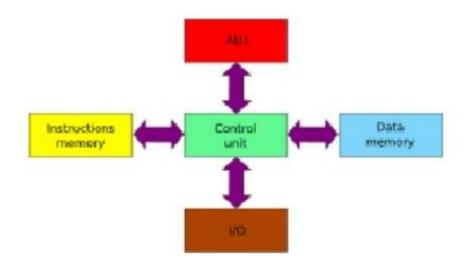

Block diagram of Embedded System

Software deals with the languages like ALP, C, and VB etc., and Hardware deals with

Processors, Peripherals, and Memory.

Memory: It is used to store data or address.

Peripherals: These are the external devices connected

Processor: It is an IC which is used to perform some task

### Applications of embedded systems

- Manufacturing and process control

- Construction industry

- Transport

- Buildings and premises

- Domestic service

- Communications

- Office systems and mobile equipment

- Banking, finance and commercial

- Medical diagnostics, monitoring and life support

- Testing, monitoring and diagnostic systems

## Processors are classified into four types like:

- Micro Processor (µp)

- Micro controller (µc)

- Digital Signal Processor (DSP)

- Application Specific Integrated Circuits (ASIC)

## Micro Processor (µp):

A silicon chip that contains a CPU is called MPU. In the world of personal computer the terms microprocessor and CPU are used interchangeably. At the heart of all personal computers and most workstations sits a microprocessor. Microprocessors also control the logic of almost all digital devices, from clock radios to fuel-injection systems for automobiles. Three basic characteristics differentiate microprocessors:

- Instruction set:-The set of instructions that the microprocessor can execute.

- Bandwidth :- The number of bits processed in a single instruction.

- Clock speed:-Given in megahertz (MHz), the clock speed determines how many instructions per second the processor can execute. In both cases, the higher the value, the more powerful the CPU. For example, a 32-bit microprocessor that runs at 50MHz is more powerful than a 16-bit microprocessor that runs at 25MHz. In addition to bandwidth and clock speed, microprocessors are classified as being either RISC (reduced instruction set computer) or CISC (complex instruction set computer).

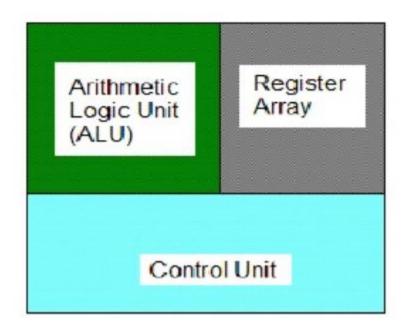

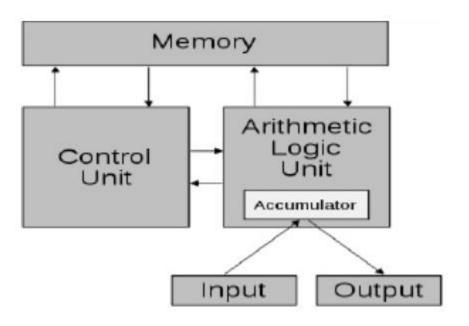

A microprocessor has three basic elements, as shown above. The ALU performs all arithmetic computations, such as addition, subtraction and logic operations (AND, OR, etc). It is controlled by the Control Unit and receives its data from the Register Array. The Register Array is a set of registers used for storing data. These registers can be accessed by the ALU very quickly. Some registers have specific functions - we will deal with these later. The Control Unit controls the entire process. It provides the timing and a control signal for getting data into and out of the registers and the ALU and it

## **CHAPTER 3**

# **METHODOLOGY**

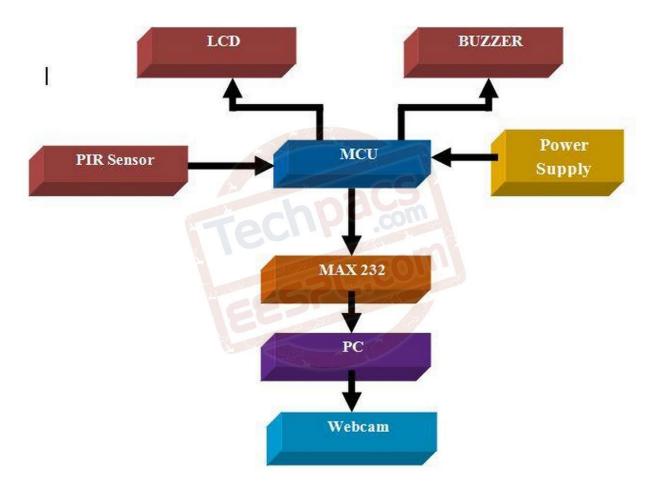

## **BLOCK DIAGRAM:**

- In the remote sensing Model, microcontroller is responsible for performing all the operations as it sends signals to the required devices.

- The microcontroller is connected to the power supply giving 220 V. As, microcontroller requires less voltage, this supply is converted into 5V by using step down transformer.

- Besides this, In order to convert the alternating current into Direct current the power supply is connected to the full wave rectifier. The

converted voltage is regulated by using the voltage regulator.

- Eventually, the microcontroller will receive regulated voltage and it is connected to LCD and Buzzer. LCD is used in this model to display the presence of any object and the buzzer will alert the user by producing alarming sound if anything is detected.

- The main role in sensing the persons is played by the PIR sensor which is connected to the microcontroller. The sensor works for the If within the range, any object in motion is detected by the sensor it will transmit the signal to microcontroller.

- After receiving the signal, microcontroller will pass the signal to the PC using serial communication. Simultaneously, it will send the signal to LCD and buzzer that will result in displaying the message of a object's detection on LCD and beeping sound by the buzzer.

- Afterwards, PC will retrieve the signal and transmits it to the MATLAB software wherein A GUI for this Model will be present. This GUI bears the responsibility of transmitting the signal to the webcam.

- As soon as the camera will get the signal, it will start recording the video for the set time period in the code. The captured video is stored in the data base and camera will get back to its original state i.e. it will wait for the next signal to capture any motion performed by the object. In this way the project will work and the person will be detected.

# HARDWARE METHODOLOGY

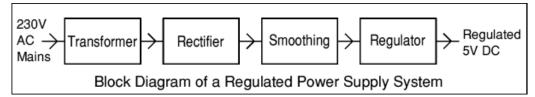

# **Regulated Power Supply**

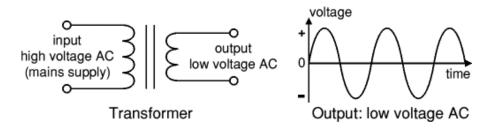

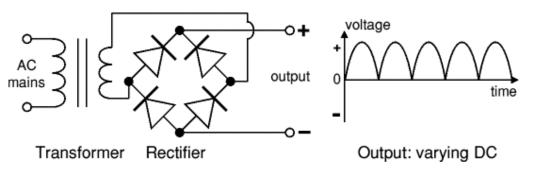

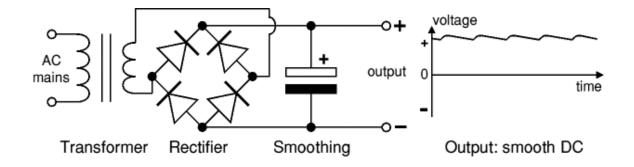

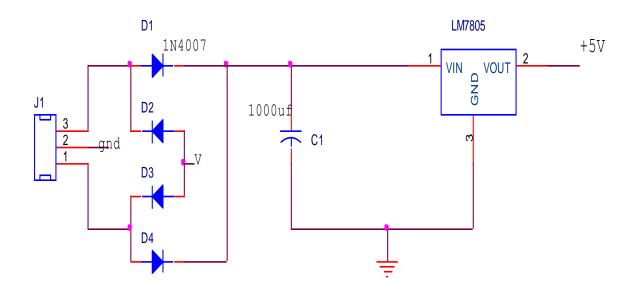

Power supplies are designed to convert high voltage AC mains to a suitable low voltage supply for electronic circuits and other devices. A power supply can be broken down into a series of blocks, each of which performs a particular function.

For example a 5V regulated supply:

Each of the blocks has its own function as described below

- 1. <u>Transformer</u> steps down high voltage AC mains to low voltage AC.

- 2. <u>Rectifier</u> converts AC to DC, but the DC output is varying.

- 3. <u>Smoothing</u> smoothes the DC from varying greatly to a small ripple.

- 4. <u>Regulator</u> eliminates ripple by setting DC output to a fixed voltage.

## Transformer

Transformers convert AC electricity from one voltage to another with little loss of power. Transformers work only with AC and this is one of the reasons why mains electricity is AC. The two types of transformers

- Step-up transformers increase voltage,

- Step-down transformers reduce voltage.

Most power supplies use a step-down transformer to

reduce the dangerously high mains voltage (230V in UK) to a safer low voltage. The input coil is called the primary and the output coil is called the secondary. There is no electrical connection between the two coils, instead they are linked by an alternating magnetic field created in the softiron core of the transformer. The two lines in the middle of the circuit symbol represent the core.

Transformers waste very little power so the power out is (almost) equal to the power in. Note that as voltage is stepped down current is stepped up. The ratio of the number of turns on each coil, called the turn ratio, determines the ratio of the voltages. A step-down transformer has a large number of turns on its primary (input) coil which is connected to the high voltage mains supply, and a small number of turns on its secondary (output) coil to give a low output voltage.

Turns Ratio =  $\frac{Vp}{Vs} = \frac{Np}{Ns}$

And

Power Out = Power In  $Vs \times Is = Vp \times Ip$ Where

Vp = primary (input) voltage

Np = number of turns on primary coil

Ip = primary (input) current

Ns = number of turns on secondary coil

Is = secondary (output) current

Vs = secondary (output) voltage

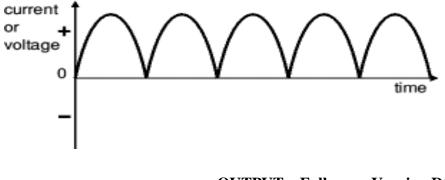

#### **Bridge Rectifier**

A bridge rectifier can be made using four individual diodes, but it is also available

in special packages containing the four diodes required. It is called a full-wave rectifier because it uses all AC wave (both positive and negative sections). 1.4V is used up in the bridge rectifier because each diode uses 0.7V when conducting and there are always two diodes conducting, as shown in the diagram below. Bridge rectifiers are rated by the maximum current they can pass and the maximum reverse voltage they can withstand (this must be at least three times the supply <u>RMS</u> voltage so the rectifier can withstand the peak voltages). In this alternate pairs of diodes conduct, changing over the connections so the alternating directions of AC are converted to the one direction of DC.

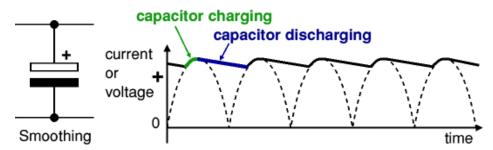

<u>OUTPUT – Full-wave Varying DC</u> SMOOTHING

Smoothing is performed by a large value <u>electrolytic capacitor</u> connected across the DC supply to act as a reservoir, supplying current to the output when the varying DC voltage from the rectifier is falling. The diagram shows the unsmoothed varying DC (dotted line) and the smoothed DC (solid line). The capacitor charges quickly near the peak of the varying DC, and then discharges as it supplies current to the output.

Note that smoothing significantly increases the average DC voltage to almost the peak value ( $1.4 \times RMS$  value). For example 6V RMS AC is rectified to full wave DC of about 4.6V RMS (1.4V is lost in the bridge rectifier), with smoothing this increases to almost the peak value giving  $1.4 \times 4.6 = 6.4V$  smooth DC.

Smoothing is not perfect due to the capacitor voltage falling a little as it discharges, giving a small ripple voltage. For many circuits a ripple which is 10% of the supply voltage is satisfactory and the equation below gives the required value for the smoothing capacitor. A larger capacitor will give fewer ripples. The capacitor value must be doubled when smoothing half-wave DC.

Smoothing capacitor for 10% ripple,  $C = 5 \times Io$

$Vs \times f$

Where

C =smoothing capacitance in farads (F)

Io = output current from the supply in amps (A)

Vs = supply voltage in volts (V), this is the peak value of the unsmoothed DC

f = frequency of the AC supply in hertz (Hz), 50Hz in the UK

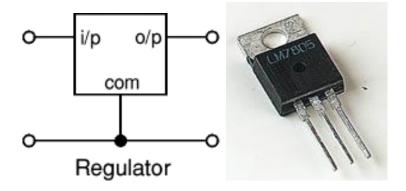

#### REGULATOR

Voltage regulator ICs are available with fixed (typically 5, 12 and 15V) or variable

output voltages. They are also rated by the maximum current they can pass. Negative voltage regulators are available, mainly for use in dual supplies. Most regulators include some automatic protection from excessive current ('overload protection') and overheating ('thermal protection'). Many of the fixed voltage regulator ICs has 3 leads and look like power transistors, such as the 7805 +5V 1A regulator shown on the right. They include a hole for attaching a heat sink if necessary.

#### Working of Power Supply

• Transformer

The low voltage AC output is suitable for lamps, heaters and special AC motors. It is not suitable for electronic circuits unless they include a rectifier and a smoothing capacitor.

• Transformer + Rectifier

The varying DC output is suitable for lamps, heaters and standard motors. It is not suitable for electronic circuits unless they include a smoothing capacitor.

• Transformer + Rectifier + Smoothing

The smooth DC output has a small ripple. It is suitable for most electronic circuits.

• Transformer + Rectifier + Smoothing + Regulator

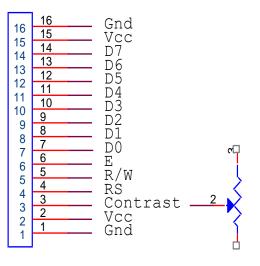

# (Liquid Crystal Display)

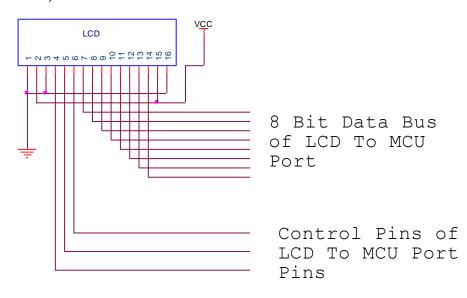

Liquid crystal displays (LCD) are widely used in recent years as compares to LEDs. This is due to the declining prices of LCD, the ability to display numbers, characters and graphics, incorporation of a refreshing controller into the LCD, their by relieving the CPU of the task of refreshing the LCD and also the ease of programming for characters and graphics. HD 44780 based LCDs are most commonly used.

The LCD, which is used as a display in the system, is LMB162A. The main features of this LCD are: 16 X 2 display, intelligent LCD, used for alphanumeric characters & based on ASCII codes. This LCD contains 16 pins, in which 8 pins are used as 8-bit data I/O, which are extended ASCII. Three pins are used as control lines these are Read/Write pin, Enable pin and Register select pin. Two pins are used for Backlight and LCD voltage, another two pins are for Backlight & LCD ground and one pin is used for contrast change.

| Pin | Symbol | I/O | Description                                                    |  |

|-----|--------|-----|----------------------------------------------------------------|--|

| 1   | VSS    | -   | Ground                                                         |  |

| 2   | VCC    | -   | +5V power supply                                               |  |

| 3   | VEE    | -   | Power supply to control contrast                               |  |

| 4   | RS     | Ι   | RS=0 to select command register, RS=1 to select data register. |  |

| 5   | R/W    | Ι   | R/W=0 for write, R/W=1 for read                                |  |

| 6   | Е      | I/O | Enable                                                         |  |

| 7   | DB0    | I/O | The 8 bit data bus                                             |  |

| 8   | DB1    | I/O | The 8 bit data bus                                             |  |

| 9   | DB2    | I/O | The 8 bit data bus                                             |  |

| 10  | DB3    | I/O | The 8 bit data bus                                             |  |

### LCD pin description

| 11 | DB4 | I/O | The 8 bit data bus |

|----|-----|-----|--------------------|

| 12 | DB5 | I/O | The 8 bit data bus |

| 13 | DB6 | I/O | The 8 bit data bus |

| 14 | DB7 | I/O | The 8 bit data bus |

### LCD pin description

The LCD discuss in this section has the most common connector used for the Hitachi 44780 based LCD is 14 pins in a row and modes of operation and how to program and interface with microcontroller is describes in this section.

LCD Pin Description Diagram

#### V<sub>CC</sub>, V<sub>SS</sub>, V<sub>EE</sub>

The voltage  $V_{CC}$  and  $V_{SS}$  provided by +5V and ground respectively while  $V_{EE}$  is used for controlling LCD contrast. Variable voltage between Ground and  $V_{cc}$  is used to specify the contrast (or "darkness") of the characters on the LCD screen.

#### **RS** (register select)

There are two important registers inside the LCD. The RS pin is used for their selection as follows. If RS=0, the instruction command code register is selected, then allowing to user to send a command such as clear display, cursor at home etc..

If RS=1, the data register is selected, allowing the user to send data to be displayed on the LCD.

## R/W (read/write)

The R/W (read/write) input allowing the user to write information from it. R/W=1, when it read and R/W=0, when it writing.

## EN (enable)

The enable pin is used by the LCD to latch information presented to its data pins. When data is supplied to data pins, a high power, a high-to-low pulse must be applied to this pin in order to for the LCD to latch in the data presented at the data pins.

## **D0-D7 (data lines)**

The 8-bit data pins, D0-D7, are used to send information to the LCD or read the contents of the LCD's internal registers. To displays the letters and numbers, we send ASCII codes for the letters A-Z, a-z, and numbers 0-9 to these pins while making RS = 1. There are also command codes that can be sent to clear the display or force the cursor to the home position or blink the cursor.

We also use RS =0 to check the busy flag bit to see if the LCD is ready to receive the information. The busy flag is D7 and can be read when R/W = 1 and RS =0, as follows: if R/W = 1 and RS =0, when D7 =1(busy flag =1), the LCD is busy taking care of internal operations and will not accept any information. When D7 =0, the LCD is ready to receive new information.

## Interfacing of micro controller with LCD display

In most applications, the "R/W" line is grounded. This simplifies the application because when data is read back, the microcontroller I/O pins have to be alternated between input and output modes.

In this case, "R/W" to ground and just wait the maximum amount of time for each instruction (4.1ms for clearing the display or moving the cursor/display to the "home position", 160 $\mu$ s for all other commands) and also the application software is simpler, it also frees up a microcontroller pin for other uses. Different LCD

execute instructions at different rates and to avoid problems later on (such as if the LCD is changed to a slower unit). Before sending commands or data to the LCD module, the Module must be initialized. Once the initialization is complete, the LCD can be written to with data or instructions as required. Each character to display is written like the control bytes, except that the "RS" line is set. During initialization, by setting the "S/C" bit during the "Move Cursor/Shift Display" command, after each character is sent to the LCD, the cursor built into the LCD will increment to the next position (either right or left). Normally, the "S/C" bit is set (equal to "1")

Interfacing of Microcontroller with LCD

#### LCD Command Code

| Code  | Command to LCD Instruction              |

|-------|-----------------------------------------|

| (HEX) | Register                                |

| 1     | Clear the display screen                |

| 2     | Return home                             |

| 4     | Decrement cursor(shift cursor to left)  |

| 6     | Increment cursor(shift cursor to right) |

| 7     | Shift display right                     |

| 8     | Shift display left                      |

|                   | 9  | Display off, cursor off                               |

|-------------------|----|-------------------------------------------------------|

|                   | А  | Display off, cursor on                                |

|                   | С  | Display on, cursor off                                |

| The original      | Е  | Display on, cursor blinking                           |

| model became far  | F  | Display on, cursor blinking                           |

| more popular      | 10 | Shift cursor position to left                         |

| than expected,    | 14 | Shift cursor position to right                        |

| selling uses such | 18 | Shift the entire display to left                      |

| as robotics       | 1C | Shift the entire display to right                     |

|                   | 80 | Force cursor to the beginning of 1 <sup>st</sup> line |

| outside of its    | C0 | Force cursor to the beginning of 2nd line             |

| target market.    | 38 | 2 line and 5×7 matrix                                 |

|                   |    |                                                       |

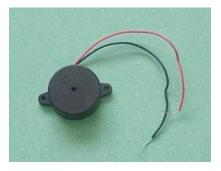

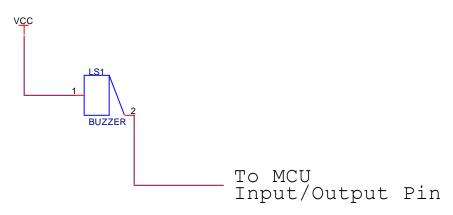

# **Buzzer for Beep Source**

A **buzzer** or **beeper** is an <u>audio</u> signaling device, which may be <u>mechanical</u>, <u>electromechanical</u>, or <u>piezoelectric</u>. Typical uses of buzzers and beepers include <u>alarm devices</u>, <u>timers</u> and confirmation of user input such as a mouse click or keystroke.

Buzzer

#### **Mechanical Buzzer**

A joy buzzer is an example of a purely mechanical buzzer.

A joy buzzer (also called a hand buzzer) is a <u>practical joke device</u> that consists of a coiled spring inside a disc worn in the palm of the hand. When the wearer shakes hands with another person, a button on the disc releases the spring, which rapidly unwinds creating a vibration that feels somewhat like an electric shock to someone not expecting it.

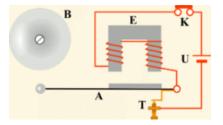

#### **Electromechanical Buzzer**

Early devices were based on an electromechanical system identical to an <u>electric</u> <u>bell</u> without the metal gong. Similarly, a <u>relay</u> may be connected to interrupt its own actuating <u>current</u>, causing the <u>contacts</u> to buzz. Often these units were anchored to a wall or ceiling to use it as a sounding board. The word "buzzer" comes from the rasping noise that electromechanical buzzers made.

An electric bell is a mechanical <u>bell</u> that functions by means of an <u>electromagnet</u>. When an <u>electric current</u> is applied, it produces a repetitive buzzing or clanging sound. Electric bells have been widely used at <u>railroad crossings</u>, in <u>telephones</u>, fire and <u>burglar alarms</u>, as <u>school bells</u>, <u>doorbells</u>, and alarms in industrial plants, but they are now being widely replaced with electronic sounders.

An electric buzzer uses a similar mechanism to an interrupter bell, but without the resonant bell. They are quieter than bells, but adequate for a warning tone over a small distance, such as across a desktop.

With the development of low cost electronics from the 1970s onwards, most buzzers have now been replaced by electronic 'sounders'. These replace the electromechanical striker of a bell with an electronic oscillator and a loudspeaker, often a <u>piezo transducer</u>.

**Piezoelectric buzzer**

A piezoelectric element may be driven by an oscillating electronic circuit or other audio signal source, driven with a piezoelectric audio amplifier. Sounds commonly used to indicate that a button has been pressed are a click, a ring or a beep.

Oscillation is the repetitive variation, typically in <u>time</u>, of some measure about a central value (often a point of <u>equilibrium</u>) or between two or more different states.

Familiar examples include swinging pendulum and AC power. a The term vibration is sometimes used more narrowly to mean a mechanical oscillation but sometimes is used to be synonymous with "oscillation". Oscillations occur not only in physical systems but also in **biological systems** and in human society. A piezoelectric audio amplifier (PAA) is a single integrated circuit or a PCB developed to amplify small audio signals to drive piezoelectric audio loudspeaker elements. A piezo audio amplifier can amplify a small signal sine wave of 1 volt peak-to-peak to a signal of about 30 or 60 Volts.

#### Uses

- Annunciate panels

- Electronic metronomes

- Game shows

- Microwave ovens and other household appliances

- Sporting events such as basketball games

- Electrical alarms

- Buzzers

#### **Interfacing Circuit to MCU**

# **Passive Infra Red Sensor**

A **passive Infrared sensor** (**PIR sensor**) is an electronic <u>sensor</u> that measures <u>infrared</u> (IR) light radiating from objects in its field of view. They are most often used in <u>PIR-based motion detectors</u>.

## **Operating Principle**

All objects above <u>absolute zero</u> emit <u>heat</u> energy in the form of infrared radiation (infrared light). Usually infrared light is invisible to the <u>human eye</u>, but it can be detected by electronic devices designed for such a purpose.

The term *passive* in this instance refers to the fact that PIR devices do not generate or radiate any energy for detection purposes. They work entirely by detecting the energy given off by other objects.

Construction

Infrared radiation enters through the front of the sensor, known as the *sensor face*. At the core of a PIR sensor is a <u>solid state</u> *sensor* or set of sensors, made from <u>pyroelectric</u> materials -- materials which generate energy when exposed to heat. Typically, the sensors are approximately 1/4 inch square, and take the form of a <u>thin film</u>. Materials commonly used in PIR sensors include <u>gallium nitride</u> (GaN), <u>caesium nitrate</u> (CsNO<sub>3</sub>), <u>polyvinyl fluorides</u>, derivatives of <u>phenylpyrazine</u>, and <u>cobalt phthalocyanine</u>. The sensor is often manufactured as part of an <u>integrated</u> circuit.

#### PIR based motion detector

A PIR-based <u>motion detector</u> is used to sense movement of people, animals, or other objects. They are commonly used in <u>burglar alarms</u> and automatically-activated <u>lighting</u> systems. They are commonly called simply "PIR", or sometimes "PID", for *passive infrared detector*.

#### Operation

Strictly speaking, individual PIR sensors do not detect motion; rather, they detect abrupt changes in temperature at a given point. As an object, such as a <u>human</u>, passes in front of the background, such as a <u>wall</u>, the temperature at that point will rise from <u>room temperature</u> to <u>body temperature</u>, and then back again. This quick change triggers the detection. Moving objects of identical temperature will not trigger detection.

PIDs can be equipped with more than one internal sensing element so that, with the appropriate electronics, it can detect the apparent direction of movement. As an object passes in front of adjacent sensors in turn, this implies the direction of movement. This may be used by on-board electronics to reduce false alarms, i.e., by requiring adjacent sensors to trip in succession. It may also be used to signal the direction of movement to a monitoring apparatus.

PIDs come in many configurations for a wide variety of applications. The most common models have numerous Fresnel lenses or mirror segments, an effective range of about thirty feet, and a field of view less than 180 degrees. Models with wider fields of view, including 360 degrees, are available -- typically designed to mount on a ceiling. Some larger PIDs are made with single segment mirrors and can sense changes in infrared energy over one hundred feet away from the PID. There are also PIDs designed with reversible orientation mirrors which allow either broad coverage (110° wide) or very narrow "curtain" coverage, or with individually selectable segments to "shape" the coverage.

#### **Differential detection**

Pairs of sensor elements may be wired as opposite inputs to a differential amplifier. In such a configuration, the PIR measurements cancel each other so that the average temperature of the field of view is removed from the electrical signal; an increase of IR energy across the entire sensor is self-cancelling and will not trigger the device. This allows the device to resist false indications of change in the event of being exposed to brief flashes of light or field-wide illumination. (Continuous high energy exposure may still be able to saturate the sensor materials

and render the sensor unable to register further information.) At the same time, this differential arrangement minimizes common-mode interference, allowing the device to resist triggering due to nearby electric fields. However, a differential pair of sensors cannot measure temperature in this configuration, and therefore is only useful for motion detection.

#### **Product design**

The PIR sensor is typically mounted on a <u>printed circuit board</u> containing the necessary electronics required to interpret the signals from the sensor itself. The complete assembly is usually contained within a housing, mounted in a location where the sensor can cover area to be monitored.

The housing will usually have a plastic "window" through which the infrared energy can enter. Despite often being only <u>translucent</u> to visible light, infrared energy is able to reach the sensor through the window because the plastic used is <u>transparent</u> to infrared radiation. The plastic window reduces the chance of foreign objects (dust, insects, etc.) from obscuring the sensor's field of view, damaging the mechanism, and/or causing <u>false alarms</u>. The window may be used as a filter, to limit the wavelengths to 8-14 micrometres, which is closest to the infrared radiation emitted by humans. It may also serve as a focusing mechanism; see below.

#### Focusing

Different mechanisms can be used to focus the distant infrared energy onto the sensor surface.

#### Lenses

The <u>plastic window covering</u> may have multiple facets molded into it, to focus the infrared energy onto the sensor. Each individual facet is a <u>Fresnel lens</u>.

#### Mirrors

Some PIDs are manufactured with internal, segmented <u>parabolic mirrors</u> to focus the infrared energy. Where mirrors are used, the plastic window cover generally has no Fresnel lenses molded into it. Motion detector module uses a motion detector IC and PCB mounted Fresnel lens (Item: SB0061)

#### General

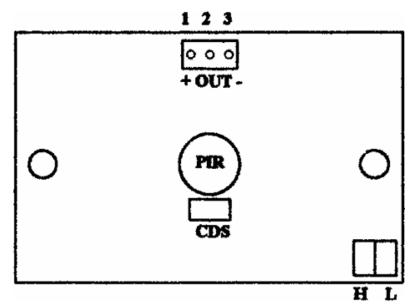

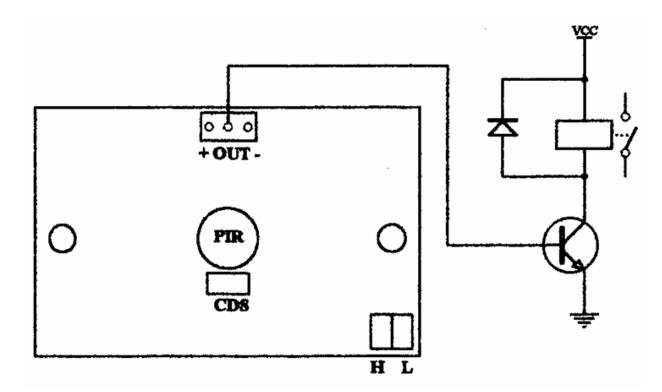

SB0061 is a pyroelectric sensor module which developed for human body detection. A PIR detector combined with a fresnel lens are mounted on a compact size PCB together with an analog IC, SB0061, and limited components to form the module. High level output of variable width is provided.

#### **Features and Electrical Specification**

- Compact size (28 x 38 mm)

- Supply current: DC5V-20V(can design DC3V-24V)

- Current drain :< 50uA (Other choice: DC0.8V-4.5V; Current drain: 1.5mA-0.1mA)

- Voltage Output: High/Low level signal : 3.3V (Other choice: Open-Collector Output)

- TTL output

- High sensitivity

- Delay time : 5s-18 minute

- Blockade time : 0.5s-50s (acquiescently 0 seconds)

- Operation Temperature: -15oC -70Oc

- Infrared sensor: dual element, low noise, high sensitivity

- Light sensor: CdS photocell (can be add as customer requirement)

# Lens information

# **Application Note**

- 1. Power anode

- 2. Output: High level signal

- 3. Power cathode

- H: Can be spring repeatedly

- L: Can not be spring repeatedly

- CDS: Photocell

#### Note

Due to the high sensitivity of PIR sensor device, it is not recommended to use the module in the following or similar condition.

- A) in rapid environmental changes

- B) in strong shock or vibration

C) in a place where there are obstructing material (eg. glass) through which IR cannot pass within detection area.

- D) exposed to direct sun light

- E) exposed to direct wind from a heater or air condition

(e)

# Microcontroller AVR Mega Series

#### **Embedded System**

An embedded system is a system which is going to do a predefined specified task is the embedded system and is even defined as combination of both software and hardware. A general-purpose definition of embedded systems is that they are devices used to control, monitor or assist the operation of equipment, machinery or plant. "Embedded" reflects the fact that they are an integral part of the system. At the other extreme a general-purpose computer may be used to control the operation of a large complex processing plant, and its presence will be obvious .All embedded systems are including computers or microprocessors. Some of these computers are however very simple systems as compared with a personal computer. The very simplest embedded systems are capable of performing only a single function or set of functions to meet a single predetermined purpose. In more complex systems an application program that enables the embedded system to be used for a particular purpose in a specific application determines the functioning of the embedded system. The ability to have programs means that the same embedded system can be used for a variety of different purposes. In some cases a microprocessor may be designed in such a way that application software for a particular purpose can be added to the basic software in a second process, after which it is not possible to make further changes. The applications software on such processors is sometimes referred to as firmware .The simplest devices consist of a single microprocessor (often called a "chip"), which may itself be packaged with other chips in a hybrid system or Application Specific Integrated Circuit (ASIC). Its input comes from a detector or sensor and its output goes to a switch or activator which (for example) may start or stop the operation of a machine or, by operating a valve, may control the flow of fuel to an engine.

As the embedded system is the combination of both software and hardware

|                                        | Embedded System                                    |

|----------------------------------------|----------------------------------------------------|

| Software                               | Hardware                                           |

| <ul> <li>∧ ALP</li> <li>∧ C</li> </ul> | <ul> <li>Processor</li> <li>Peripherals</li> </ul> |

| • VB<br>Etc.,                          | o memory                                           |

Block diagram of Embedded System

Software deals with the languages like ALP, C, and VB etc., and Hardware deals with Processors, Peripherals, and Memory.

Memory: It is used to store data or address.

Peripherals: These are the external devices connected

**Processor:** It is an IC which is used to perform some task

# Applications of embedded systems

- Manufacturing and process control

- Construction industry

- Transport

- Buildings and premises

- Domestic service

- Communications

- Office systems and mobile equipment

- Banking, finance and commercial

- Medical diagnostics, monitoring and life support

- Testing, monitoring and diagnostic systems

# Processors are classified into four types like:

• Micro Processor (µp)

- Micro controller (µc)

- Digital Signal Processor (DSP)

- Application Specific Integrated Circuits (ASIC)

#### Micro Processor (µp):

A silicon chip that contains a CPU is called MPU. In the world of personal computer the terms microprocessor and CPU are used interchangeably. At the heart of all personal computers and most workstations sits a microprocessor. Microprocessors also control the logic of almost all digital devices, from clock radios to fuel-injection systems for automobiles. Three basic characteristics differentiate microprocessors:

- Instruction set:-The set of instructions that the microprocessor can execute.

- Bandwidth :- The number of bits processed in a single instruction.

- Clock speed:-Given in megahertz (MHz), the clock speed determines how many instructions per second the processor can execute. In both cases, the higher the value, the more powerful the CPU. For example, a 32-bit microprocessor that runs at 50MHz is more powerful than a 16-bit microprocessor that runs at 25MHz. In addition to bandwidth and clock speed, microprocessors are classified as being either RISC (reduced instruction set computer) or CISC (complex instruction set computer).

- A microprocessor has three basic elements, as shown above. The ALU performs all arithmetic computations, such as addition, subtraction and logic operations (AND, OR, etc). It is controlled by the Control Unit and receives its data from the Register Array. The Register Array is a set of registers used for storing data. These registers can be accessed by the ALU very quickly. Some registers have specific functions we will deal with these later. The Control Unit controls the entire process. It provides the timing and a control signal for getting data into and out of the registers and the ALU and it synchronizes the execution of instructions (we will deal with instruction execution at a later date)

## **Three Basic Elements of a Microprocessor**

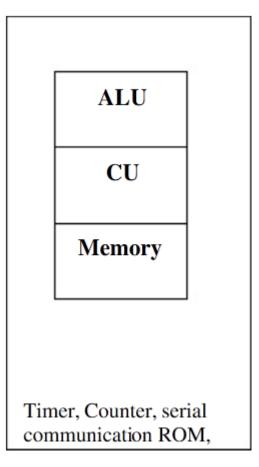

## Micro Controller (µc)

A microcontroller is a small computer on a single integrated circuit containing a processor core, memory, and programmable input/output peripherals. Program memory in the form of NOR flash or OTP ROM is also often included on chip, as well as a typically small amount of RAM. Microcontrollers are designed for embedded applications, in contrast to the microprocessors used in personal computers or other general purpose applications.

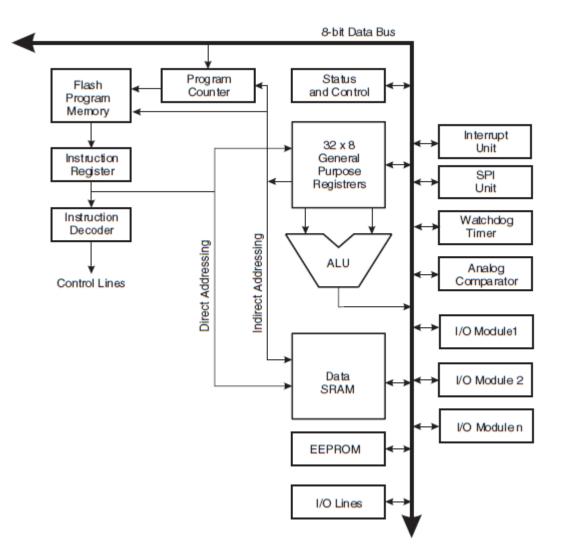

Figure: Block Diagram of Micro Controller (µc)

# **Digital Signal Processors (DSPs)**

Digital Signal Processors is one which performs scientific and mathematical operation. Digital Signal Processor chips - specialized microprocessors with architectures designed specifically for

The types of operations required in digital signal processing. Like a general-purpose microprocessor, a DSP is a programmable device, with its own native instruction code. DSP chips are capable of carrying out millions of floating point operations per second, and like their better-known general-purpose cousins, faster and more powerful versions are continually being introduced. DSPs can also be embedded within complex "system-on-chip" devices, often containing both analog and digital circuitry.

# Application Specific Integrated Circuit (ASIC)

ASIC is a combination of digital and analog circuits packed into an IC to achieve the desired control/computation function

• CPU cores for computation and control

- Peripherals to control timing critical functions

- Memories to store data and program

- Analog circuits to provide clocks and interface to the real world which is analog in nature

- I/Os to connect to external components like LEDs, memories, monitors etc.

**Computer Instruction Set**

#### There are two different types of computer instruction set there are:

- 1. RISC (Reduced Instruction Set Computer)

- 2. CISC (Complex Instruction Set computer)

# **Reduced Instruction Set Computer (RISC)**

- Reduced Instruction Set Computer

- As compared to Complex Instruction Set Computers, i.e. x86

- Assumption: Simpler instructions execute faster

- Optimized most used instructions

- Other RISC machines: ARM, PowerPC, SPARC

A RISC (reduced instruction set computer) is a microprocessor that is designed to perform a smaller number of types of computer instruction so that it can operate at a higher speed (perform more million instructions per second, or millions of instructions per second). Since each instruction type that a computer must perform requires additional transistors and circuitry, a larger list or set of computer instructions tends to make the microprocessor more complicated and slower in operation. Besides performance improvement, some advantages of RISC and related design improvements are

- A new microprocessor can be developed and tested more quickly if one of its aims is to be less complicated.

- Operating system and application programmers who use the microprocessor's instructions will find it easier to develop code with a smaller instruction set.

- The simplicity of RISC allows more freedom to choose how to use the space on a microprocessor. Higher-level language compilers produce more efficient code than

formerly because they have always tended to use the smaller set of instructions to be found in a RISC computer.

## **RISC characteristics**

# Simple instruction set

In a RISC machine, the instruction set contains simple, basic instructions, from which more. Complex instructions can be composed.

# Same length instructions

Each instruction is the same length, so that it may be fetched in a single operation. Most instructions complete in one machine cycle, which allows the processor to handle several instructions at the same time. This pipelining is a key technique used to speed up RISC machines.

# **Complex Instruction Set Computer (CISC)**

CISC, which stands for Complex Instruction Set Computer, is a philosophy for designing chips that are easy to program and which make efficient use of memory. Each instruction in a CISC instruction set might perform a series of operations inside the processor. This reduces the number of instructions required to implement a given program, and allows the programmer to learn a small but flexible set of instructions.

#### The advantages of CISC

At the time of their initial development, CISC machines used available technologies to optimize computer performance.

• Microprogramming is as easy as assembly language to implement, and much less expensive than hardwiring a control unit.

• The ease of micro-coding new instructions allowed designers to make CISC machines upwardly compatible: a new computer could run the same programs as earlier computers because the new computer would contain a superset of the instructions of the earlier computers.

• As each instruction became more capable, fewer instructions could be used to implement a given task. This made more efficient use of the relatively slow main memory.

• Because micro program instruction sets can be written to match the constructs of highlevel languages, the compiler does not have to be as complicated.

### **Disadvantages of CISC**

Still, designers soon realized that the CISC philosophy had its own problems, including:

- Earlier generations of a processor family generally were contained as a subset in every new version --- so instruction set & chip hardware become more complex with each generation of computers.

- So that as many instructions as possible could be stored in memory with the least possible wasted space, individual instructions could be of almost any length----this means that different instructions will take different amounts of clock time to execute, slowing down the overall performance of the machine.

- Many specialized instructions aren't used frequently enough to justify their existence --- approximately 20% of the available instructions are used in a typical program.

- CISC instructions typically set the condition codes as a side effect of the instruction. Not only does setting the condition codes take time, but programmers have to remember to examine the condition code bits before a subsequent instruction changes them.

# **Memory Architecture**

There two different type's memory architectures there are:

- Harvard Architecture

- Von-Neumann Architecture

# **Harvard Architecture**

Computers have separate memory areas for program instructions and data. There are two or more internal data buses, which allow simultaneous access to both instructions and data. The CPU fetches program instructions on the program memory bus.

The **Harvard architecture** is computer architecture with physically separate storage and signal pathways for instructions and data. The term originated from the Harvard Mark Irelay-based computer, which stored instructions on punched tape (24 bits wide) and data in electromechanical counters. These early machines had limited data storage, entirely contained within the central processing unit and provided no access to the instruction storage as data. Programs

needed to be loaded by an operator, the processor could not boot itself.

#### Harvard Architecture Modern uses of the Harvard architecture

#### Modern uses of the Harvard architecture

The principal advantage of the pure Harvard architecture - simultaneous access to more than one memory system - has been reduced by modified Harvard processors using modern CPU cache systems. Relatively pure Harvard architecture machines are used mostly in applications where tradeoffs, such as the cost and power savings from omitting caches, outweigh the programming penalties from having distinct code and data address spaces.

- Digital signal processors (DSPs) generally execute small, highly-optimized audio or video processing algorithms. They avoid caches because their behavior must be extremely reproducible. The difficulties of coping with multiple address spaces are of secondary concern to speed of execution. As a result, some DSPs have multiple data memories in distinct address spaces to facilitate SIMD and VLIW processing. Texas Instruments TMS320 C55x processors, as one example, have multiple parallel data busses (two write, three read) and one instruction bus.

- Microcontrollers are characterized by having small amounts of program (flash memory) and data (SRAM) memory, with no cache, and take advantage of the Harvard architecture to speed processing by concurrent instruction and data access. The separate storage means the program and data memories can have different bit depths, for example using 16-bit wide instructions and 8-bit wide data. They also mean that

instruction pre-fetch can be performed in parallel with other activities. Examples include, the AVR by Atmel Corp, the PIC by Microchip Technology, Inc. and the ARM Cortex-M3 processor (not all ARM chips have Harvard architecture). Even in these cases, it is common to have special instructions to access program memory as data for read-only tables, or for reprogramming.

#### **Von-Neumann Architecture**

A computer has a single, common memory space in which both program instructions and data are stored. There is a single internal data bus that fetches both instructions and data. They cannot be performed at the same time The von Neumann architecture is a design model for a stored-program digital computer that uses a central processing unit (CPU) and a single separate storage structure ("memory") to hold both instructions and data. It is named after the mathematician and early computer scientist John von Neumann. Such computers implement a universal Turing machine and have a sequential architecture.

A stored-program digital computer is one that keeps its programmed instructions, as well as its data, in read-write, random-access memory (RAM). Stored-program computers were advancement over the program-controlled computers of the 1940s, such as the Colossus and the ENIAC, which were programmed by setting switches and inserting patch leads to route data and to control signals between various functional units. In the vast majority of modern computers, the same memory is used for both data and program instructions. The mechanisms for transferring the data and instructions between the CPU and memory are, however, considerably more complex than the original von Neumann architecture. The terms "von Neumann architecture" and "stored-program computer" are generally used interchangeably, and that usage is followed in this article.

Schematic of the Von-Neumann Architecture

#### **Basic Difference between Harvard and Von-Neumann Architecture**

- The primary difference between Harvard architecture and the Von Neumann architecture is in the Von Neumann architecture data and programs are stored in the same memory and managed by the same information handling system.

- Whereas the Harvard architecture stores data and programs in separate memory devices and they are handled by different subsystems.

- In a computer using the Von-Neumann architecture without cache; the central processing unit (CPU) can either be reading and instruction or writing/reading data to/from the memory. Both of these operations cannot occur simultaneously as the data and instructions use the same system bus.

- In a computer using the Harvard architecture the CPU can both read an instruction and access data memory at the same time without cache. This means that a computer with Harvard architecture can potentially be faster for a given circuit complexity because data access and instruction fetches do not contend for use of a single memory pathway.

- Today, the vast majority of computers are designed and built using the Von Neumann architecture template primarily because of the dynamic capabilities and efficiencies gained in designing, implementing, operating one memory system as opposed to two.

Von Neumann architecture may be somewhat slower than the contrasting Harvard Architecture for certain

- Specific tasks, but it is much more flexible and allows for many concepts unavailable to Harvard architecture such as self programming, word processing and so on.

- Harvard architectures are typically only used in either specialized systems or for very specific uses. It is used in specialized digital signal processing (DSP), typically for video and audio processing products. It is also used in many small microcontrollers used in electronics applications such as Advanced RISK Machine (ARM) based products for many vendors

## What is AVR?

- Modified Harvard architecture 8-bit RISC single chip microcontroller

- Complete System-on-a-chip

- On Board Memory (FLASH, SRAM & EEPROM)

- On Board Peripherals

- Advanced (for 8 bit processors) technology

- Developed by Atmel in 1996

- First In-house CPU design by Atmel

# **AVR Family**

• 8 Bit tinyAVR

Small package – as small as 6 pins

• 8 Bit megaAVR

Wide variety of configurations and packages

• 8 / 16 Bit AVR XMEGA

Second Generation Technology

• 32 Bit AVR UC3

Higher computational throughput

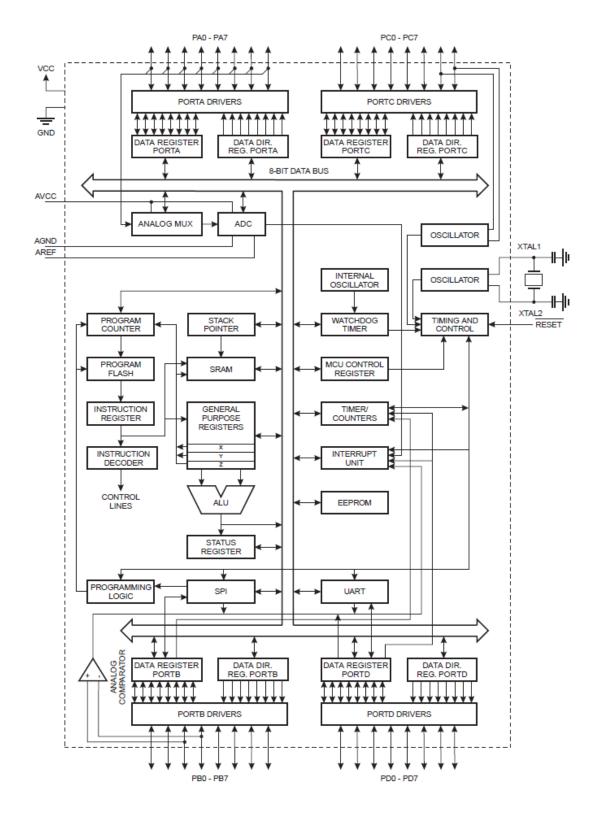

**Overview:** The ATmega8535 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing instructions in a single clock cycle, the ATmega8535 achieves throughputs approaching 1 MIPS per MHz allowing the system designed to optimize power consumption versus processing speed.

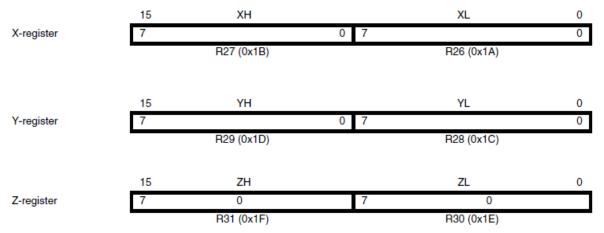

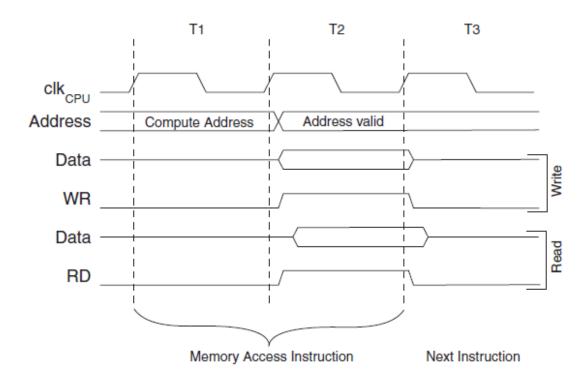

The AVR core combines a rich instruction set with 32 general purpose working registers. All 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

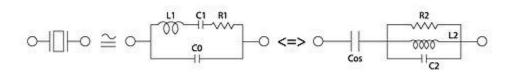

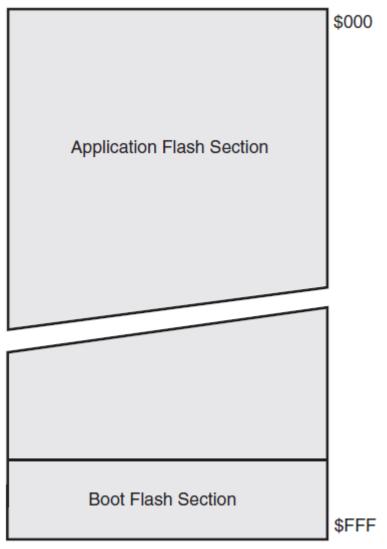

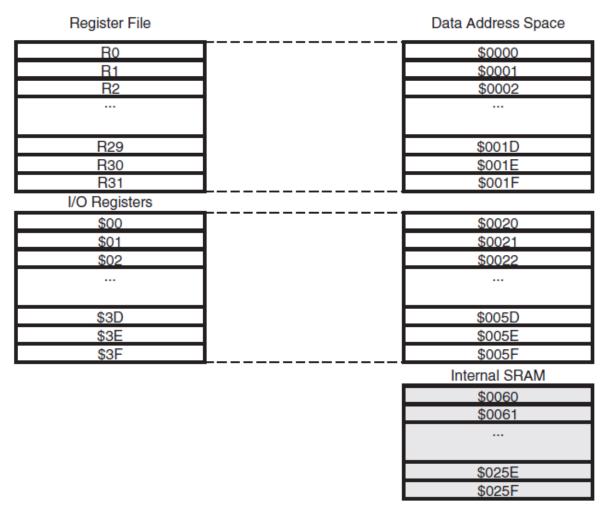

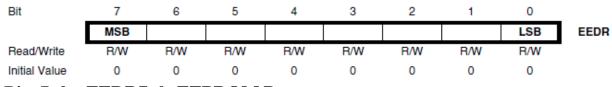

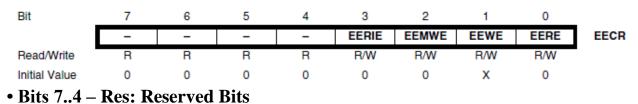

The ATmega8535 provides the following features: 8K bytes of In-System Programmable Flash with Read-While-Write capabilities, 512 bytes EEPROM, 512 bytes SRAM, 32 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain in TQFP package, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the asynchronous timer continue to run.

The device is manufactured using Atmel's high density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be

reprogrammed In-System through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega8535 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega8535 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, In Circuit Emulators, and evaluation kits.

**AT90S8535 Compatibility** The ATmega8535 provides all the features of the AT90S8535. In addition, several new features are added. The ATmega8535 is backward compatible with AT90S8535 in most cases. However, some incompatibilities between the two microcontrollers exist. To solve this problem, an AT90S8535 compatibility mode can be selected by programming the S8535C fuse. ATmega8535 is pin compatible with AT90S8535, and can replace the AT90S8535 on current Printed Circuit Boards. However, the location of fuse bits and the electrical characteristics differs between the two devices.

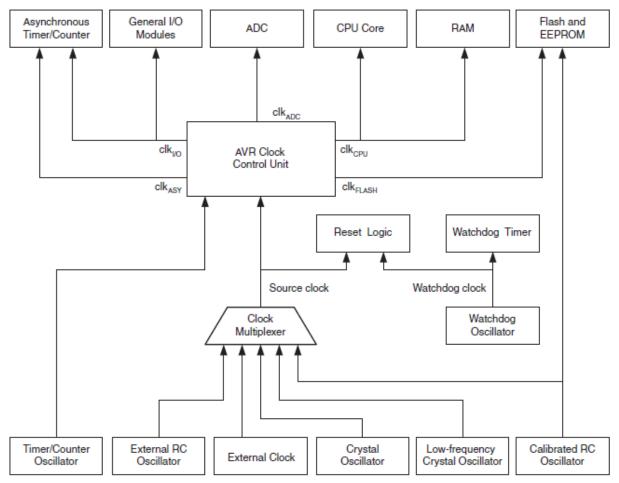

#### **Block Diagram**

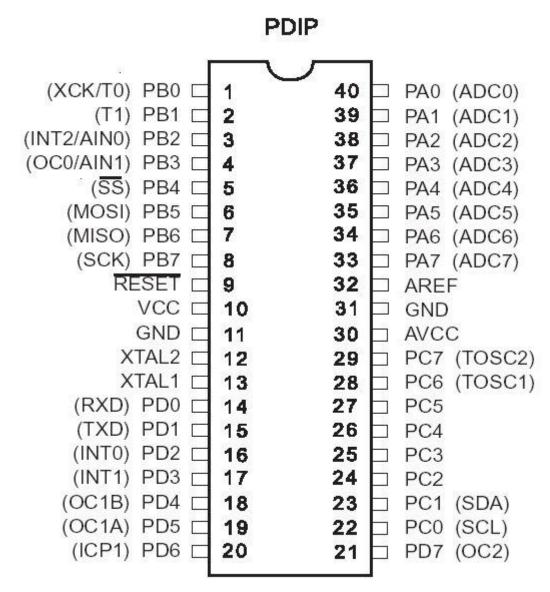

**Pin Description**

#### **Pin Descriptions**

VCC: Digital supply voltage

GND: Ground

**Port A (PA7..PA0)** Port A serves as the analog inputs to the A/D Converter.

Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

**Port B** (**PB7..PB0**) Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

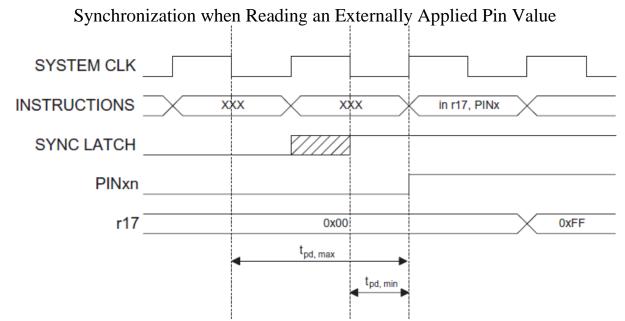

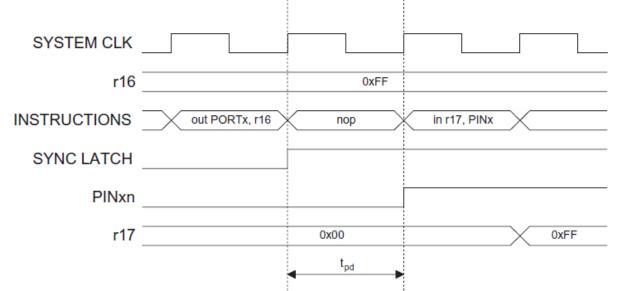

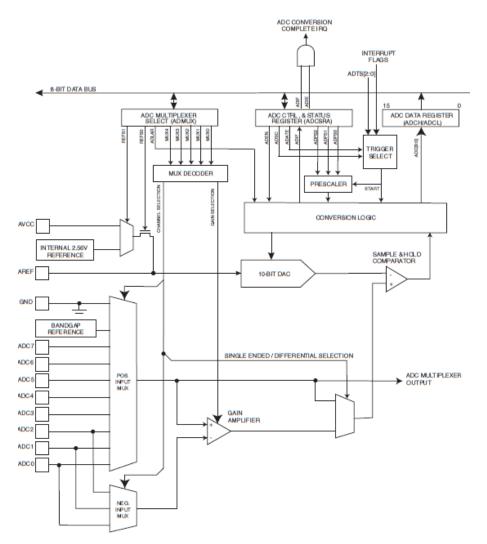

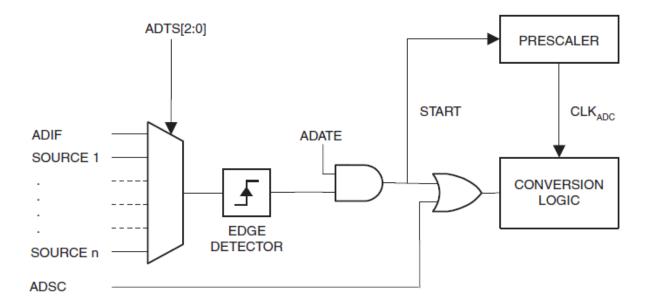

**Port C (PC7..PC0)** Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.