# Visvesvaraya Technological University, Belagavi.

#### PROJECT REPORT

on

### "NAND FLASH BASED IN-FLIGHT ACQUISITION AND RECORDING UNIT FOR ACCELERATION SENSOR ASSEMBLY OF FLIGHT CONTROL SYSTEM"

Project Report submitted in partial fulfillment of the requirement for the award of the degree of Bachelor of Engineering

in

**Electronics and Communication Engineering**

For the academic year 2019-20

Submitted by

#### USN

#### Name

1CR16EC027 1CR16EC052 Bhavana R Reddy Hrusna Chakri Shadakshri.V

Under the guidance of

Internal Guide Dr. Sharmila K. P Professor Department of ECE CMRIT, Bengaluru-560 037. External Guide Mr.E. Krishna Kishore, Mr.Rajesh Kumar Garg Scientist 'D' ADA Bengaluru -560 017.

Department of Electronics and Communication Engineering CMR Institute of Technology, Bengaluru – 560 037

Tel. : +91-80-25087002 / 25087566 25087777 / 25087555

**AERONAUTICAL DEVELOPMENT AGENCY**

(Ministry of Defence, Govt. of India) PB No. 1718, Vimanapura Post, Bangalore - 560 017, India

30<sup>th</sup> June 2020

#### **CERTIFICATE**

This is to Certify that Ms. Bhavana R Reddy (1CR16EC027) and Ms. Hrusna Chakri Shadakshri V (1CR16EC052) pursuing B.E. in Electronics and Communication Engineering has completed the project "NAND Flash Based In-Flight Acquisition And Recording Unit For Acceleration Sensor Assembly of Flight Control System" successfully at Aeronautical Development Agency (ADA), Autonomous Body —Ministry of Defence, Govt. of India P.B. No. 1718, Vimanapura Post, Bengaluru - 560 017 from 16<sup>th</sup> Sept. 2019 to 5<sup>th</sup> June 2020.

External Guide

Mr. Rajesh Kumar Garg, Scientist/Engineer 'D', Aeronautical Development Agency (ADA)

#### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

#### <u>CERTIFICATE</u>

This is to Certify that the dissertation work "NAND Flash Based In-Flight Acquisition And Recording Unit For Acceleration Sensor Assembly Of Flight Control System" carried out by Bhavana R Reddy, 1CR16EC027, Hrusna Chakri Shadakshri V, 1CR16EC052, bonafide students of CMRIT in partial fulfillment for the award of Bachelor of Engineering in Electronics and Communication Engineering of the Visvesvaraya Technological University, Belagavi, during the academic year 2019-20. It is certified that all corrections/suggestions indicated for internal assessment have been incorporated in the report deposited in the departmental library. The project report has been approved as it satisfies the academic requirements in respect of Project work prescribed for the said degree.

Signature of Guide

Signature of HOD

Signature of Principal

Dr. Sharmila K. P, Professor, Dept. of ECE., CMRIT, Bengaluru. Dr. R. Elumalai Head of the Department, Dept. of ECE., CMRIT, Bengaluru. Dr. Sanjay Jain Principal, CMRIT, Bengaluru.

Signature & date

External Viva Name of Examiners 1. 2

## **ACKNOWLEDGEMENT**

The satisfaction and euphoria that accompanies the successful completion of any task would be incomplete without mentioning the people, whose consistent guidance and encouragement has served as a beacon and crowned my efforts with success.

We take an opportunity to thank all the distinguished personalities for their enormous and precious support and encouragement throughout the duration of this seminar.

We take this opportunity to express our sincere gratitude and respect to CMR Institute of Technology, Bengaluru for providing us an opportunity to carry out our project work.

We express our gratitude to Principal **Dr. Sanjay Jain**, Principal, CMRIT, Bengaluru, for having provided me the golden opportunity to undertake this project work in their esteemed organization.

We sincerely thank **Dr. R. Elumalai**, HOD, Department of Electronics and Communication Engineering, CMR Institute of Technology for the immense support given to me. We express our warm thanks to our guide **Mr. E. Krishna Kishore & Mr. Rajesh Kumar Garg**, Scientist 'D', Aeronautical Development Agency, Bengaluru-17, for their skillful guidance, constant supervision, timely suggestions and constructive criticism in the successful completion of project work in time.

We express our gratitude to our project guide **Dr. Sharmila K. P**, Professor, Department of Electronics and Communication Engineering, CMRIT, Bengaluru. for their support, guidance, and suggestions throughout the project work. Their guidance gave us the environment to enhance our knowledge, skills, and to reach the pinnacle with sheer determination, dedication, and hard work.

We also extend our thanks to the faculties of Electronics and Communication Engineering Department who directly or indirectly encouraged us throughout the course of project work.

Last but not the least, heartful thanks to our parents and friends for all their moral support they have given us during the completion of this work.

# TABLE OF CONTENTS

| CHAPTER 1                                | 1  |

|------------------------------------------|----|

| INTRODUCTION                             | 1  |

| 1.1 Requirement of ECC in NAND Flash     | 2  |

| 1.2 Overview of BCH                      | 3  |

| 1.3 Motivation                           | 3  |

| 1.4 Objectives                           | 4  |

| CHAPTER 2                                | 5  |

| LITERATURE SURVEY                        | 5  |

| 2.1 LCA-FCS, DFCC                        | 5  |

| 2.2 Accelerometer Sensor Assembly (ASA)  | 6  |

| 2.3 Data Integrity:                      | 7  |

| 2.3.1 Data integrity vs. Data security:  | 7  |

| 2.4 Error Control Coding                 | 8  |

| 2.4.1 Linear Block Codes                 | 9  |

| 2.5 Galois Field (GF):                   | 10 |

| 2.5.1 Properties of Galois Field         | 11 |

| 2.5.2 Galois field GF(2) "Binary Field"  | 11 |

| 2.5.3 Extension Fields                   | 12 |

| 2.6 BCH Codes                            | 13 |

| 2.6.1 BCH Merits:                        | 13 |

| 2.6.2 BCH Demerits:                      | 14 |

| 2.6.3 Some examples of BCH Applications: | 15 |

| 2.7 BCH Encoder                          | 15 |

| 2.7.1 Code generation:                   | 15 |

| 2.7.2 Primitive Polynomials:             | 16 |

| 2.7.3 Minimal Polynomials:               | 17 |

| 2.8 BCH Decoder                                                            | 17 |

|----------------------------------------------------------------------------|----|

| 2.8.1 Algebraic Decoding                                                   | 17 |

| A. Peterson-Gorenstein-Zierler Decoding                                    | 17 |

| B. The Berlekamp-Massey Decoding Algorithm                                 | 19 |

| C. Sugiyama's Euclidean Decoding Algorithm                                 | 21 |

| 2.8.2 Chien Search Algorithms                                              | 23 |

| CHAPTER 3                                                                  | 28 |

| HARDWARE                                                                   | 28 |

| 3.1 Acquisition and Recording Unit (ARU)                                   | 28 |

| 3.2 System Initialization                                                  | 29 |

| 3.3 NAND Flash Controller                                                  | 30 |

| 3.1.1 Data integrity for ASA-ARU:                                          | 32 |

| 3.2 FPGA-ARTIX 7:                                                          | 32 |

| 3.3 NAND Flash Memory                                                      | 35 |

| 3.3.1 Types of NAND:                                                       | 36 |

| CHAPTER 4                                                                  | 38 |

| SOFTWARE                                                                   | 38 |

| 4.1 ECC for NAND Flash                                                     | 38 |

| 4.1.1 Data Recording – NAND Flash                                          | 39 |

| 4.2 BCH Codes in ASA-ARU Application                                       | 40 |

| 4.3 BCH Encoder                                                            | 41 |

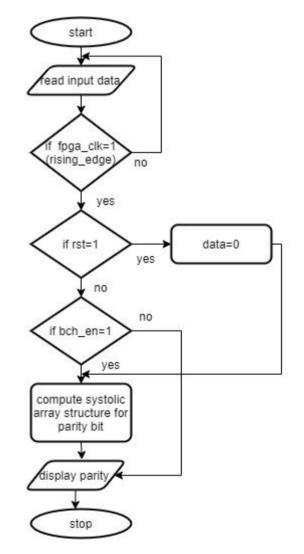

| 4.3.1 Design and Implementation of Systolic- Array type Binary BCH Encoder | 42 |

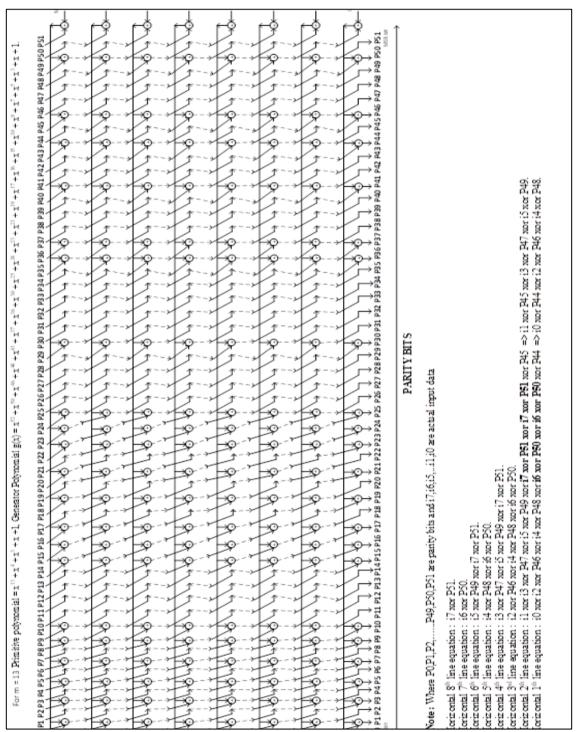

| A. Generator Polynomial                                                    | 42 |

| B. Construction of BCH (8191,8139,4) Encoder                               | 43 |

| 4.4 BCH Decoder                                                            | 45 |

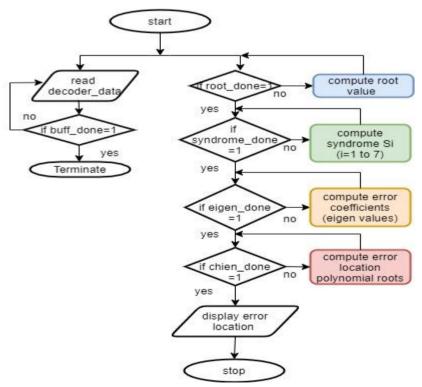

| 4.4.1 Design and Implementation Binary BCH Decoder                         | 45 |

| A. Galois Field roots generation                                           | 45 |

| B. Syndrome calculation                                                    | 45 |

|                                                                            |    |

| C. Coefficients of error locator polynomial                                  | 46 |

|------------------------------------------------------------------------------|----|

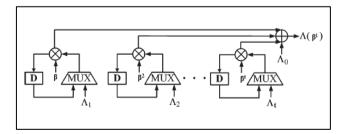

| D. Roots of $\Lambda(\varkappa)$                                             | 47 |

| CHAPTER 5                                                                    | 49 |

| RESULTS                                                                      | 49 |

| 5.1 Simulation results of BCH(8191,8139,4) Encoder                           | 49 |

| 5.2 Performance Comparison of Conventional and Parallel BCH(63,39,4) Encoder | 49 |

| 5.3 Simulation Results of BCH Decoder                                        | 51 |

| CHAPTER 6                                                                    | 53 |

| APPLICATIONS AND ADVANTAGES                                                  | 53 |

| 6.1 Applications of BCH codes                                                | 53 |

| 6.1.1 Digital Communications and Storage                                     | 53 |

| 6.1.2 BCH Codes as Industry Standards                                        | 53 |

| 6.1.3 BCH Code in image encryption                                           | 54 |

| 6.1.4 Error-free Communication in NB-IoT                                     | 55 |

| 6.2 Advantages                                                               | 56 |

| CHAPTER 7                                                                    | 57 |

| CONCLUSIONS AND SCOPE FOR FUTURE WORK                                        | 57 |

| REFERENCES                                                                   | 58 |

| APPENDIX A                                                                   | 59 |

| BCH Encoder: Module definition                                               | 59 |

| BCH Encoder: Test Bench                                                      | 63 |

| APPENDIX B                                                                   | 68 |

| BCH Decoder: Module Definition                                               | 68 |

| BCH Decoder: Test Bench                                                      | 87 |

| APPENDIX C                                                                   | 94 |

| Verification using built-in matlab function:                                 | 94 |

## LIST OF FIGURES

| Figure 1. ASA interface with DFCC                                                      | 1     |

|----------------------------------------------------------------------------------------|-------|

| Figure 2.1: Aircraft Flight Control System                                             | 5     |

| Figure 2.2: Cantilever Capacitor Output                                                | 7     |

| Figure 2.3: Classification of ECC                                                      | 8     |

| Figure 2.4 Systematic form of codeword of a linear block code                          | 10    |

| Figure 2.5: The Peterson-Gorenstein-Zierler Algorithm Flowchart                        | 19    |

| Figure 2.6: BMA Algorithm with flowchart                                               | 20    |

| Figure 2.7(a) : Conventional Chien search circuit                                      | 23    |

| Figure 2.7(b) : p-parallel Chien search architecture: direct unfolded version          | 24    |

| Figure 2.7(c) : p-parallel Chien search architecture: equivalent architecture with sho | orter |

| critical path                                                                          | 24    |

| Figure 2.8 Basic components in Chien search architecture(a) MPCNj(b) BTj (c) GBT       | 25    |

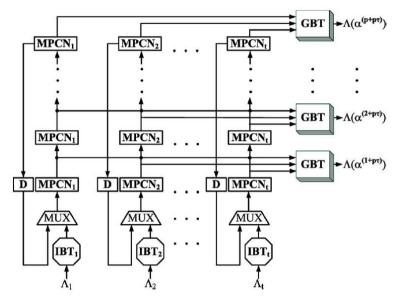

| Figure 2.9 MPCN-based parallel-p Chien search architecture.                            | 26    |

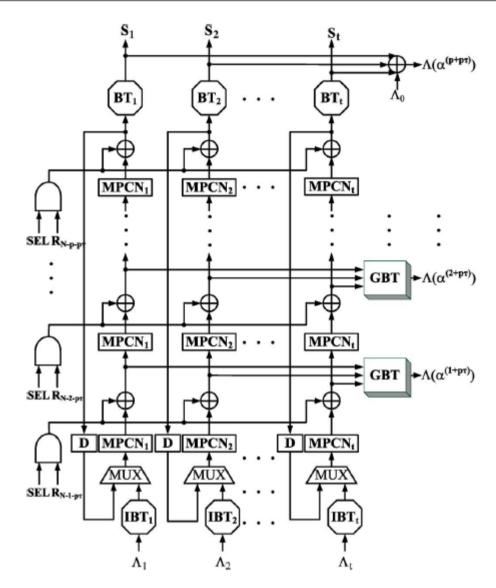

| Figure 2.10 Parallel-p joint syndrome calculator and Chien search with MPCN ba         | ased  |

| architecture.                                                                          | 27    |

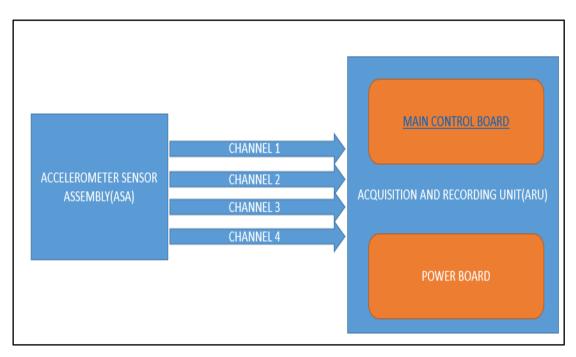

| Figure 3.1 ASA-ARU system interface with ASA-LRU                                       | 28    |

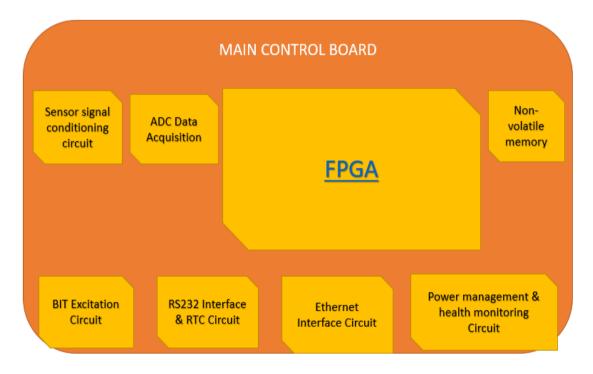

| Figure 3.2 ASA-ARU system-Main Control Board                                           | 29    |

| Figure 3.3 Controller modules of FPGA                                                  | 30    |

| Figure 3.4 NAND Flash Controller module                                                | 30    |

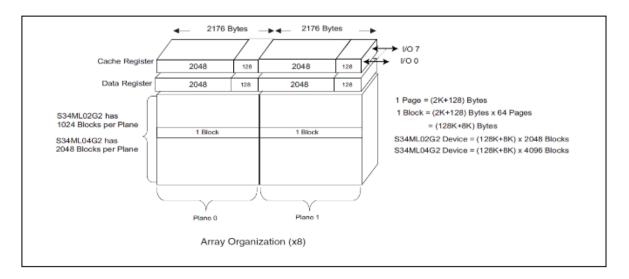

| Figure 4.1A: NAND FLASH Array Organisation                                             | 38    |

| Figure 4.1B: Main area and its division                                                | 39    |

| Figure 4.2 Hardware Systolic Array Type BCH Encoder                                    | 41    |

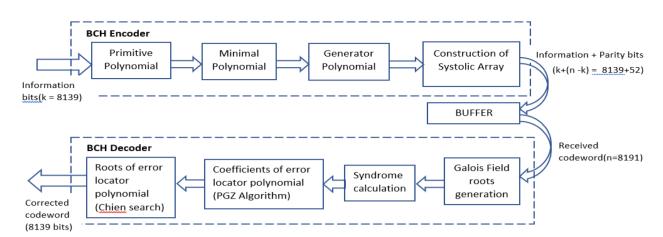

| Figure 4.3 Block Flow Diagram of BCH Encoder-Decoder                                   | 42    |

| Figure 4.5 Conventional Chien search                                                   | 47    |

| Figure 4.6 Flow diagram for proposed BCH Decoder                                       | 48    |

| Figure 5.1 Simulated waveform for BCH(8191,8139,4) Encoder (message = 2.9230e          | +47   |

| (in decimal))                                                                          | 49    |

| Figure 5.2 Serial BCH(63,39,4) Encoder                                                 | 50    |

| Figure 5.3 Parallel BCH(63,39,4) Encoder                                               | 50    |

| Figure 5.4A : Syndrome when no errors in rx                                            | 51    |

| Figure 5.4B : Syndrome when rx has errors                              | 51 |

|------------------------------------------------------------------------|----|

| Figure 5.5A: Coefficients when no errors in rx                         | 51 |

| Figure 5.5B: Coefficients when rx has errors                           | 52 |

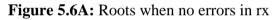

| Figure 5.6A: Roots when no errors in rx                                | 52 |

| Figure 5.6B: Roots when rx has errors                                  | 52 |

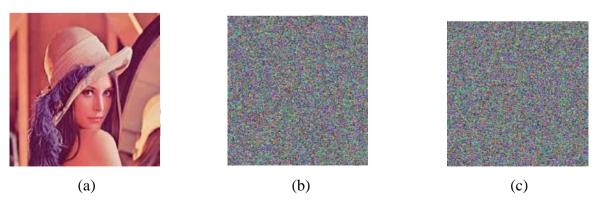

| Figure 6.1 (a) Original Lena image;(b) Image by AES;(c) Image by AES-C | 54 |

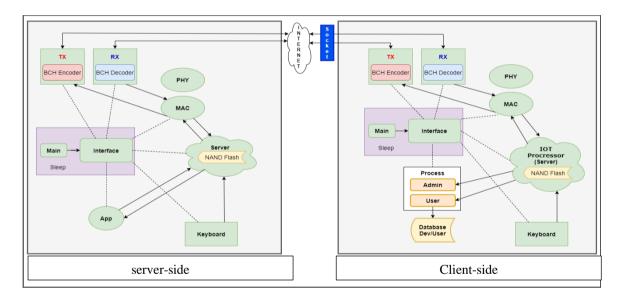

| Figure 6.2 NB-IoT architecture with BCH arrangement                    | 55 |

## LIST OF TABLES

| Table 2.1: (a)Modulo-2 addition(XOR) ;(b) Modulo-2 Multiplication (AND)                                  | 11   |

|----------------------------------------------------------------------------------------------------------|------|

| <b>Table 2.2</b> : (a) Addition for $GF(4) = \{0,1,2,3\}$ ; (b) Multiplication for $GF(4) = \{0,1,2,3\}$ | 12   |

| <b>Table 2.3</b> :(a)Addition for $GF(4) = \{0,1,a,b\}$ ;(b)Multiplication for $GF(4) = \{0,1,a,b\}$     | 12   |

| <b>Table 2.4</b> : BCH codes parameters of lengths less than $2^{10}$ -1                                 | 14   |

| Table 3.1 Operating Environment of Hardware Description Language                                         | 33   |

| Table 3.2 I/O Pin/Device/Package Combinations for Artix-7 FPGAs                                          | 34   |

| Table 3.3 Characteristic Comparison of NAND and NOR                                                      | 36   |

| Table 3.4 Parameteric Comparison of NAND and NOR                                                         | 37   |

| Table 4.1 Recommended BCH Code                                                                           | 39   |

| <b>Table 4.2</b> Root Table for GF $(2^{13})$                                                            | 45   |

| Table 5.1: Performance comparison of parallel and serial BCH encoder observe                             | d in |

| simulation                                                                                               | 50   |

## Chapter 1

# INTRODUCTION

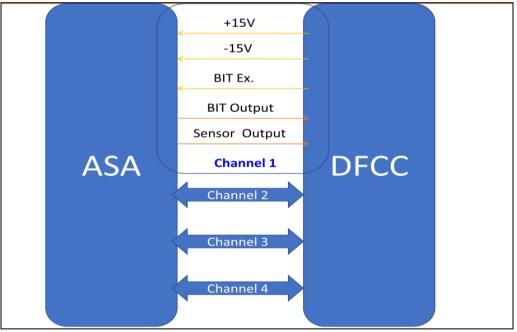

There is need to develop an on-board acquisition unit for interfacing with ASA and assess the in-fight performance of the unit. The in-flight acquisition and recording unit provide excitation voltages to four channels of the ASA unit. ASA operated in two modes namely bit mode and normal mode. During bit mode, ARU provides bit excitation signals to four channels of ASA and need to acquire bit outputs from the ASA unit. In the normal mode of operation, all four channels accelerometer sensor outputs are required to acquire continuously and record them on board. The On-board recorded data need to be downloaded through a high-speed serial interface after the flight on ground for post flight performance analysis of the ASA unit. The unit should provide isolated power to all four channels of ASA. ASA-ARU needs to be compact, lightweight, rugged, low power and airworthy unit to use along with indigenously developed ASA. The ASA-ARU needs to provide a similar interface of DFCC to ASA. The existing interface of ASA with DFCC is given Fig. 1.

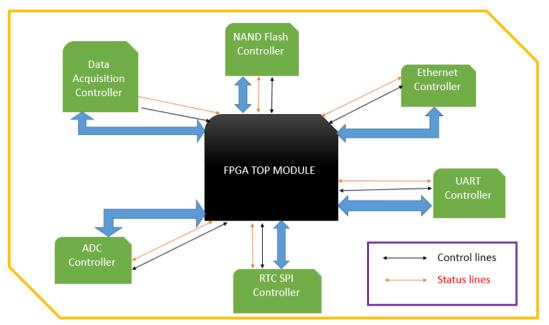

Figure 1. ASA interface with DFCC

The ASA-ARU will have FPGA based main control module for BIT excitation generation, acquisition of BIT output, normal mode sensor output and recording to on-board NAND flash memory. The Ethernet interface is used for downloading of in-flight recorded data.

The RS 232 interface is planned to monitor system health on ground. There will be separate power supply module for the generation of four independent voltages to four channels of ASA.

## 1.1 Requirement of ECC in NAND Flash

Practically, there exists no channel that is noise free and even a single bit error might lead to a major setback for a safety critical system of an aircraft, like flight control systems of a fighter aircraft. Hence, a need for encoding the data along with error correcting and controlling mechanisms for error-free retrieval at the receiver end arises. The interest for a completely dependable computerized framework has been quickened by the accessibility and fast advancement of VLSI innovation, rapid information systems, and capacity of advanced data.[1] Error control coding schemes are linear codes, categorised into Convolution codes and Block codes whose examples are Reed-Solomon, BCH (Bose-Chaudhuri-Hocquenghem) codes, Golay, Cyclic codes, Repetition codes, Polynomial codes, Hamming codes and non-linear codes. The most straightforward block code being Hamming codes, is just appropriate for basic error control circuit while BCH, the generalization of Hamming codes, forms a wide range of effective arbitrary error correcting cyclic codes that is capable of rectifying multiple errors [2].

The ECC mechanism is implemented in two opposing functions. The first is the encoding operation and second is the decoding operation where the former adds spare bits and the latter removes these added bits iteratively [3].

The widely used NAND Flash memory systems are vulnerable to multiple types of errors, such as, retention errors due to charge leakage, physical errors due to coupling noises, errors generated due to shift of threshold voltages as the memory density increases and many more. Thus, the data reliability is of utmost importance for any communication and storage systems in terms of high operational speed and other aspects. Therefore, to improve data reliability we use ECC. With the occurrence of random errors, the first preference would be BCH codes as these are adaptable to wide ranges of code length and possess a versatile error correcting capability over Reed Solomon as the latter is mostly suitable for handling burst errors [4].

## 1.2 Overview of BCH

A conventional BCH design includes an elementary shift register, the LFSR (linear feedback shift register), which in correspondence with explicit XOR, computes single message bit per cycle. Considering the need of circuits with high operational speed, the BCH serial encoder is replaced with the parallel BCH encoders which process p-bit data at an instance. Matrix multiplication, CRT based encoding, unfolding method are some of the parallel processing methods used [5]. In this paper, we employ a BCH encoder with tree-type systolic array architecture. This architecture does without modifying the generator polynomial and extra hardware requirement unlike other three methods mentioned above.

Galois Field (GF) is named after Evariste Galois. The existence of a finite count of elements characterises the GF. Data in vector form in a GF allows mathematical operations to scramble data easily and effectively. Some of the significant properties of GF are:

- All elements of GF are defined on addition and multiplication and the resultant must also be an element of GF.

- Addition (a) and subtraction (b) are inversely related (i.e. a+b=0) and similarly, multiplication(c) and division(d) are inverse to one another (i.e. c\*d=1) [6].

A BCH decoding system is designed for correction of errors in the codeword that might have occurred in the intermediate channel. In the proposed BCH decoder, there are four sub modules, the  $GF(2^{13})$  root table generation, syndrome calculation, computation of coefficients of error locator polynomial (PGZ (Peterson-Gorenstein-Zierler) Algorithm) [7] and determining roots of the error locator polynomial(Chien search) [8].

### 1.3 Motivation

The aerospace systems demand very high level of reliability and safety. Stringent development process is followed for development for aerospace systems to meets these requirements. The design and development exposure in aerospace domain will help in developing systems for all other domains. This has motivated to take up project related fighter aircraft application. In this aerospace domain, the need for compact, rugged, high speed data acquisition and on-board storage is becoming crucial for flight test applications. This in-turn has motivated to take up a Project on "NAND Flash Based In-Flight Acquisition and Recording Unit for Accelerometer Sensor Assembly of Flight Control System"

### 1.4 Objectives

The main objectives of this Project are given bellow:

- 1. General understanding of LCA-FCS, DFCC, ASA and its sensors.

- 2. Understanding of ASA in-flight test requirements and its interface.

- 3. Study of ARU design and development process.

- 4. Study of NAND Flash interface with FPGA.

- 5. Implementation of ECC module using VHDL.

- 6. Functional simulation

- 7. Verification using in-built MATLAB functions

# Chapter 2

# LITERATURE SURVEY

Extensive literature survey helps in understanding the work already carried in the field of investigation and also provides the technology trend in the domain to help to home on to the challenging problem to take up and further investigate as a part of the project.

As a part of literature survey, multiple papers were examined and out of these, few important papers which are in the area of interest were investigated in detail. The outcome of the literature survey is given below:

## 2.1 LCA-FCS, DFCC

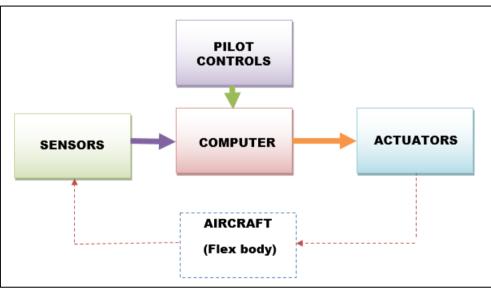

Flight control system of an aircraft consists of Flight control computer, Sensors, Cockpit sensors and actuators as shown in figure 2.1.

Figure. 2.1: Aircraft Flight Control System

LCA flight Control System employees Digital Fly-by-wire flight control system. The heart of the fly-by-wire flight control system is Digital Flight Control Computer (DFCC).

DFCC interfaces with Accelerometer Sensor Assembly, Rate Sensor assembly, Cockpit controls like Pilot Stick, Rudder pedals etc., and Direct Drive Valve (DDV) based Actuators. It contains Flight program with Control Laws.

Fly-by-wire control system, developed in the early 1970's, is purely electrically signaled control system, which use computer to process flight control input by pilot/autopilot and

send corresponding electrical signal to fight control surface actuators. This replaces mechanical linkage, that is, pilot inputs do not directly move to control surface.

Features:

- Provides safety and reliability

- Reduces pilot work load

- Higher Fuel efficiency

- Overall cost reduction

## 2.2 Accelerometer Sensor Assembly (ASA)

An accelerometer is an electromechanical device that will measure acceleration forces. These forces may be static, like the constant force of gravity pulling at your feet, or they could be dynamic which is caused by moving or vibrating the accelerometer.

FCS of TEJAS uses body acceleration for stabilization and command augmentation. The body acceleration is obtained by axes accelerometer sensor assembly.

### BAE's ASA VS Indigenous ASA:

- A single LRU, Line Replacement Unit consist of two accelerometer sensors, that is,

o Lateral axis

o Normal axis

- These sensors are imported from M/s BAE systems, USA.

- Since few components of BAE -ASA are obsolete (production from vendors has stopped),

ASA is out of production as the alternatives are expensive.

- Thereby, ADA initiated indigenous development of MEMS based ASA.

**MEMS** (Micro-electromechanical system) devices that have characteristics of very small size ranges from few micrometres to millimetres combine both mechanical and electrical components fabricated using IC batch processing technologies.

### MEMS-ASA:

### - MEMS-ASA consists of three Axes: o Longitudinal axis

- o Lateral axis

- o Normal axis

- And it is a quadraplex redundant channel. Therefore 12 sensor output data is available.

- Types:

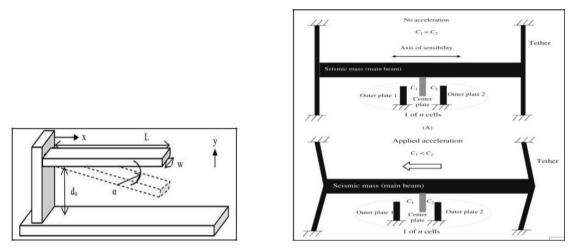

o Cantilever capacitor output

o Proof mass pendulum

Figure.2.2: Cantilever Capacitor Output

- 2.3 Data Integrity:

- Maintaining the data consistent throughout its lifecycle is a matter of protecting it so that it's reliable. Uncorrupted data is considered to be whole and then stay unchanged.

- Data integrity refers to the fact that data must be reliable and accurate over its entire lifecycle. Data integrity(uncorrupted) and data security(protection) go hand in hand.

- Data is expected to be attributable, legible, contemporaneous, original and accurate (ALCOA principle).

## 2.3.1 Data integrity vs. Data security:

Data security refers to the protection of data against unauthorized access or corruption and is necessary to ensure data integrity. Data integrity[9] is a desired result of data security. Data security, in other words, is one of several measures which can be employed to maintain data integrity. Whether it's a case of malicious intent or accidental compromise, data security plays an important role in maintaining data integrity.

## 2.4 Error Control Coding

In recent years there has been an increasing demand for digital transmission and storage systems. This demand has been accelerated by the rapid development and availability of VLSI technology and digital processing. It is frequently the case that a digital system must be fully reliable, as a single error may shutdown the whole system, or cause unacceptable corruption of data, e.g. in a bank account . In situations such as this error control must be employed so that an error may be detected and afterwards corrected. The simplest way of detecting a single error is a parity checksum [10], which can be implemented using only exclusive-or gates. But in some applications this method is insufficient and a more sophisticated error control strategy must be implemented.

If the transmission system transmits data in both directions, an error control strategy may be determined by detecting an error and then, if an error is occurred, retransmitting the corrupted data. These systems are called Automatic Repeat Request (ARQ). If transmission transfers data in only one direction, e.g. in- formation recorded on a compact disk, the only way to control the error is with Forward Error Correction (FEC). In FEC systems some redundant data is concatenated with the information data in order to allow for the detection and correction of the corrupted data without having to retransmit it.

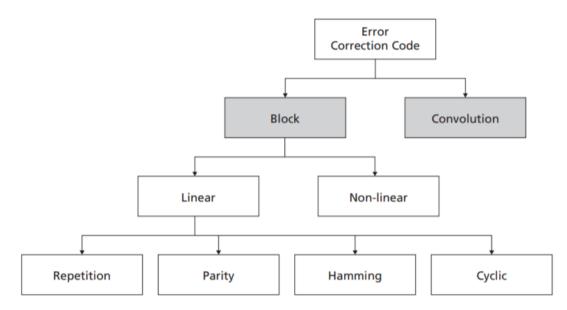

Classification of error control coding schemes[2]:

Figure.2.3: Classification of ECC

The two types of linear codes are,

- Block codes: These codes are referred to as "n" and "k" codes. A block of k data bits is encoded to become a block of n bits called a code word. In block codes, code words do not have any dependency on previously encoded messages. NAND Flash memory devices typically use block codes. Example: RS, Golay, Cyclic codes, Repetition codes, Polynomial codes.

- Convolution codes: These codes produce code words that depend on both the data message and a given number of previously encoded messages. The encoder changes state with every message processed. Typically, the length of the code word constant. Example: Systematic codes, Nonsystematic codes.

### 2.4.1 Linear Block Codes

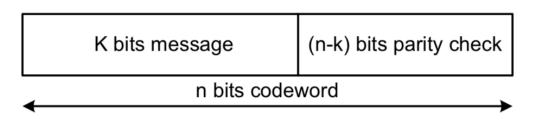

Error control coding mechanism is done in two inverse operations. The first one is a mechanism of adding redundancy bits to the message and form a codeword, this operation called (encoding operation), the second operation is excluding the redundancy bits from the codeword to achieve the message and this operation called (decoding operation).

These types of codes are called block codes and are denoted by C(n,k). The rate of the code, R = k/n, where k represents the message bits and n represents the coded bits. Since the 2kmessages are converted into codewords of n bits. This encoding procedure can be understood as conversion from message vector of k bits located in space of size 2k to a coded vector of size n bits in a space of size, and 2konly selected to be valid codewords.

Linear block codes [2] are considered to be the most common codes used in channel coding techniques. In this technique, message words are arranged as blocks of k bits, constituting a set of 2k possible messages. The encoder takes each block of k bits, and converts it into a longer block of n > k bits, called the coded bits or the bits of the codeword. In this procedure there are (n-k) bits that the encoder adds to the message word, which are usually called redundant bits or parity check bits. As explained in the previous section. The codewords generated from the encoder is linearly combined as the summation of any two codeword is an existing codeword so it is called Linear Block Codes.

Figure. 2.4 Systematic form of codeword of a linear block code

Linear block codes are summarized by their symbol alphabets (e.g., binary or ternary) and parameters  $(n,m,d_{min})$  where

- n is the length of the codeword, in symbols,

- o m is the number of source symbols that will be used for encoding at once,

- $\circ$  *d<sub>min</sub>* is the minimum hamming distance for the code.

There are many types of linear block codes, such as

- 1. Cyclic codes (e.g., Hamming codes)

- 2. Repetition codes

- 3. Parity codes

- 4. Polynomial codes (e.g., BCH codes)

- 5. Reed–Solomon codes

- 6. Algebraic geometric codes

- 7. Reed–Muller codes

- 8. Perfect codes

### 2.5 Galois Field (GF):

In this chapter finite fields[6] and finite field arithmetic operators are introduced. The definitions and main results underlying finite field theory are presented and it is shown how to derive extension fields. The various finite field arithmetic operators are reviewed. In addition, new circuits are presented carrying out frequently used arithmetic operations in decoders. These operators are shown to have faster operating speeds and lower hardware requirements than their equivalents and consequently have been used extensively throughout this project.

## 2.5.1 Properties of Galois Field

The main properties of a Galois field are:

- A finite field always contains a finite number of elements and it must be a prime power, say q = pr, where p is prime and it is unique. In Galois field GF (q), the elements can take q different values. Field is another algebraic system.

- 2. All elements of GF are defined on two operations, called addition and multiplication.

- 3. The result of adding or multiplying two elements from the Galois field must be an element in the Galois field.

- 4. Identity of addition "zero" must be exist, such that a + 0 = a for any element a in the field.

- 5. Identity of multiplication "one" must be exist, such that a \* 1 = a for any element a in the field.

- For every element a in the Galois field, there is an inverse of addition element b such that a + b = 0. This allows the operation of subtraction to be defined as addition of the inverse.

- For every non-zero element b in the Galois field, there is an inverse of multiplication element b-1 such that bb-1= 1. this allows the operation of division to be defined as multiplication by the inverse.

- 8. Both addition and multiplication operations should satisfy the commutative, associative, and distributive laws.

- 2.5.2 Galois field GF(2) "Binary Field"

The simplest Galois field is GF (2). Its elements are the set  $\{0, 1\}$  under modulo-2 algebra. The addition and multiplication tables of GF (2) are shown in Tables 2.1(a) and 2.1(b).

Table 2.1: (a)Modulo-2 addition(XOR) ;(b) Modulo-2 Multiplication (AND)

Here is a one-to-one correspondence between any binary number and a poly- nomial with binary coefficients as every binary number can be presented as a polynomial over GF(2). A polynomial of degree K over GF(2) has the following general form:

$$f(x) = f_0 + f_1 X + f_2 X^2 + \dots + f_K X^K$$

where the coefficient  $f_{0,...}f_k$  are the elements of GF(2) i.e. it can take only values 0 or 1. A binary number of (K + 1) bits can be represented as a polynomial of degree K by taking the coefficients equal to the bits and the exponents of X equal to bit locations. In the polynomial representation, a multiplication by X represents a shift to the right.

### 2.5.3 Extension Fields

Finite fields exist for all prime numbers q and for all  $p^m$  where p is prime and m is a positive integer. GF(q) is a sub-field of GF( $p^m$ ) and as such the elements of GF(q) are a sub-set of the elements of GF( $p^m$ ), therefore GF( $p^m$ ) is an extension field of GF(q).

| <b>Table 2.2</b> : (a) Addition for $GF(4) = \{0,1,2,3\}$ ; (b) Multiplication for $GF(4) = \{0,1,2,3\}$ ; (c) Multiplica | ),1,2,3} |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| + | 0                                                                                                                                       | 1 | 2 | 3 | * | 0 | 1 | 2  | 3                |   |

|---|-----------------------------------------------------------------------------------------------------------------------------------------|---|---|---|---|---|---|----|------------------|---|

| 0 | 0                                                                                                                                       | 1 | 2 | 3 |   | 0 | 0 | 0  | 0                | 0 |

| 1 | 1                                                                                                                                       | 2 | 3 | 0 |   | 1 | 0 | 1  | 2                | 3 |

| 2 | 2                                                                                                                                       | 3 | 0 | 1 |   | 2 | 0 | 2  | 0                | 2 |

| 3 | 3                                                                                                                                       | 0 | 1 | 2 |   | З | 0 | 3  | 0<br>2<br>0<br>2 | 1 |

|   |                                                                                                                                         |   |   |   |   | · |   |    |                  |   |

|   | 0     1     2     3       0     0     1     2     3       1     2     3     0       2     2     3     0     1       3     0     1     2 |   |   |   |   |   | ( | b) |                  |   |

Consider GF (4)= $\{0,1,2,3\}$  in Table 2.2(a) and 2.2(b), which is not a Galois field because it is of order 4, which is not a prime. The element 2 has no multiplicative inverse and therefore we cannot divide by 2. Instead, we could define GF (4)= $\{0,1, a, b\}$  with addition and multiplication as shown in Table 2.3(a)and 2.3(b).

Now all elements do have additive and multiplicative inverses.

**Table 2.3**: (a)Addition for  $GF(4) = \{0,1,a,b\}$ ; (b)Multiplication for  $GF(4) = \{0,1,a,b\}$

| + | 0                                                      | 1 | а | b |  | * | 0 | 1  | а | b |

|---|--------------------------------------------------------|---|---|---|--|---|---|----|---|---|

| 0 | 0                                                      | 1 | а | b |  | 0 | 0 | 0  | 0 | 0 |

| 1 | 1                                                      | 0 | b | а |  | 1 | 0 | 1  | а | b |

| а | а                                                      | b | 0 | 1 |  | а | 0 | а  | b | 1 |

| b | b                                                      | а | 1 | 0 |  | b | 0 | b  | 1 | а |

|   | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |   |   |   |  |   |   | (b |   |   |

These extension fields are used to handle non-binary codes where code symbols are expressed as m -bit binary code symbols, For example, GF(4) consists of four different two-bit symbols and GF(16) of 16 hexadecimal symbols. To obtain multiplication for binary, numbers are expressed as polynomials, they are multiplied and divided by the prime polynomial while the remainders taken as result.

## 2.6 BCH Codes

BCH codes forms a class of random multiple error-correcting cyclic codes. defined over a Galois Field (GF) of q elements GF(q), with q=2m. The parameter m corresponds to the degree of the GF, q is the number of states that takes each component of the GF elements, and they are related with the codeword length as n=2m-1.

Binary BCH codes are identified by their codeword length n, their message length k, the maximum error capability of the code is t, and are represented as BCH (n, k, t)

For any positive integer  $m \ge 3$  (where  $3 \le m \le 16$ ) and t < 2m - 1, there exists a binary BCH code with the following parameters:

Block length: n = 2m - 1

Number of parity-check digits: n - k - mt

Minimum distance: dmin = 2t + 1.

BCH codes are subset of the Block codes. In block codes, the redundancy bits are added to the original message bits and the resultant longer information bits called "codeword" for error correction is transmitted. The block codes are implemented as (n, k) codes where n indicates the codeword and k the original information bits.

2.6.1 BCH Merits:

- It can be decoded using syndrome decoding method

- Highly flexible allowing control over block length and acceptable error thresholds

- Reed Solomon codes are nonlinear BCH codes used in applications such as satellite communication, compact disk players, DVD's, disk drives, 2-dimensional bar code

- Low amount of redundancy

- Easy to implement in hardware

- Widely used

The parameters of some useful BCH codes of lengths less than  $2^{10}$ -1 are given below:

| m     | n     | k   | t  | m   | n   | k             | t    | m  | n   | k   | t    | n   | k   | t                | n    | k                | t                   |          |

|-------|-------|-----|----|-----|-----|---------------|------|----|-----|-----|------|-----|-----|------------------|------|------------------|---------------------|----------|

| 3     | 7     | 4   | 1  |     | 63  | 24            | 7    |    | 127 | 50  | 13   | 255 | 187 | 9                | 255  | 71               | 29                  | <b>)</b> |

| 4     | 15    | 11  | 1  |     |     | 18            | 10   |    |     | 43  | 14   |     | 179 | 10               |      | 63               | 30                  | )        |

|       |       | 7   | 2  |     |     | 16            | 11   |    |     | 36  | 15   |     | 171 | 11               |      | 55               | 3                   | 1        |

|       |       | 5   | 3  |     |     | <del>10</del> | -13- |    |     | 29  | 21   |     | 163 | 12               |      | 47               | 42                  | 2        |

| 5     | 31    | 26  | 1  |     |     | 7             | 15   |    |     | 22  | 23   |     | 155 | 13               |      | 45               | 43                  | 3        |

|       |       | 21  | 2  | 7   | 127 | 120           | 1    |    |     | 15  | 27   |     | 147 | 14               |      | 37               | 43                  | 5        |

|       |       | 16  | 3  |     |     | 113           | 2    |    |     | 8   | 31   |     | 139 | 15               |      | 29               | 47                  | 7        |

|       |       | 11  | 5  |     |     | 106           | 3    | 8  | 255 | 247 | 1    |     | 131 | 18               |      | 21               | 55                  | 5        |

|       |       | 6   | 7  |     |     | 99            | 4    |    |     | 239 | 2    |     | 123 | 19               |      | 13               | 59                  | 9        |

| 6     | 63    | 57  | 1  |     |     | 92            | 5    |    |     | 231 | 3    |     | 115 | 21               |      | 9                | 63                  | 3        |

|       |       | -51 | 2  |     |     | 85            | 6    |    |     | 223 | 4    |     | 107 | 22               | 511  | 502              | ]                   | 1        |

|       |       | 45  | 3  |     |     | 78            | 7    |    |     | 215 | 5    |     | 99  | 23               |      | 493              | 2                   | 2        |

| For t | small | 39  | 4  |     |     | 71            | 9    |    |     | 207 | 6    |     | 91  | 25               |      | 484              | 2                   | 3        |

| 1 – k |       | 36  | 5  |     |     | 64            | 10   |    |     | 199 | 7    |     | 87  | 26               |      | 475              | 4                   | 4        |

|       |       | 30  | 6  |     |     | 57            | 11   |    |     | 191 | 8    |     | 79  | 27               |      | 466              | 4                   | 5        |

|       |       |     |    |     |     |               |      |    |     |     |      |     |     |                  |      |                  |                     |          |

| n     | k     | 1   | t  | n   | k   | t             | n    |    | k   | t   | n    |     | k   | t                | n    | k                | (                   |          |

| 511   | 457   |     | 6  | 511 | 322 | 22            | 51   | 11 | 193 | 43  | 511  | 1   | 58  | 91               | 1023 | 3 93             | 33                  |          |

|       | 448   |     | 7  |     | 313 | 23            |      |    | 184 | 45  |      |     | 49  | 93               |      | 92               | 23                  |          |

|       | 439   |     | 8  |     | 304 | 25            |      |    | 175 | 46  |      |     | 40  | <mark>9</mark> 5 |      | 91               | 13                  |          |

|       | 430   |     | 9  |     | 295 | 26            |      |    | 166 | 47  |      |     | 31  | 109              | 903  |                  |                     |          |

|       | 421   |     | 10 |     | 286 | 27            |      |    | 157 | 51  |      |     | 28  | 111              | 89   |                  |                     |          |

|       | 412   |     | 11 |     | 277 | 28            |      |    | 148 | 53  |      |     | 19  | 119              |      |                  | <mark>8</mark> 83 1 |          |

|       | 403   |     | 12 |     | 268 | 29            |      |    | 139 | 54  |      |     | 10  | 121              |      | 873 <sup>-</sup> |                     |          |

|       | 394   |     | 13 |     | 259 | 30            |      |    | 130 | 55  | 1000 |     | 013 | 1                |      | 86               |                     |          |

|       | 385   |     | 14 |     | 250 | 31            |      |    | 121 | 58  | 1023 |     | 003 | 2                |      | 85               | 80                  |          |

|       | 376   |     | 15 |     | 241 | 36            |      |    | 112 | 59  |      |     | 993 | 3                |      |                  |                     |          |

|       | 367   |     | 16 |     | 238 | 37            |      |    | 103 | 61  |      | ç   | 983 | 4                |      |                  |                     |          |

### 2.6.2 BCH Demerits:

- Complexity.

- Iterative complex decoding algorithm.

• Decoder cannot decide whether decoded package is false or not.

### 2.6.3 Some examples of BCH Applications:

- (511,493) BCH code is used in ITU-T Rec.H.261video codec for video conferencing and video phone

- (40,32) BCH is used in ATM (Asynchronous Transfer Mode) it is a shorten cyclic code that can correct 1-bit or 2-bit error

- ECC in NAND Flash memory for reliable data storage

## 2.7 BCH Encoder

An encoder is a device, circuit, transducer, software program, or algorithm that converts the information from one format or code to another, for the purposes of standardisation, speed or compressions. A simple encoder assigns binary code to an active input line. The BCH encoder block creates a BCH code with message length k and codeword length n. The input must contain exactly k elements. n must have the form  $2^{m}$ -1 where m is an integer greater than or equal to 3.

## 2.7.1 Code generation:

To generate all the field elements a primitive polynomial in Galois Field :

In order to obtain the generator polynomial[6] of the BCH code we need and auxiliary polynomial called primitive polynomial. The generator polynomial is the polynomial of lowest degree over GF(2) with  $\alpha^2$ ,  $\alpha^3$ ,...,  $\alpha^{2t}$  as roots. Let mi(x) be the minimal polynomial of  $\alpha^i$ . Then, must be the *least common multiple (LCM)* of  $m(x)_1, m_2(x), ..., m_{2t}(x)$ . That is

$g(x) = LCM\{m_1(x), m_2(x), \dots, m_{2t}(x)\}$

A simplification is possible because every even power of a primitive element has the same minimal polynomial as some odd power of the element, halving the number of factors in the polynomial. Then

$$g(x) = LCM\{m_1(x), m_3(x), \dots, m_{2t-1}(x)\}$$

Hence, every even power of  $\alpha$  in the sequence has the same minimal polynomial as some preceding odd power of  $\alpha$  in the sequence. As a result, the generator polynomial g(x) of the binary *t-error-correcting* BCH code of length 2<sup>m</sup>-1 can be reduced to

$$g(x) = LCM\{\phi_1(x), \phi_3(x), \dots, \phi_{2t-1}(x)\}$$

The generator polynomial is  $g(x) = 1 + g_1 x + g_2 x^2 + g_3 x^3 + \dots + g_{n-k-1} x^{n-k-1}$

Code word  $c(x) = c_{n-1}x^{n-1} + c_{n-2}x^{n-2} + \ldots + c_1x + c_0$

Data polynomial,  $d(x) = d_{k-1}x^{k-1} + d_{k-2}x^{k-2} + \dots + d_1x + d_0$

$C(x) = d(x) \cdot g(x)$

2.7.2 Primitive Polynomials:

A primitive polynomial is a polynomial that generates all elements of an extension field from a base field. Primitive polynomials are also irreducible polynomials. For any prime or prime power q and any positive integer n, there exists a primitive polynomial of degree n over GF(q).

The primitive polynomial for various value of m is shown in table:

| <b>Table 2.5</b> : Primitive polynomials for $3 \le m \le 20$ |

|---------------------------------------------------------------|

|---------------------------------------------------------------|

| М  | Primitive Polynomial              |

|----|-----------------------------------|

| 3  | $1+x+x^3$                         |

| 4  | $1+x+x^4$                         |

| 5  | $1 + x^2 + x^5$                   |

| 6  | $1+x+x^6$                         |

| 7  | $1 + x^{3+} x^{7}$                |

| 8  | $1 + x^2 + x^3 + x^4 + x^8$       |

| 9  | $1 + x^4 + x^9$                   |

| 10 | $1 + x^3 + x^{10}$                |

| 11 | $1 + x^2 + x^{11}$                |

| 12 | $1 + x + x^4 + x^6 + x^{12}$      |

| 13 | $1 + x + x^3 + x^4 + x^{13}$      |

| 14 | $1 + x + x^6 + x^{10} + x^{14}$   |

| 15 | $1 + x + x^{15}$                  |

| 16 | $1 + x + x^{3} + x^{12} + x^{16}$ |

| 17 | $1 + x^3 + x^{17}$                |

| 18 | $1 + x^7 + x^{18}$                |

| 19 | $1 + x + x^2 + x^5 + x^{19}$      |

| 20 | $1 + x^{3+} x^{20}$               |

There are

$$a_q(n) = \frac{\phi(q^n - 1)}{n}$$

Primitive polynomials over GF(q), where  $\Phi(n)$  is the totient function. A polynomial of degree n over the finite field GF(2) is primitive if it has polynomial order  $2^n - 1$ .

### 2.7.3 Minimal Polynomials:

The even powers minimal polynomials are duplicates of odd powers minimal polynomials, so we only use the first two minimal polynomials corresponding to odd powers of the primitive element.

#### 2.8 BCH Decoder

A BCH decoding system is designed for the correction of errors in the codeword. Some of the popular methods used for decoding are PGZ (Peterson-Gorenstein-Zierler) Algorithm, Berlekamp-Massey (BMA) algorithm and Euclidean (EA) algorithm. There are different Chien search algorithms for fast encoding like the Conventional p-parallel - Chien architecture, MPCN-based parallel architecture , Joint Chien Search & Syndrome-Calculator Architecture.

#### 2.8.1 Algebraic Decoding

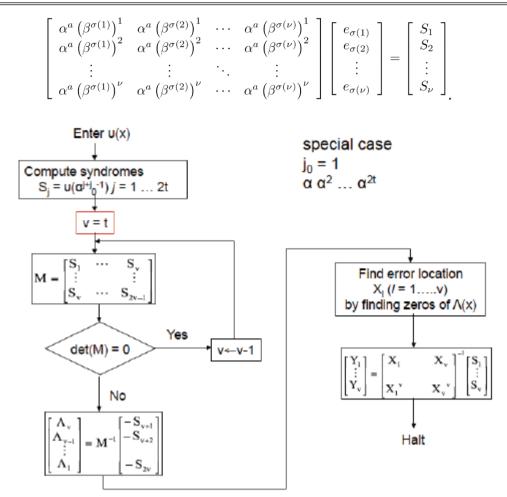

### A. Peterson-Gorenstein-Zierler Decoding

If there are  $\nu$  errors, then the syndrome relationships (3) for j = 1, 2, ..., n - k provide n - k equations involving the  $2\nu$  unknowns  $\sigma(i)$  and  $e_{\sigma(i)}$  for  $i = 1, 2, ..., \nu$ . Since these equations are nonlinear, solving for these unknowns requires a clever trick. For  $\nu \le t \le \lfloor \frac{n-k}{2} \rfloor$ , let  $\Lambda(x) \triangleq \sum_{j=0}^{t} \Lambda_j x^j$  be any degree-*t* polynomial that satisfies  $\Lambda(0) = 1$  and  $\Lambda(\beta^{-\sigma(i)}) = 0$  for  $i = 1, ..., \nu$ . Then, the coefficients of  $\Lambda(x)$  have a linear relationship with the syndromes. This can be seen by summing the equation

$$0 = \Lambda \left( \beta^{-\sigma(i)} \right) = \Lambda_t \left( \beta^{-\sigma(i)} \right)^t + \Lambda_{t-1} \left( \beta^{-\sigma(i)} \right)^{t-1} + \dots + \Lambda_1 \left( \beta^{-\sigma(i)} \right) + \Lambda_0$$

for  $i = 1,...,\nu$  with the coefficients  $e_{\sigma(i)}\alpha^a \left(\beta^{\sigma(i)}\right)^k$ . For k = t + 1, t + 2,...,2t, this gives

NAND Flash Based In-Flight Acquisition and Recording Unit for Accelerometer Sensor Assembly of Flight Control System

$$0 = \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^{a} \left(\beta^{\sigma(i)}\right)^{k} \Lambda \left(\beta^{-\sigma(i)}\right)$$

$$= \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^{a} \left(\beta^{\sigma(i)}\right)^{k} \sum_{j=0}^{t} \Lambda_{j} \left(\beta^{-\sigma(i)}\right)^{j}$$

$$= \sum_{j=0}^{t} \Lambda_{j} \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^{a} \left(\beta^{\sigma(i)}\right)^{k-j}$$

$$= \sum_{j=0}^{t} \Lambda_{j} S_{k-j}.$$

(1)

The derivation implies that any polynomial  $\Lambda(x)$  with constant term 1 and roots at  $\beta^{-\sigma(i)}$  (i.e., the inverse of  $\alpha$  to the error location) for  $i = 1,...\nu$  must satisfy this equation. The minimal-degree polynomial  $\Lambda(x)$  that satisfies these conditions is called the *error-locator polynomial*. It is easy to see that it must have one root at each location and is, therefore, the degree- $\nu$  polynomial defined by

$$\Lambda(x) \triangleq \prod_{i=1}^{\nu} \left( 1 - x \beta^{\sigma(i)} \right)$$

This polynomial allows the error position to be revealed by factoring  $\Lambda(x)$ .

Since  $\Lambda_0 = 1$ , (1) defines the linear system

$$\begin{bmatrix} S_1 & S_2 & \cdots & S_t \\ S_2 & S_3 & \cdots & S_{t+1} \\ \vdots & \vdots & \ddots & \vdots \\ S_t & S_{t+1} & \cdots & S_{2t-1} \end{bmatrix} \begin{bmatrix} \Lambda_t \\ \Lambda_{t-1} \\ \vdots \\ \Lambda_1 \end{bmatrix} = \begin{bmatrix} -S_{t+1} \\ -S_{t+2} \\ \vdots \\ -S_{2t} \end{bmatrix}$$

(2)

where the *i*-th row is given by the equation for k = t + i. If t = v, then this matrix will be invertible because there is a unique solution. If it is not invertible, one can sequentially reduce t by 1 until the matrix becomes invertible. After solving for the error-locator polynomial, one can evaluate it at all points  $\ln \mathbb{F}_q^*$  to determine the error locations. An efficient method of doing this is called a *Chien search*.

For binary BCH codes, the error magnitudes must be 1. After correcting the "errors", one must also check that the resulting vector is a codeword by reducing it modulo g(x). If it is not a codeword, then the decoder should declare a detected error. For non-binary codes, one can solve for the error magnitudes using the error locations and the implied frequency-domain parity-check matrix[7]. For fixed error locations, one can write the first v syndromes as linear functions of the error magnitudes using

NAND Flash Based In-Flight Acquisition and Recording Unit for Accelerometer Sensor Assembly of Flight Control System

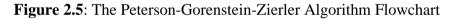

#### B. The Berlekamp-Massey Decoding Algorithm

While the PGZ algorithm is conceptually simple, it can require the inversion of an  $i \times i$  matrix for i = 1, 2, ..., t in the worst case. Since each inversion has a complexity of roughly  $i^3/2$  operations, this approach leads to a worst case complexity of roughly  $t^4/6$  operations. The Berlekamp-Massey algorithm [11] starts with the observation that (1) can be rewritten, for j = t + 1, t + 2, ..., n - k, as

$$S_j = -\sum_{i=1}^t \Lambda_i S_{j-i}.$$

This implies that the syndrome sequence  $S_1, S_2,...$  can be generated by a linear feedback shift register (LFSR) with coefficients  $\Lambda_1, \Lambda_2,...,\Lambda_t$ . The shortest LFSR that generates the syndrome sequence is unique and corresponds to t = v and gives the error-locator polynomial. The trick is to solve recursively for a sequence of LFSRs that generate the initial part of the syndrome sequence. Let the connection polynomial of a length- $L_k$  minimal length LFSR that generates the first *k* elements of the syndrome be

$$\Lambda^{[k]}(x) = \sum_{i=0}^{L_k} \Lambda_i^{[k]} x^i.$$

To be precise, we say that  $\Lambda^{[k]}(x)$  generates the first *k* elements if

$$S_j = -\sum_{i=1}^{L_k} \Lambda_i^{[k]} S_{j-i},$$

for  $j = L_k + 1,...,k$ . In particular, the shift register is initialized to contain the first  $L_k$  elements,  $S_1, S_2,..., S_{L_k}$ . Then, the *j*-th clock outputs  $S_j$  and computes  $S_{j+L_k}$  from  $S_1, S_2,..., S_{L_k}$ . This also introduces a subtle distinction between  $L_k$  and the degree of  $\Lambda^{[k]}(x)$ .

Figure 2.6: BMA Algorithm with flowchart

#### C. Sugiyama's Euclidean Decoding Algorithm

An alternative approach is to use the Euclidean algorithm[12] to find the error-locator polynomial. To describe this, the syndrome is first extended to a semi-infinite sequence  $(S_1, S_2,...)$  by defining

$$S_j = \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^a \left(\beta^{\sigma(i)}\right)^j, \tag{3}$$

for  $j \in \{1, 2, ...\}$  and noting that the two definitions coincide for j = 1, 2, ..., n - k. The *extended* syndrome function  $\widetilde{S}(x)$  is defined to be

$$\widetilde{S}(x) \triangleq \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^{a} \frac{\beta^{\sigma(i)}}{1 - x\beta^{\sigma(i)}}$$

$$= \sum_{j=1}^{\infty} \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^{a} x^{j-1} \left(\beta^{\sigma(i)}\right)^{j}$$

$$= \sum_{j=1}^{\infty} S_{j} x^{j-1}.$$

It is important here to comment on the meaning of infinite sums over finite fields. Unlike the continuous case, no two distinct points can be considered close to one another. Therefore, convergence in the limit is the same as eventual equality. Thus, the second and third equalities do not hold for evaluations but instead imply that the (infinite) power series expansions of the two expressions match term by term.

The error-evaluator polynomial

$$\Omega(x) \triangleq \sum_{j=0}^{\nu} \Omega_j x^j$$

is given by

$\Omega(x) \triangleq \Lambda(x) \widetilde{S}(x)$

$= \prod_{j=1}^{\nu} \left(1 - x\beta^{\sigma(j)}\right) \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^a \frac{\beta^{\sigma(i)}}{1 - x\beta^{\sigma(i)}}$

$= \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^a \beta^{\sigma(i)} \prod_{j \neq i}^{\nu} \left(1 - x\beta^{\sigma(j)}\right).$

It is easy to see that  $\Omega(x)$  has degree at most v - 1. The polynomial  $\Omega(x)$  is called the errorevaluator polynomial because

$$\begin{split} \Omega\left(\beta^{-\sigma(k)}\right) &= \sum_{i=1}^{\nu} e_{\sigma(i)} \alpha^{a} \beta^{\sigma(i)} \prod_{j \neq i}^{\nu} \left(1 - \beta^{-\sigma(k)} \beta^{\sigma(j)}\right) \\ &= e_{\sigma(k)} \alpha^{a} \left[\beta^{\sigma(k)} \prod_{j \neq k}^{\nu} \left(1 - x \beta^{\sigma(j)}\right)\right]_{x = \beta^{-\sigma(k)}} \\ &= -e_{\sigma(k)} \alpha^{a} \Lambda'\left(\beta^{-\sigma(k)}\right), \end{split}$$

where, using the product rule, the formal derivative of  $\Lambda(x)$  is given by

$$\Lambda'(x) = -\sum_{i=1}^{\nu} \beta^{\sigma(i)} \prod_{j \neq i}^{\nu} \left( 1 - x \beta^{\sigma(j)} \right).$$

Using  $\Omega(x)$ , one can compute the error magnitudes using

$$e_{\sigma(k)} = -\frac{\Omega\left(\beta^{-\sigma(k)}\right)}{\alpha^a \Lambda'\left(\beta^{-\sigma(k)}\right)}.$$

(4)

This approach is known as Forney's method.

The decoder is required to compute both the error-locator and error-evaluator polynomials from the finite syndrome polynomial  $S(x) \triangleq \sum_{j=1}^{2t} S_j x^{j-1}$ . Since  $S_e(x) = S(x) + x^{2t} w(x)$ , for some w(x), we find that

$$\Omega(x) = \Lambda(x)S_{e}(x) = \Lambda(x)S(x) + \Lambda(x)x^{2t}w(x)$$

and deg( $\Omega(x)$ ) <  $\nu$ . Thus, we arrive at the key equation for RS decoding which is given by

$$\Omega(x) \equiv \Lambda(x)S(x) \bmod x^{2t}.$$

In fact, if  $v \le t$ , then any degree-v polynomial  $\Theta(x)$  that satisfies deg  $\Theta(x)S(x) \mod x^{2t}$  < v must also satisfy  $\Theta(x) = c\Lambda(x)$  [4, Prop. 6.1]. Therefore, this equation can also be used to find error-locator and error-evaluator polynomials.

The extended Euclidean algorithm (EEA) computes the greatest common divisor of two elements  $a_1, a_2$  from a Euclidean domain E (e.g., a ring of polynomials over a field) and coefficients  $u, v \in E$  such that  $a_0u + a_1v = \gcd(a_1, a_2)$ . The algorithm proceeds by dividing  $a_j$ by  $a_{j+1}$  so that  $a_j = a_{j+1}q_{j+1} + a_{j+2}$  with quotient  $q_{j+1}$  and remainder  $a_{j+2}$ . Each step of the Euclidean algorithm works because the division implies that  $\gcd(a_j, a_{j+1}) = \gcd(a_{j+1}, a_{j+2})$ . For polynomials, the Euclidean algorithm terminates when  $a_j = 0$ . This always occurs because  $\deg(a_2) < \deg(a_1)$  holds by assumption and  $\deg(a_{j+2}) < \deg(a_{j+1})$  holds by induction.

The extended algorithm also computes  $u_j, v_j$  recursively so that  $a_j = u_j a_1 + v_j a_2$ . Starting from  $a_3 = a_1 - q_2 a_2$  (i.e.,  $u_3 = 1$  and  $v_3 = -q_2$ ), we have the recursion

$$aj+2 = aj - qj+1aj+1 = (uja1 + vja2) - qj+1 (uj+1a1 + vj+1a2).$$

This gives the recursions  $u_{j+2} = u_j - q_{j+1}u_{j+1}$  and  $v_{j+2} = v_j - q_{j+1}v_{j+1}$  starting from  $u_3 = 1$  and  $v_3 = -q_2$ .

The decoding the RS codes is accomplished using a partial application of the EEA algorithm to compute  $gcd(x^{2t}, S(x))$ . The extended part of the algorithm generates a sequence of relationships of the form  $u_j(x)x^{2t} + v_j(x)S(x) = a_j(x)$ ,

where the degree of  $a_j(x)$  is decreasing with j. Let  $j^*$  be the first step where  $deg(a_j(x)) < t$ and stop the algorithm at this point. Viewing the above relationship as a congruence modulo  $x^{2t}$  gives  $v_j(x)S(x) \equiv a_j(x) \mod x^{2t}$ , and we see that  $v_j*(x)$  and  $a_j*(x)$  satisfy the key equation with  $deg(a_j*(x)) < t$ . In this case, the polynomials  $v_j*(x), a_j*(x)$  must also satisfy

$$v_j(x) = c\Lambda(x)$$

$a_j(x) = c\Omega(x),$

for some constant *c*. This means that we can run the EEA until the remainder term has degree less than *t*. After that, we can solve for *c* using  $c = v_j(0)$  and compute  $\Lambda(x), \Omega(x)$ . After the error-locator and error-evaluator polynomials are known, decoding proceeds by factoring  $\Lambda(x)$  to find the error locations and then using (4) to compute the error magnitudes.

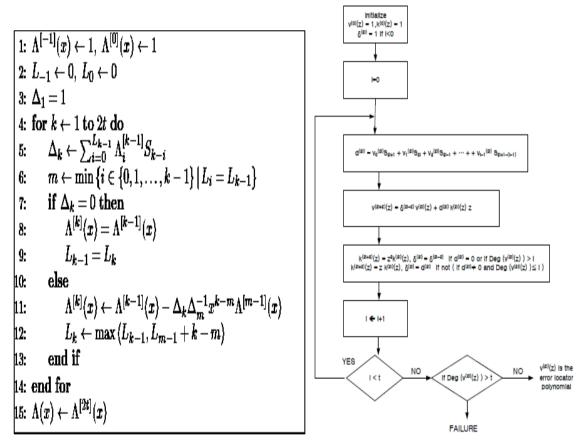

#### 2.8.2 Chien Search Algorithms

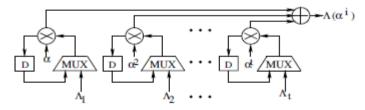

Once  $\Lambda(x)$  is found, the decoder searches for error locations by checking whether  $\Lambda(\alpha i) = 0$  for  $0 \le i \le (n - 1)$ , which is normally achieved by Chien search. A conventional serial Chien search architecture is shown in Fig. 2.7(a), and

$$\Lambda(\alpha^i) = \sum_{j=0}^t \Lambda_j \alpha^{ij} = \sum_{j=1}^t \Lambda_j \alpha^{ij} + 1$$

where  $0 \le i \le (n - 1)$ . All the multiplexers select  $\Lambda(x)$  in the first clock cycle, then select the registered data afterwards.

Figure 2.7(a) : Conventional Chien search circuit

Since all the n possible locations have to be evaluated for the  $\Lambda(x)$ , it takes n clock cycles to complete the Chien search process. To speed up this process, parallel Chien search architecture that evaluates several locations per clock cycle is essential. Two different

NAND Flash Based In-Flight Acquisition and Recording Unit for Accelerometer Sensor Assembly of Flight Control System

possible architectures [13] with parallel factor p are depicted in Fig. 2.7(b) and Fig. 2.7(c) , where Fig. 2.7(b) actually is just a direct unfolded version of Fig. 2.7(a) with an unfolding factor of p.

As both designs can reduce the number of clock cycles searching for error locations from n down to [n/p], they also share similar hardware complexity. Denoting the parallel factor as p, both designs have the exactly same (p × t) constant finite field multipliers (FFM), p t-input m-bit finite field adders(FFA),p m-bit registers and p m-bit multiplexers. However, the critical path of Fig. 2.6(b) is (Tmux+ p ×Tm+ Ta) while it is only (Tmux+Tm+Ta) for Fig. 2.7(c), where Tmux,Tm and Ta stand for the critical path of multiplexer, FFM and t-input m-bit FFA, respectively. Obviously, once the parallel factor p is greater than 1, much faster clock speed could be achieved for the design in Fig. 2.7(c) is p times shorter.

Figure 2.7(b) : p-parallel Chien search architecture: direct unfolded version

**Figure 2.7(c)** : p-parallel Chien search architecture: equivalent architecture with shorter critical path

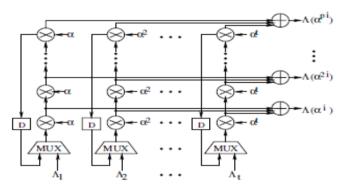

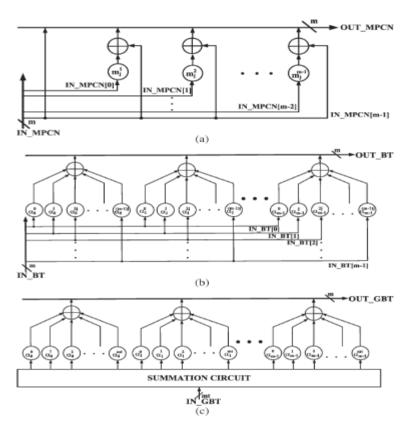

Fig. 2.8 shows the architectures of three basis components, including the *j*th MPCN, the *j*th BT, and the GBT. The *j*th MPCN MPCN*j* shown in Fig. 2.8(a) executes modulo operation with divisor Mj(x). It is constructed by the combinational circuit of the linear feedback shift

register with the connectionm polynomial Mj(x). Each binary element mkj in Fig. 2.8(a) is the *k*th coefficient of Mj(x), indicating the wire connection. In the *j*th BT shown in Fig. 2.8(b), each  $\alpha k l$  is a binary element and can be represented whether the wire is connected or not. Fig. 2.8(c) illustrates the block diagram of the GBT. The additions are first executed with all the coefficients of Dj(x) for  $j = 1 \sim t$  (total *mt* bits), and the similar operations as a BT are applied with basis  $\alpha 0 \sim \alpha mt$ .

Figure 2.8 Basic components in Chien search architecture. (a) MPCN<sub>j</sub>. (b) BT<sub>j</sub>. (c) GBT.

In the MPCN-based parallel-*p* Chien search architecture shown in Fig. 2.9, the coefficients of  $\Lambda(x)$  are applied to the IBTs for transforming the operating basis. The transformed values are evaluated with minimal polynomials for obtaining the Chien search results. All the multiplexers select the outputs of IBTs in the first cycle and then select the register data afterward. Searching from the (N - 1)th to zeroth location, the proposed design checks *p* locations at each cycle. In each row, *mt*-bit data are fed into a GBT to examine the error locations. An error is found at the  $(N + r - p(\tau + 1) - 1)$ th location if the output of the *r*th-row GBT is equal to zero at the  $\tau$  th cycle. MPCN Chien search architecture utilizes  $p \times t$  MPCNs to replace  $p \times t$  CFFMs. Notice that the XOR gate count requirement of one MPCN

is at most m - 1, which is much smaller than that of one CFFM. Therefore, it is area efficient to apply the MPCNs, particularly in the large parallelism conditions.

Figure 2.9 MPCN-based parallel-p Chien search architecture.

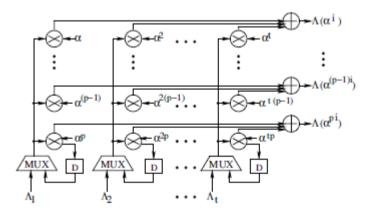

The MPCN-based architecture can merge the syndrome calculator and the Chien search in the same hardware with small overhead. Fig. 2.10 illustrates parallel-p joint syndrome calculator and Chien search with the MPCN-based architecture. The syndrome calculator and Chien search phases are determined by the SEL signal. When the SEL signal is high, the jth syndrome value is formulated as

$$S_{j} = \left( \left( (R_{N-1}x^{p-1} + \dots + R_{N-p-1}) \mod M_{j}(x) \right) x^{p} + (R_{N-p-2}x^{p-1} + \dots + R_{N-2p-1}) \right) \mod M_{j}(x) x^{p} + \dots x^{p} + R_{p-1}x^{p-1} + \dots + R_{0} \mod M_{j}(x) |_{x=\alpha j}$$

The partial remainder stored in the register is multiplied by  $x^p$  and accumulated with the received symbols. After all the received symbols are processed, BTj transforms the accumulated result to the jth syndrome value. In contrast with Fig. 2.9, t BTs are applied instead of one GBT in the first row to evaluate individual syndrome value. Note that the FFA in Fig. 2.10 is only a 1-bit operation because each coefficient of R(x) is a binary value. Therefore, except for the difference between the BT and the GBT, the overhead of the supporting syndrome calculation is only p NAND and p  $\times$  t XOR gates.

NAND Flash Based In-Flight Acquisition and Recording Unit for Accelerometer Sensor Assembly of Flight Control System

**Figure 2.10** Parallel-*p* joint syndrome calculator and Chien search with MPCN based architecture.

# Chapter 3

# HARDWARE

# 3.1 Acquisition and Recording Unit (ARU)

Figure 3.1 ASA-ARU system interface with ASA-LRU

The main objective of ASA-ARU is used to store the 12 Accelerometer Sensors data. The data is stored in the digital but the sensors outputs are analog. So, to convert analog to digital ADC's are required. ASA has 12 sensor outputs. Hence, two ADC's are used. NAND FLASH is used to store the acquired data. RTC with on-board memory is used for time-stamp and storing data. To retrieve the data from the NAND FLASH Ethernet is used. RS232 is used to retrieve the data from the RTC. ASA-ARU uses ADC, NAND FLASH, RTC, Ethernet physical layer and RS232 transceiver.

The ASA-ARU will acquire and record the 12-accelerometer sensors data of ASA continuously. The recorded data can be later retrieved for analysis purpose at ground. The ASA-ARU contains RS-232 interface, which shall be used to debug the system and Ethernet interface for data retrieval.

The objective of the ASA-ARU is used to store the 12 Accelerometer Sensor Data, store in NAND FLASH Memory during Flight, retrieve the data from NAND FLASH Memory and

NAND Flash Based In-Flight Acquisition and Recording Unit for Accelerometer Sensor Assembly of Flight Control System

send to Rugged Laptop through Ethernet and RS232 during POST flight. In ASA-ARU, FPGA is communicating with ADC, RTC Memory, NAND FLASH Memory, Ethernet Physical Layer and RS232 Driver. The below sections gives the related information regarding System Initialization, Power on Self Test, Mode Identification, Acquisition Mode, Retrieval Mode, Inside FPGA modules, FPGA Constraints and Safety Considerations.

#### 3.2 System Initialization

ASA-ARU has ADC, NAND FLASH Memory, RTC with on-board Memory, Ethernet Physical Layer and RS232 transceiver. Each one is initialized using FPGA sub Modules such as Data Acquisition Controller, NAND FLASH Controller and RTC SPI Controller, Ethernet Controller, UART Controller and all these modules are controlled by the Top Module.

Figure 3.2 ASA-ARU system-Main Control Board

Figure 3.3 Controller modules of FPGA

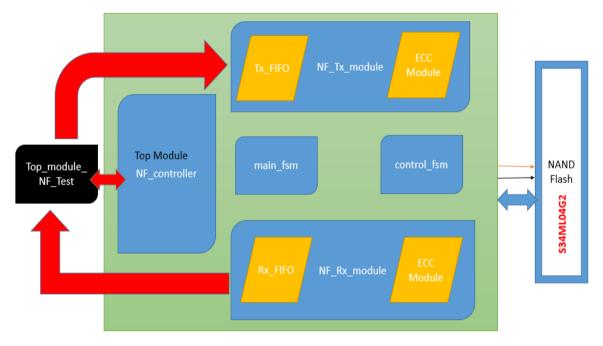

Figure 3.4 NAND Flash Controller module

# 3.3 NAND Flash Controller

Top module will enables operations like page read, page write, reset operation, readID (manufacture ID) operation and block erase operation.

- 1. Once FPGA\_RESET\_n is deasserted, POST operation will starts automatically. Check flash health status .

- 2. Check flash health is good and ASA-ARU health is good, go for the mode identification operation else exit the function.

- 3. If Acquisition mode (mode=0), It enables the bad block checking operation by making signal BB\_FSM\_en = 1, else Retrieval Mode (mode=1). In retrieval mode it enables the bad blocks read operation from the RTC controller by making BB\_retrieval\_FSM\_en = 1.

- 4. During Acquisition mode:

- If BB\_FSM\_en = 1 it enables the bad block checking operation by making page\_BB\_read\_en =1. This signal enables the bad block page read operation. Read 1<sup>st</sup> location of NF spare memory data. check for BB if block is bad block update the BB's address into BB\_FIFO memory. Check for all blocks (4096); once completion of this operation enables the BB\_opr\_comp BB\_opr\_comp it. Enable the program operation by making progm\_FSM\_en = 1.

- ii. Once Progm\_FSM\_en = 1, Read NF write completed page address from the RTC then read acquisition data from the DAQ controller. Assign page completion address to NF page address and block completion address to NF block address. Check if 0 send DAQ\_FIFO\_rd\_data daq\_stop = along with DAQ\_FIFO\_data\_valid signal and page\_write\_en=1. Wait for write\_complete=1 once write\_complete=1, check NF page and block address with completed page and block address if it not equal compare current address with bad block address if it not equal go for DAQ stop check and repeat the process up to dag stop = 1 else updated the NF address in the BB\_FIFO memory and compare next BB address with NF address.

- iii. Once daq\_stop=1, read session data from RTC controller and send to NF on last two pages.

- 5. During Retrieval mode:

- BB management operation :- If BB\_retrival\_FSM\_en = 1 read BB's address from RTC and store into BB\_FIFO memory. Once stored the all BB's into BB\_FIFO it generate BB\_FIFO\_filled = 1. BB\_FIFO\_filled it Enable the read operation by making read\_FSM\_en = 1.

- ii. Once read\_FSM\_en = 1, read BB address from DAQ controller and store into BB\_FIFO. Compare BB address with NF block address, if address are equal increment NF address by 1 and compare with BB address else address are different read data from NF by send Page\_read\_en = 1. Wait for Read\_complete=1 repeat the process.

- iii. Once page complete address and NF block and page address are equal read last two blocks first page data by enabling page\_read\_en =1.

- iv. After reading last two blocks  $1^{st}$  page data generate erase\_FSM\_en = 1.

- v. Once erase\_FSM\_en = 1, it will wait for the NF\_block\_erase\_en = 1. Once NF\_block\_erase\_en = 1, compares NF block address with BB block address if both are equal increment NF block address by 1 and compare with next BB address else both address are not equal erase NF block repeat the process.

#### 3.1.1 Data integrity for ASA-ARU:

The data recorded in-flight is fed to the actuators which then leads to the smooth functioning of the flight without any turbulence. The slightest change in this data, would lead to a large deviation from the original position, causing the flight to topple in the worst case. Thus, to avoid such disasters, the data from the accelerometer has to be accurate and reliable throughout the whole process of giving an input, processing and providing the feedback for the normal functioning of the whole system.

#### 3.2 FPGA-ARTIX 7:

- FPGA hardware: FPGA[14] is the main data processing hardware of the system. It is used for controlling various functions of the ASA-ARU such as POST analysis, Mode Identification, Data Acquisition Controlling, recording data into NAND Flash memory, retrieving data from NAND Flash memory, Transmitting retrieved data to GSE via Ethernet Interface and UART Controller.

- > FPGA Clock: A 25 MHz clock is used for FPGA operations and peripherals controlling.

- Artix-7 FPGAs are available in -3, -2, -1, -1LI, and -2L speed grades, with -3 having the highest performance. The Artix-7 FPGAs predominantly operate at a 1.0V core voltage.

- FPGA is used as a controller in ASA-ARU system. FPGA hardware used in ASA-ARU system is XC7A100T-2FTG256I ARTIX 7 FPGA. Artix 7 FPGA Hardware Description Language (HDL) developed in the 'VHDL' language. The operating environment details of the HDL are given in the below Table.