| CMR          |

|--------------|

| INSTITUTE OF |

| TECHNOLOGY   |

| Sub:         | b: Analog Circuits                                                                                                                                                      |                                                              | Co              | ode:                                                    | 18EC42     |            |                    |        |     |          |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------|---------------------------------------------------------|------------|------------|--------------------|--------|-----|----------|

| Date:        | 19/ 05 / 2021                                                                                                                                                           | Duration:                                                    | 90 mins         | Max Marks:                                              | 50         | Sem:       | 4 <sup>th</sup> Br | anch:  | ECE |          |

|              |                                                                                                                                                                         | A                                                            | nswer Any       | y FIVE FULL Q                                           | uestions   | 3          |                    |        |     |          |

|              |                                                                                                                                                                         |                                                              |                 |                                                         |            |            |                    | Marks  | CO  | BE<br>RB |

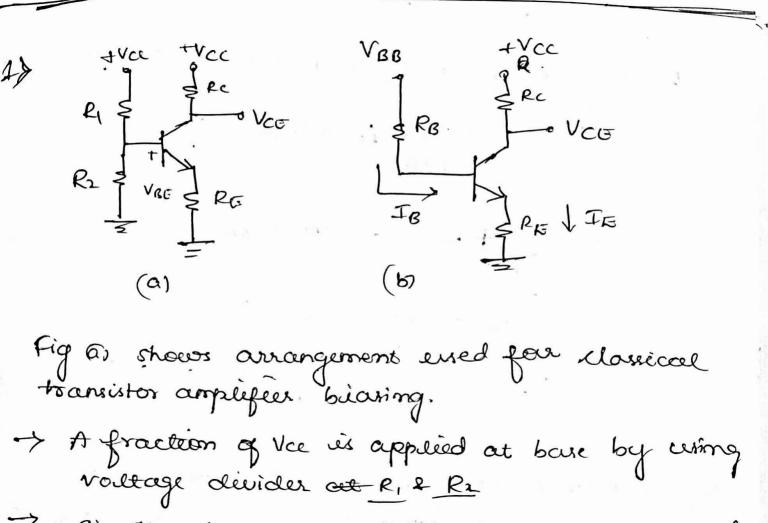

| disc         | th the help of necessar<br>crete biasing (voltage<br>on to stabilise the bias                                                                                           | divider biasin                                               |                 | •                                                       | •          |            |                    | s [10] | CO1 | L2       |

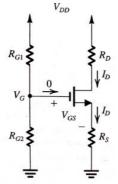

|              | Thy biasing a MOSFE inique?                                                                                                                                             | T amplifier c                                                | ircuit by fi    | ixing V <sub>GS</sub> is not                            | conside    | ed as a g  | ood                | [04]   | CO1 | L2       |

|              | b) With the help of necessary circuit diagrams and design equations, explain MOSFET biasing circuit by Fixing $V_G$ and connecting a resistance in the source.          |                                                              |                 |                                                         |            | [06]       | CO1                | L2     |     |          |

|              | the the great size of a con-                                                                                                                                            | $R_{B1} = 100 \text{ k}\Omega$ $R_{B2} = 50 \text{ k}\Omega$ | +15             | $R_{C} = 5 \text{ k}\Omega$ $R_{E} = 3 \text{ k}\Omega$ |            | n fouther  |                    | [10]   | CO1 | L3       |

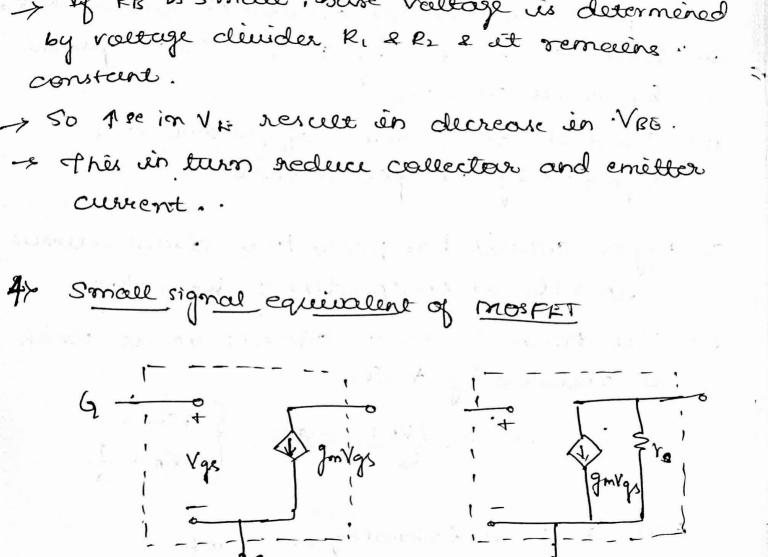

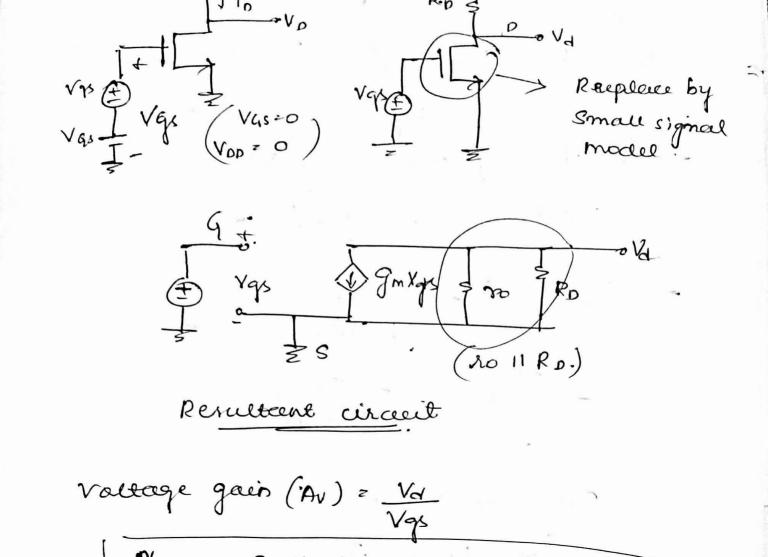

|              | h the small signal equal and transconductance                                                                                                                           |                                                              |                 | FET, derive an e                                        | expression | on for the | voltage            | [10]   | CO2 | L2       |

|              | Considering the conceptual circuit of Common Emitter BJT Amplifier, derive the following parameters; $g_m$ , $r_e$ , $r_\pi$ and $A_\nu$ . Draw the hybrid $\pi$ model. |                                                              |                 |                                                         | [10]       | CO2        | L2                 |        |     |          |

| spec<br>chai | ign a MOS Amplifications: $I_D = 0.5 m$ nge in the value of $I_D = 1.5 V$ . Consider $\lambda = 0.5 V$                                                                  | A, Vt=1V, K<br>obtained wh                                   | $C_n$ , $W/L=1$ | $mA/V^2, V_{DD}=15$                                     | V. Calcu   | late the   | percenta           | ge     |     |          |

[10]  $\left| \text{CO2} \right|_{\text{L3}}$

| 7. | Define the following characteristic parameters of Amplifiers using necessary circuit diagram. $A_v,A_{vo},G_{v,}G_{vo},G_m,R_i,R_{in}\text{and}R_{out}$                                                               | [10] | CO2 | L2 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|----|

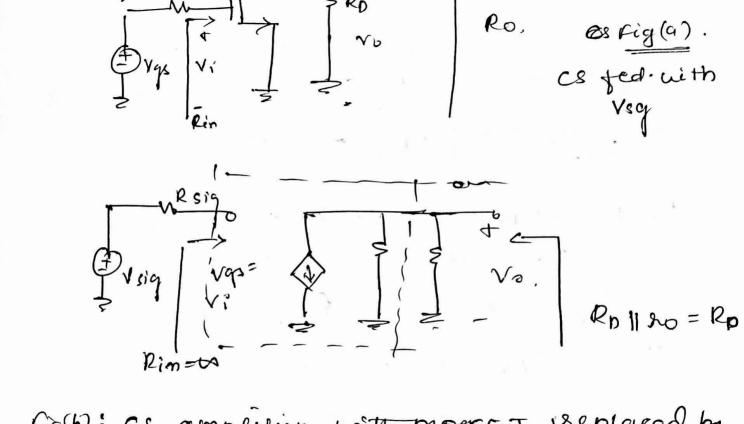

| 8. | With a neat circuit diagram and ac equivalent circuit, derive the expressions for Voltage gains $A_v$ , $A_{vo}$ , $G_{v_i}$ and Output resistance $R_{out}$ for a Common source amplifier without source resistance. |      | CO2 | L3 |

## IAT-1 (19/05/2021)

## **Analog Circuits Scheme**

## 4<sup>th</sup> Sem

Q-1 Diagram Voltage divider- 2 Marks

**Explanation-6 Marks**

Explanation of RE stabilization-2 marks

Q-2(a)Expalanation-4 Marks

Q2(b) Circuit Diagram-2 Marks

Explanation- 4 Marks

Q-3 Rth-1 marks

Vth-1 marks

Equivalent circuit -3 Mark

Ic, Ib, IE, VB, VC---- 5 marks (Each carries 1 mark)

Q-4 Small signal model-2 marks

Voltage gain-4 Marks

Transconductance-4 marks

Q-5 Circuit diagram-1 Marks

Gm, re, rpi, Av---8 Marks

Hybrid pi mosel-1 marks

Q-6 RD, RS, RG1, RG2---8 Marks

% change in ID= 2 marks

Q-7 Diagram -2 marks

Each parameter- 1 mark each (8x1= 8 marks)

Q-8 Circuit-2 marks

Each parameter - 2 mark each (4x2=8 marks)

$$\frac{I_{RE}\left(\frac{R_{B}}{1+R}\right)R_{E}}{I_{E}} = \frac{V_{BB} - V_{BE}}{R_{E} + R_{B}}$$

$$\frac{I_{RE}\left(\frac{R_{B}}{1+R}\right)R_{E}}{R_{E} + R_{B}}$$

$$\frac{I_{RE}\left(\frac{R_{B}}{1+R}\right)R_{E}}{R_{E} + R_{B}}$$

$$\frac{I_{RE}\left(\frac{R_{B}}{1+R}\right)R_{E}}{R_{E} + R_{B}}$$

pulling IB from equen 4 into 3 no have

VBB = IE RB + VBR + IERE

NOTER DIN order to make Ix insenselive

(i) Replace mosfet by equivalent curcient as the by short circuid (isi) Constant de cerrent if present de replaced by an open circuit. => Fig (a) circuit has prob, that drain current in saty is independent q drain vy -> But drain cument six depends on Vos which us modeled by 4. The  $\begin{cases} vehere \\ V_n = \frac{1}{\lambda} \end{cases}$ ro = 1 VA | →1

Foir a givon technology.

gm x kn' 1 gm x to, gm x Vor & (Vgs-Vt) -> gm increased by large he & small L We have, ED = 1 Km W (VGS-Vt)2 \[

\text{Vas-Vt} \times = \frac{2\int\_b L}{\kn' \times L}

\] Vas=Vt t 2 Joh But Sub, Values,

If

$$|P_{1}| = \frac{\sqrt{pp}}{\sqrt{pp}} = \frac{\sqrt{pp}}{\sqrt{pp}}$$

$$R_{s} = \frac{V_{s}}{I_{D}} = \frac{5}{0.25 \times 10^{-3}} = 10 \text{ Ks}^{-2}$$

$$\int V_{s} = \frac{V_{DD}}{3} = 5V$$

$$R_{s} = \frac{V_{s}}{I_{D}} = \frac{5}{0.5 \times 10^{3}} = 10 \text{ kg}$$

$$\left[ V_{S^{2}} \frac{V_{DD}}{3} = 5V \right]$$

7. change in

$$FD = 2$$

$Vt^{2}(.5) = 4 m_{1}/v_{1}$

$$FD = \frac{1}{2}kn^{1}\frac{1}{k}(Vas - Vt)^{2}$$

$$FD = \frac{1}{2}v_{1}v^{-3} \times (Vas - 1.5)^{2}$$

$$T_{0} = \frac{1}{2}\pi_{10}^{-3} \times (V_{as} - 1.5)$$

$$T_D = \frac{1}{2} n_{10}^{-3} \times (v_{as} - 1.5)^2$$

$$\frac{1}{2} \sum_{i=1}^{n} \frac{1}{2} \sum_{i=1}^{n} \frac{1}$$

$2 I_D = \left( \left( 1 - 20 I_D \right)^2 \right)$

19(b): Cs amplifier with most of replaced by Hybrid To smodel

the off terminal of amplifier. so Re well be placed.

As Vi = Vsig, Overall voltege gain

$$G_{V} = \frac{V_{0}}{V_{Rig}} = \frac{V_{0}}{V_{i}} = -9m(P_{0} || P_{L} || P_{0})$$

$$V_{B} = V_{CC} \times \frac{R_{BL}}{R_{BI} + R_{BL}} = 15 \times \frac{50 \times 10^{3}}{(100 + 10^{3})}$$

$$V_{B} = 54$$

RITPL

Substy. RE + (RB) RE + (RB) RE + (RB)

= 1029 110 7