# Scheme Of Evaluation Internal Assessment Test 2 – October 2019

| Sub:  |            | Analog ar | nd Digital I | Electronics   |    |      |     | Code:   | 18CS33 |

|-------|------------|-----------|--------------|---------------|----|------|-----|---------|--------|

| Date: | 15/10/2019 | Duration: | 90mins       | Max<br>Marks: | 50 | Sem: | III | Branch: | ISE    |

**Note:** Answer Any Five Questions

| Que | estion<br># | Description                                                                                                                                                                                                                                                                                                 | Marks l        | Distribution | Max<br>Marks |

|-----|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|--------------|

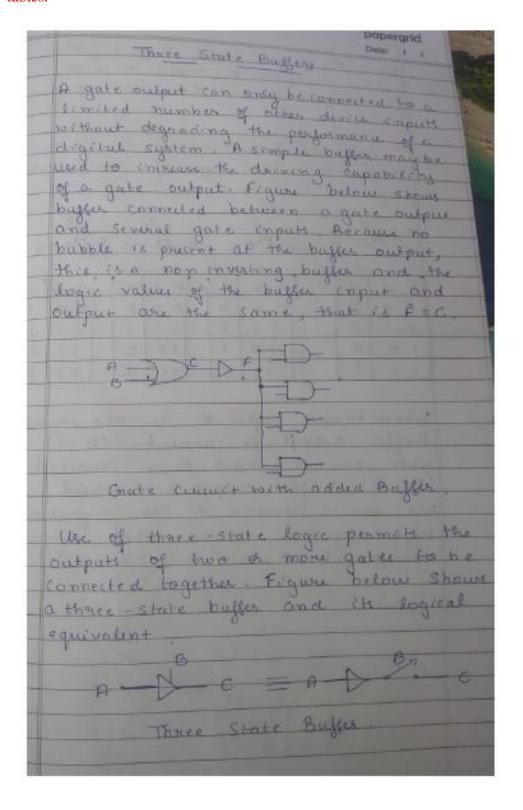

| 1   | a)          | What is a three state buffer? Explain the 4 types of three state buffers along with their truth tables.  • Buffer – description + purpose of buffer  • Tri-state buffer with diagram  • 4 types – description with truth tables                                                                             | 1M<br>1M<br>4M | 6M           | 10 M         |

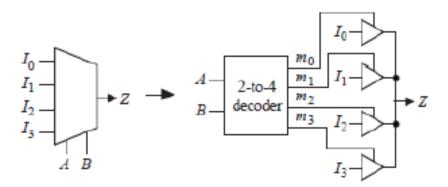

|     | b)          | <ul> <li>Implement a 4-to-1 MUX using four three-state buffers and a decoder.</li> <li>Show the implementation</li> <li>Basic description</li> </ul>                                                                                                                                                        | 3M<br>1M       | 4M           |              |

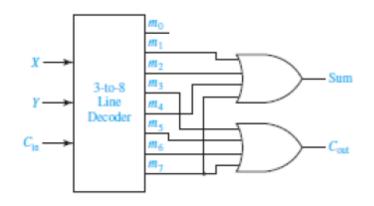

| 2   | a)          | Implement a full adder using 3 to 8 line decoder and 2 OR gates.  • Truth table and expression for sum and carry • Implementation                                                                                                                                                                           | 2M<br>3M       | 5M           | – 10 M       |

| 2   | b)          | <ul> <li>Implement a full subtractor using 3 to 8 line decoder with inverting outputs and 2 NAND gates.</li> <li>Truth table and expression for difference and borrow</li> <li>Implementation</li> </ul>                                                                                                    | 2M<br>3M       | 5M           | - 10 M       |

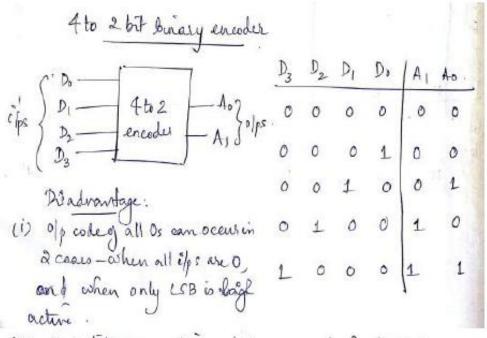

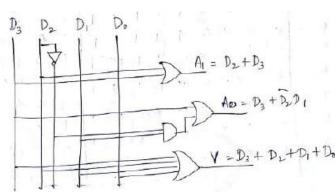

| 3   | a)          | <ul> <li>Derive the logic equations for a 4 to 2 line priority encoder and implement the same using basic gates.</li> <li>Disadvantage of 4 to 2 line priority encoder with truth table</li> <li>Priority encoder – truth table and description</li> <li>K-Map for outputs of priority encoder +</li> </ul> | 1M<br>2M       | 6M           | 10 M         |

|   |    | Expression for each output  • Implementation using basic gates                                                                                                                                                                                                                                                                                                                              | 2M<br>1M             |     |      |

|---|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----|------|

|   | b) | <ul> <li>Implement an 8 to 3 priority encoder using two 4 to 2 priority encoders.</li> <li>Implementation</li> <li>Explanation for how to get the expressions of outputs and valid output indicator</li> </ul>                                                                                                                                                                              | 3M<br>1M             | 4M  |      |

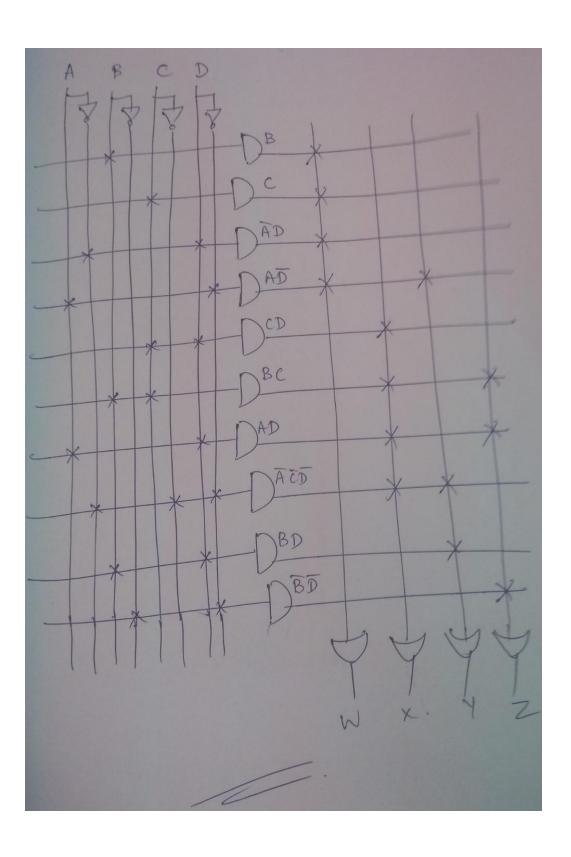

| 4 |    | Braille is a system which allows a blind person to read alpha-numeric by feeling a pattern of raised dots. Design a circuit using PLA that converts BCD to Braille. The below table shows the correspondence between BCD (denoted by ABCD) and Braille (denoted by WXYZ).     M                                                                                                             | 2M<br>4M<br>2M<br>2M | 10M | 10 M |

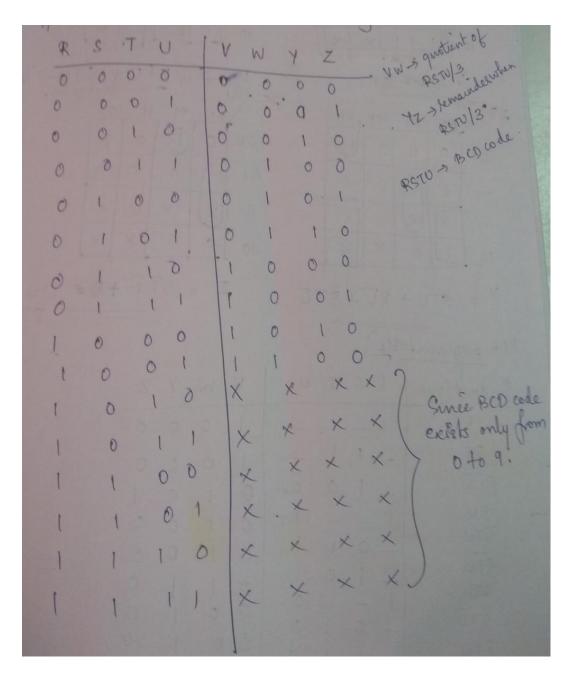

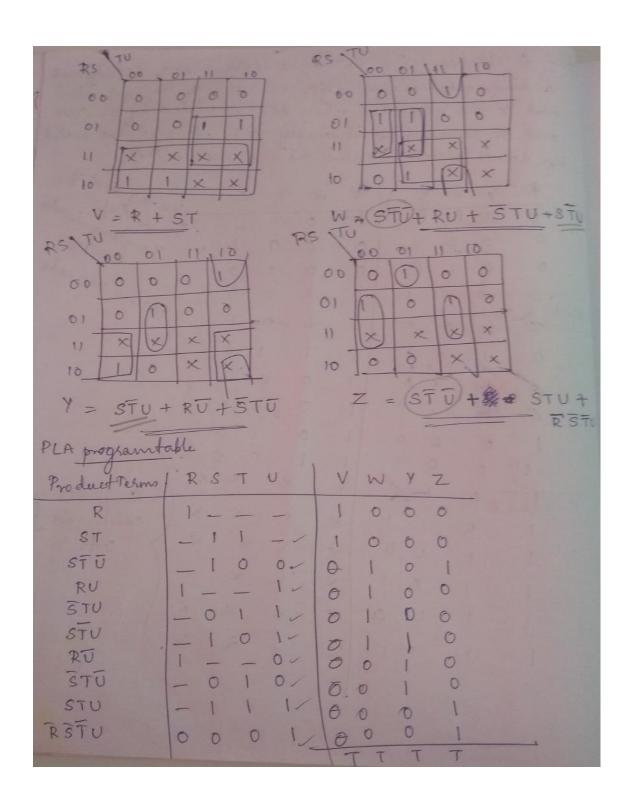

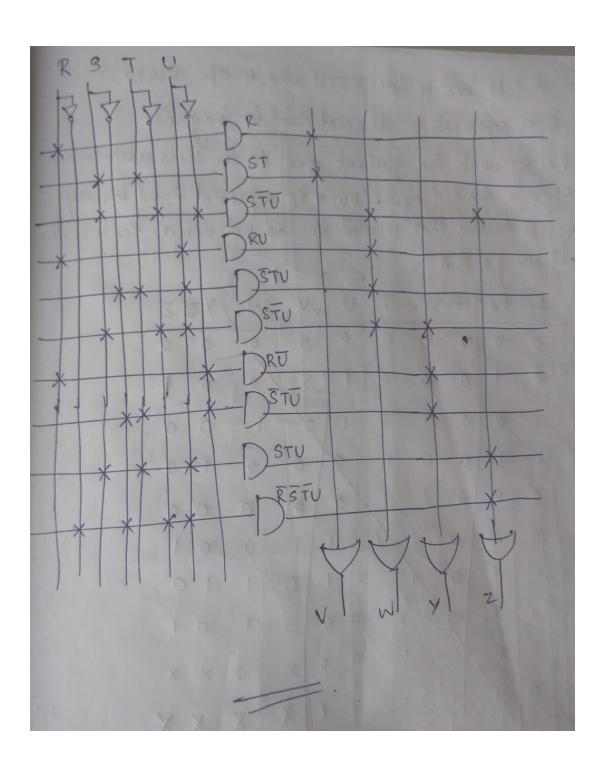

| 5 | a) | A circuit has four inputs RSTU and four outputs VWYZ. RSTU represents a binary coded-decimal digit. VW represents the quotient and YZ the remainder when RSTU is divided by 3 (VW and YZ represent 2-bit binary numbers). Assume that invalid inputs do not occur. Realize the circuit using a PLA.  • Truth table • Expressions for W, X, Y and Z using K-Map • PLA table • Implementation | 2M<br>4M<br>2M<br>2M | 10M | 10 M |

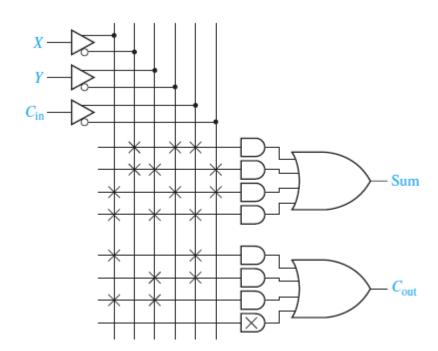

| 6 | a) | Generate the sum and carry functions of a full adder using a PAL.  • Truth table of full adder + Expressions for sum and carry  • Implementation of sum and carry on PAL                                                                                                                                                                                                                                                                                                                       | 2M<br>4M       | 6M  | 10M    |

|---|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|--------|

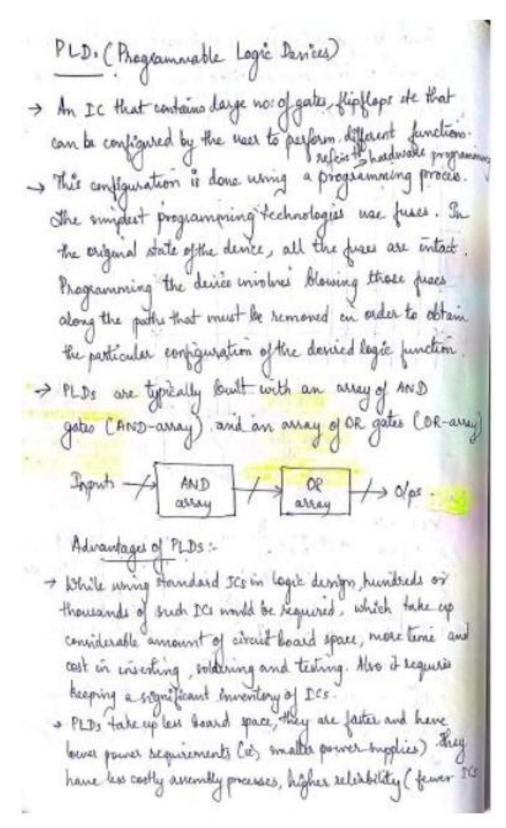

|   | b) | What are PLDs? Distinguish between the 3 main types of PLDs.  • Description of PLDs  • 3 types with general block diagram and description                                                                                                                                                                                                                                                                                                                                                      | 1M<br>3M       | 4M  |        |

|   | a) | Explain the working of an SR latch constructed using NOR gates.  • SR Latch diagrams  • Working of SR latch for each input combination                                                                                                                                                                                                                                                                                                                                                         | 2M<br>2M       | 4M  |        |

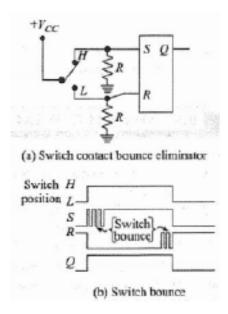

| 7 | b) | Explain switch contact bounce circuits. How can contact bounce be eliminated in mechanical switches?  • Circuit diagrams + output waveforms  • Description of contact bounce occurrence  • How to avoid contact bounce                                                                                                                                                                                                                                                                         | 2M<br>2M<br>2M | 6M  | - 10 M |

|   | 8  | With necessary diagrams and proper explanation, derive the truth table, state transition diagram, characteristic equation and excitation table for an SR flip-flop and a JK flip-flop.  • Definition of state transition diagram, characteristic equation and excitation table  • Truth table, state transition diagram, characteristic equation and excitation table for SR flip-flop  • Truth table, state transition diagram, characteristic equation and excitation table for JK flip-flop | 2M<br>4M<br>4M | 10M | 10 M   |

1a). What is a three state buffer? Explain the 4 types of three state buffers along with their truth tables.

When the enable input Bis 1, output a equals A. When Bis the output c ack like an open Concust Figure below shows the truth four types of three-sla tables for baffers. BAC BA C BA A Ö 001 2 0 0 0 0 0 01 010 Z Z 01 0 1 10 12 Z 10 10 0 10 11 Z 1 0 When enable imput B is not investo buffer output is enabled. (B=1) when enable input B is invested (B = 0), buffer output is disabled 2 to supplesed use a symbol high impedence state that occur when B=0, i.e Bis invented

## 1b). Implement a 4-to-1 MUX using four three-state buffers and a decoder.

### 2a). Implement a full adder using 3 to 8 line decoder and 2 OR gates.

|   | Input |     | Output |       |  |

|---|-------|-----|--------|-------|--|

| Α | В     | Cin | Sum    | Carry |  |

| 0 | 0     | 0   | 0      | 0     |  |

| 0 | 0     | 1   | 1      | 0     |  |

| 0 | 1     | 0   | 1      | 0     |  |

| 0 | 1     | 1   | 0      | 1     |  |

| 1 | 0     | 0   | 1      | 0     |  |

| 1 | 0     | 1   | 0      | 1     |  |

| 1 | 1     | 0   | 0      | 1     |  |

| 1 | 1     | 1   | 1      | 1     |  |

Sum =  $\Sigma$ m (1, 2, 4, 7) Carry =  $\Sigma$ m (3, 5, 6, 7)

# 2b). Implement a full subtractor using 3 to 8 line decoder with inverting outputs and 2 NAND gates.

|   | Input |   | Output     |        |  |  |

|---|-------|---|------------|--------|--|--|

| Α | В     | С | Difference | Borrow |  |  |

| 0 | 0     | 0 | 0          | 0      |  |  |

| 0 | 0     | 1 | 1          | 1      |  |  |

| 0 | 1     | 0 | 1          | 1      |  |  |

| 0 | 1     | 1 | 0          | 1      |  |  |

| 1 | 0     | 0 | 1          | 0      |  |  |

| 1 | 0     | 1 | 0          | 0      |  |  |

| 1 | 1     | 0 | 0          | 0      |  |  |

| 1 | 1     | 1 | 1          | 1      |  |  |

$x = \begin{bmatrix} x & & & & \\ y & & & & \\ Decoder & & \\ Deco$

Difference =  $\Sigma$ m (1, 2, 4, 7)

Borrow =  $\Sigma$ m (1, 2, 3, 7)

3a). Derive the logic equations for a 4 to 2 line priority encoder and implement the same using basic gates.

(ii) of 2 bits are active at the same time, it produces the wrong ofp oade.

- To overcome this, we go for Priorityencoder.

-> In apriority encoder," we arrige appriority to each clp bit. Say to bas for a 4 bit priority encoder. we assign highest priority to \$ D, and least provity

-> So if 2 ilps are high at the same time, only the ilp ey: for a 4 bit proposity encoder,  $D_2 o$  highest priority encoder,  $D_0 o$  lowest priority

| $\mathcal{D}_3$ | D2 | $\mathfrak{D}_{\gamma}$ | ps | A, | Ao | V 3 |

|-----------------|----|-------------------------|----|----|----|-----|

| 0               | ٥  | 0                       | 0  | 0  | D  | ð   |

| ð               | 0  | 0                       | 1  | 0  | 0  | 1   |

| 0               | 0  | 1                       | X  | 0  | 1  | 1   |

| 0               | 1  | х.                      | ×  | 1  | 0  | 1   |

| 1               | ×  | ×                       | x  | 1  | 1_ | 1   |

|                 |    |                         |    | 17 |    |     |

V is a valid of prindicator.

V-1 only if atleast one of the lips is active.

So when all ips are O, V is equal to O. Thus we can distinguish bl. 0000 and 0001 condition of ips.

|                                |     | distin     |                |       | 000      | )0 an      | nd 01 | 001               | cond | Then o         |

|--------------------------------|-----|------------|----------------|-------|----------|------------|-------|-------------------|------|----------------|

| D3 D2 \ (                      | 100 | ADO TO OR  | Di Do          | D, Do | 130      | D3D21      | 0,00  | A                 | es . |                |

| B 22                           | 0   | 0          | 1              | 0     |          |            | 000   | 0                 | 00   |                |

| $D_3 D_2$ $D_3 \overline{D}_2$ |     | 10         |                |       |          | 10 m ( )   |       | 1                 |      | A.             |

| 73.02.00                       | = 1 | 1/2 +<br>V | D <sub>3</sub> | 0     | 13       |            | App   | = D <sub>3</sub>  | + D, | D <sub>1</sub> |

|                                | 0   |            | 1              |       | <b>→</b> | <b>Y</b> = | D3 -  | +D <sub>2</sub> . | + Di | + D.           |

|      | $D_3$ | D <sub>2</sub> 1 | ), | Do - | A | A | V  |

|------|-------|------------------|----|------|---|---|----|

|      | 0     | ٥                | 0  | 0    | 0 | 0 | 0  |

|      | 0     | 0                | 0  | 41   | 0 | 0 | 1  |

|      | 0     | ٥                | 1  | 0    | 0 | 1 | .1 |

| 1    | 0     | ð                | .1 | ı    | 0 | 1 | 1  |

| 1    | 0     | i I              | 0. | ð    | 1 | 0 | 1  |

|      | 0     | t                | ۵  | 1    | 1 | 0 | 1  |

|      | O     | ì                | 1  | 0    | 1 | 0 | 1  |

| 1920 | 0     | 1                | 1  | 1    | 1 | 0 | 1  |

| -    | 1     | 0                | 0  | 0    | 1 | 1 | 1  |

|      | t     | 0                | 0  | 1.   | 1 | 1 | 1  |

|      | Ţ     | 0                | t  | ٥    | 1 | 1 | 1  |

|      | 1     | ð                | t  | 1    | 1 | 1 | 1  |

|      | 1     | 1                | 0  | ð    | 1 | 1 | 1  |

|      | t     | 1                | 0  | 1    | 1 | 1 | 1  |

|      | Ī     | 1                | Į  | 0    | 1 | 1 | 1  |

|      | 1     | Į                | 1  | 1    | 1 | 1 | 1  |

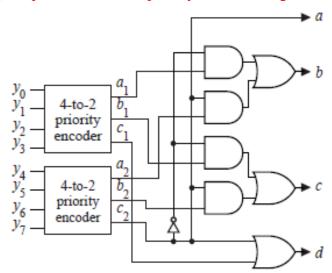

3b). Implement an 8 to 3 priority encoder using two 4 to 2 priority encoders.

If any of the inputs  $y_0$  through  $y_7$  is 1, then d of the 8-to-3 decoder should be 1. But in that case,  $c_1$  or  $c_2$  of one of the 4-to-2 decoders will be 1. So  $d = c_1 + c_2$ .

If one of the inputs  $y_4$ ,  $y_5$ ,  $y_6$ , and  $y_7$  is 1, then a should be 1, and b and c should correspond to  $a_2$  and  $b_2$ , respectively. Otherwise, a should be 0, and b and c should correspond to  $a_1$  and  $b_1$ , respectively. So  $a = c_2$ ,  $b = c_2 a_2 + c_2 a_1$ , and  $c = c_3 b_3 + c_5 b_4$ .

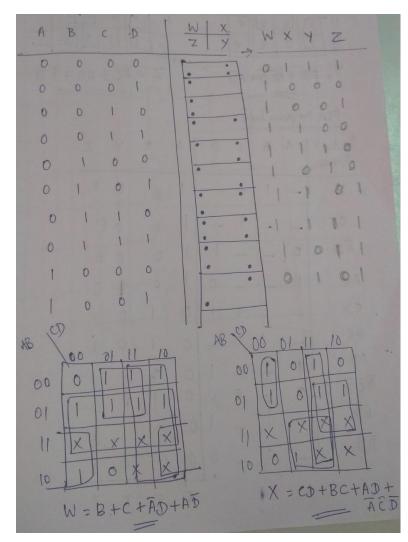

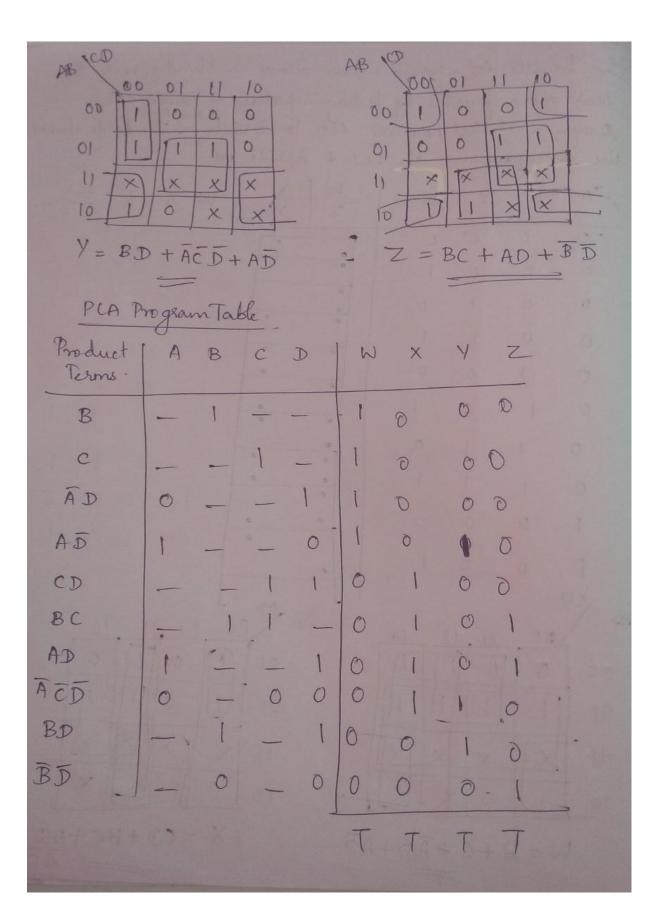

4. Braille is a system which allows a blind person to read alpha-numeric by feeling a pattern of raised dots. Design a circuit using PLA that converts BCD to Braille. The below table shows the correspondence between BCD (denoted by ABCD) and Braille (denoted by WXYZ).

|   |   |   |   | W | X |

|---|---|---|---|---|---|

| A | В | C | D | Z | Y |

| 0 | 0 | 0 | 0 |   | : |

| 0 | 0 | 0 | 1 |   | , |

| 0 | 0 | 1 | 0 |   |   |

| 0 | 0 | 1 | 1 |   | • |

| 0 | 1 | 0 | 0 | [ | : |

| 0 | 1 | 0 | 1 |   |   |

| 0 | 1 | 1 | 0 | : | • |

| 0 | 1 | 1 | 1 | : | : |

| 1 | 0 | 0 | 0 | : | • |

| 1 | 0 | 0 | 1 |   | • |

5. A circuit has four inputs RSTU and four outputs VWYZ. RSTU represents a binary coded-decimal digit. VW represents the quotient and YZ the remainder when RSTU is divided by 3 (VW and YZ represent 2-bit binary numbers). Assume that invalid inputs do not occur. Realize the circuit using a PLA.

# 6a). Generate the sum and carry functions of a full adder using a PAL.

|   | Inputs | 1               | Outputs |   |  |

|---|--------|-----------------|---------|---|--|

| x | у      | C <sub>in</sub> | Cout    | s |  |

| 0 | 0      | 0               | 0       | 0 |  |

| 0 | 0      | 1               | 0       | 1 |  |

| 0 | 1      | 0               | 0       | 1 |  |

| 0 | 1      | 1               | 1       | 0 |  |

| 1 | 0      | 0               | 0       | 1 |  |

| 1 | 0      | 1               | 1       | 0 |  |

| 1 | 1      | 0               | 1       | 0 |  |

| 1 | 1      | 1               | 1       | 1 |  |

$$Sum = X'Y'C_{in} + X'YC'_{in} + XY'C'_{in} + XYC_{in}$$

$$C_{out} = XC_{in} + YC_{in} + XY$$

6b). What are PLDs? Distinguish between the 3 main types of PLDs.

and ext connections means cance troubleshooting) and availability of design software. PROM PAL PLA - Atypical PLD may have hundreds to millions of goods . So in order to show the internal logic diagram for such technologies in a concise form, special symbolo for array logic are used Connentional Symbols Programmable Logic Devices (PLD2) - record or suite reconfigurable digital chie PROM "Programmable (Programmable (Programmable Logic Read only Hemory) trony Logic ) Array ) i/p -) AND gete amay is → Both AND and OR gate AND gate array can be dixed of cond-bolattoned arrage can be programmed. - DR gate away can be - OR gate array is oked + -) More versatile than Proud PA pregrammed! count be altered. - More complicated to utilize, since - Earth AND gotte produces the not of fisible links are doubled one of the possible minterns.

# 7a). Explain the working of an SR latch constructed using NOR gates.

Flip glop changes state after the success edge of the choice Set State :-Os Shown in State table, if the R input is at hour level and 5 input at high level (RS=01), during a low - to high transition on close pulse SR Flip glop is Said to be in Set State and output of Slip flop is set to 1 (8=1) Reset State If the R input is at high level and & input at low level (Rs=10). during a low to high transition on block pulse SR glip glop is Said to be in Reset state and output of SR glip flop is quet to 0 (0=0) Nochage state: When both se R equal bo zeno (SR = 00), then output Remains in previous state. Invalid State: When both SER equal to one (SR = 11), then output will be invalid.

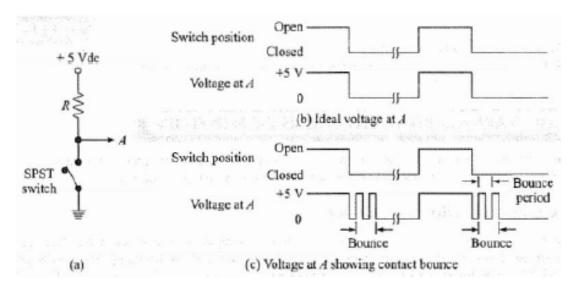

# 7b). Explain switch contact bounce circuits. How can contact bounce be eliminated in mechanical switches?

In nearly every digital system there will be occasion to use mechanical contacts for the purpose of conveying an electrical signal; examples of this are the switches used on the keyboard of a computer system. In each case, the intent is to apply a high logic level (usually +5 Vdc) or a low logic level (o Vdc). The single-pole single-throw (SPST) switch shown in the figure (a) below is one such example. When the switch is open, the voltage at point A is +5 V dc; when the switch is closed, the voltage at point A is O V dc. Ideally, the voltage waveform at A should appear as shown in figure (b) as the switch is moved from open to closed, or vice versa.

In actuality, the waveform at point A will appear more or less as shown in figure (c), as the result of a phenomenon known as contact bounce. Any mechanical switching device consists of a moving contact arm restrained by some sort of a spring system. As a result, when the arm is moved from one stable position to the other, the arm bounces, much as a hard ball bounces when dropped on a hard surface. The number of bounces that occur and the period of the bounce differ for each switching device. Notice carefully that in this particular instance, even though actual physical contact bounce occurs each time the switch is opened or closed, contact bounce appears in the voltage level at point A only when the switch is closed

If the voltage at point A is applied to the input of a TTL circuit, the circuit will respond properly when the switch is opened, since no contact bounce occurs. However, when the switch is closed, the circuit will respond as if multiple signals were applied, rather than the single-switch closure intended - the undesired result of mechanical contact bounce. There is a need here for some sort of electronic circuit to eliminate the contact bounce problem.

#### RS Latch Debounce Circuit

The RS latch in the figure above will remove any contact bounce due to the switch. The output (Q) is used to generate the desired switch signal. When the switch is moved to position H, R = o and S = 1. Bouncing occurs at the S input due to the switch. The flip-flop "sees" this as a series of high and low inputs, settling with a high level. The flip-flop will immediately be set with Q = 1 at the first high level on S. When the switch bounces, losing contact, the input signals are R = S = 0, therefore the flip-flop remains set (Q = 1). When the switch regains contact, R = 0 and R = 0; this causes an attempt to again set the flip-flop. But since the flip-flop is already set, no changes occur at R = 0. The result is that the flip-flop responds to the first, and only to the first, high level at its R = 0 input, resulting in a "clean" low-to-high signal at its output R = 0.

When the switch is moved to position L, S = o and R = 1. Bouncing occurs at the R input due to the switch. Again, the flip-flop "sees" this as a series of high and low inputs. It simply responds to the first high level, and ignores all following transitions. The result is a "clean" high-to-low signal at the flip-flop output.

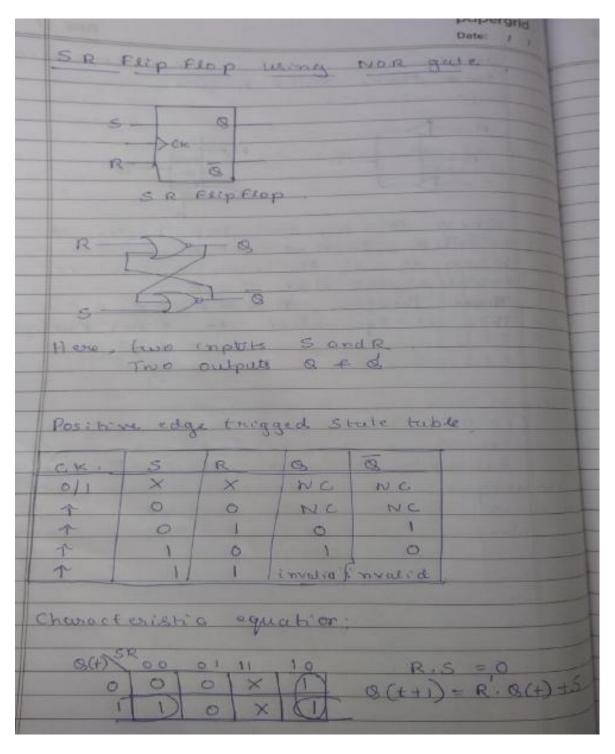

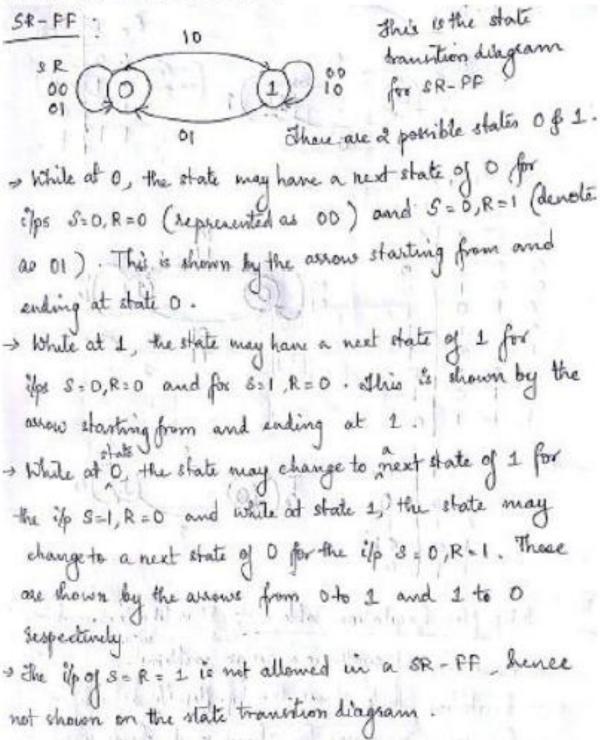

8. With necessary diagrams and proper explanation, derive the truth table, state transition diagram, characteristic equation and excitation table for an SR flip-flop and a JK flip-flop.

Characteristic Equations of Flip-fleps:

- Used for analyzing okts made of flip-flops:

- The next ofp. Quest is expressed as a function of present of 8,0 and i/p to the flip-flops:

- K-maps are used to get the optimized expression and the truth table of each FF is mapped into it.

- The states of sequential chief are represented using binary variables. For a sequential chi with n state variables (where n is possibly large), the nos of possible states (2°) is finite. Hence sequential chis are called as finite state machines. State transition diagram is a very conservent tool to describe a FSM. It is obtained from the truth table of a FF or to diaracteristic equation.

OSPESS:

Tach FF can be set at either 0 state or 1 state defined by to stored value at any given time. Application of ilp may change the stored value, is, state of the FF. This is shown by a directional arrow and the corresponding ilp is written along order it.

- , The timing relation implicit in FF touth tables are brought to the forefront by the FSM concept of state transition diagram.

Php-1 lop Excitation Table. - It is like looking at the truth tale in a severe way.

-> Used in cht synthesis orderign problems.

JExcitation table shows the flip-flop ilp as adependent function of transition on Jan, ie, it shows what all ilps must be applied to a FP in order to achieve a derived state from tion from 9, to 9, 1+

also be obtained from the characteristic table / egn or truth

### (a) SR flip-flop

Characteristic equation of SR FF

|    | Din. | s | R.  | Bott |                 |

|----|------|---|-----|------|-----------------|

| 7. | 0    | 0 | 0-  | 0    |                 |

|    | 0    | 0 | 1   | 0    |                 |

|    | 0    | 1 | 0   | 1    | o Se.           |

|    | 0    | 1 | 1   | ×    | 00 01 11 10     |

|    | 1    | 0 | 0   | 1    | 0000 0 1 1 35.  |

|    | 1    | 0 | - ( | 0    | O X D OR        |

|    | 1    | 4 | 0   | 1    |                 |

|    | 1    | 1 | 1   | x    | , . On+ = S+RQn |

The logic equations are presented in SOP form by fearing the largest group of 13 for each FF for SR-FF, since S=R=1 ilp is not allowed, we put don't cases (x) in the consequenting K-map locations, it whether 9mm is 0 or 1, an ip combination of S=R=1 will never assis.

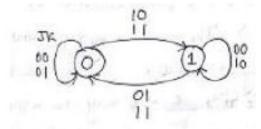

State transition diagram of SR FF

## Excitation Table of SR FF

The excitation table can be explained as follows:

- -> If an = 0, then on applying S=0 and R= oor 1 (ie, x), the and becomes 0.

- of an = 0, applying S = 1 and R > 0 makes ans = 1

- → of Sn=1, applying S=0 and R=1 makes ant =0.

- Ant = 1. applying So ov 1 (u, x) and R=0 makes

Excitation tables can be obtained for the other per in a smiler manner.

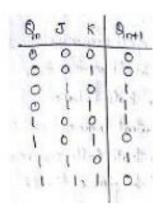

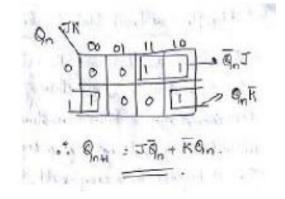

# (b) JK flip-flop

# Characteristic equation of JK FF

# State transition diagram of JK FF

## Excitation Table of JK FF

| Qn  | Anti | -  | J | K |   |

|-----|------|----|---|---|---|

| 0   | b    |    | 0 | X |   |

| 0   | 1    | 41 | 1 | X |   |

| - 1 | 0    |    | x | 1 |   |

| - 1 | 1    |    | X | 0 | * |

|     |      | ١. |   |   |   |