|                                                                                   |                                                |                                |                                                |                                    |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                | I                              | nteri                       | nal A                                  | ssess                                       | men                             | t Te                                | st III                                                 |                  |                |                                |                                           |            |      |     |    |

|-----------------------------------------------------------------------------------|------------------------------------------------|--------------------------------|------------------------------------------------|------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------|-----------------------------|----------------------------------------|---------------------------------------------|---------------------------------|-------------------------------------|--------------------------------------------------------|------------------|----------------|--------------------------------|-------------------------------------------|------------|------|-----|----|

|                                                                                   |                                                |                                |                                                |                                    |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                |                             | No                                     | vemb                                        | er 20                           | 19                                  |                                                        |                  |                |                                |                                           |            |      |     |    |

| Sub:                                                                              | Adva                                           | nced                           | Con                                            | npute                              | er Arc                                          | chite                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | cture                                          | <b>,</b>                       |                             |                                        |                                             |                                 | Sul                                 | Code                                                   |                  | 15C            | S72                            | В                                         | ranch: CSE |      |     |    |

| Date:                                                                             |                                                |                                |                                                | Duration:                          |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90 mins                                        |                                |                             | Max Marks:                             |                                             |                                 | Sem / Sec:                          |                                                        | :                | VII            |                                |                                           |            |      | OB  | E  |

|                                                                                   | 18/11                                          | 1/2019                         | 9                                              |                                    |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                |                             |                                        |                                             |                                 |                                     |                                                        |                  | A,B            |                                |                                           | ,C         |      |     |    |

|                                                                                   | •                                              |                                |                                                |                                    |                                                 | <u>A</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | nswe                                           | er an                          | y FIV                       | VE F                                   | ULL                                         |                                 |                                     |                                                        | 1                |                |                                |                                           | MAF        | RK S | СО  | RB |

| Questions  1 (a) Explain multiply pipeline design to multiply two 8-bit integers. |                                                |                                |                                                |                                    |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                                |                             |                                        |                                             |                                 |                                     |                                                        |                  | Τ              |                                |                                           |            |      |     |    |

| 1 (a)                                                                             | Expla                                          | in mı                          | ultip                                          | oly pi                             | ipelii                                          | ne de                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | esigr                                          | n to                           | mult                        | iply                                   | two                                         | 8-bit                           | inte                                | egers.                                                 |                  |                |                                |                                           | (0         | 6)   | CO2 | L2 |

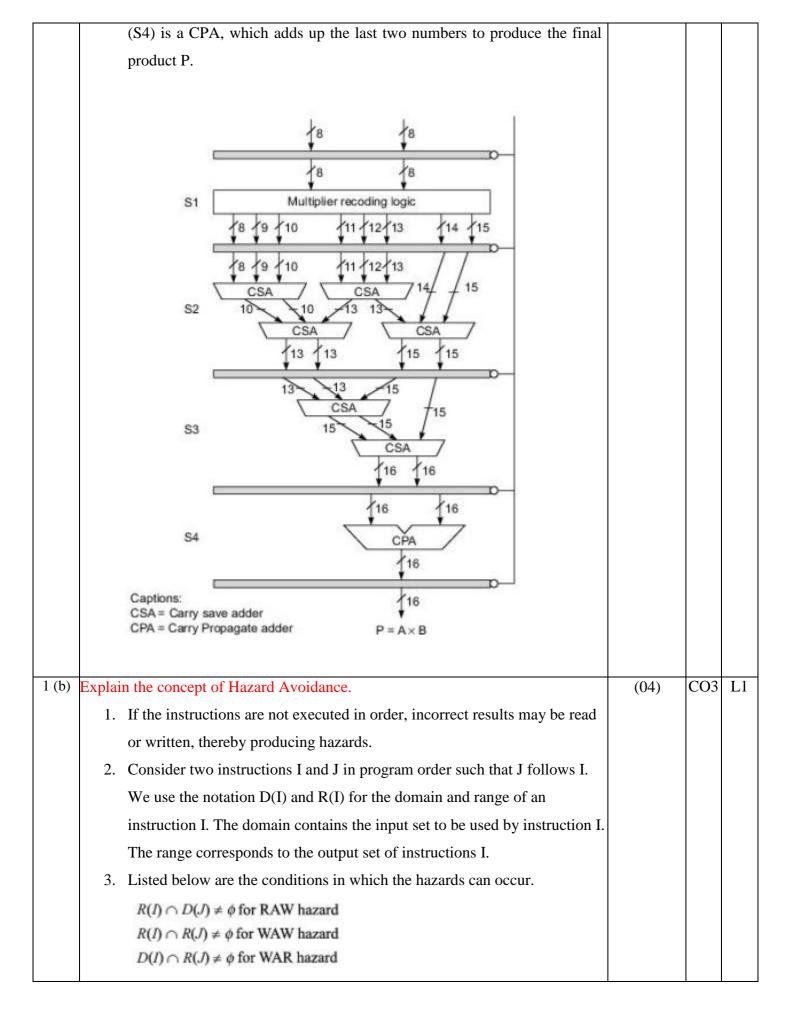

|                                                                                   | 1.<br>                                         | who<br>wri<br>P =              | ere<br>tten<br>: A *                           | P is<br>as tl<br>* B =             | the<br>ne su                                    | 16<br>.mm<br>+ P <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit ation                                      | prod<br>n of -<br>2 + F        | luct.<br>eigh               | Thi<br>t par<br>P <sub>4</sub> +       | s fix<br>tial p                             | ed-p<br>rodu                    | oint<br>ects                        | 3-bit in multi as sho e * and 1 0 0 0 0 0 0 0 0 1      | plio<br>wn       | catio<br>belo  | n ca<br>w:                     | an be                                     |            |      |     |    |

|                                                                                   | <ol> <li>2.</li> <li>3.</li> <li>4.</li> </ol> | mulleft The of C The to 1 of f | Itiple for sure SAA transfer first before ging | j = 0 mma as plu st sta its si CSA | d A loo, 1, 2 loo ation us a Camulta A's a m 13 | by the control of the | ne jth, 7.  he e at the enera ously t ess 15 b | h bit light he fi lates y. The | part nal s all e ne se ally | B an tial pastage ight economers third | d the produce, as spartid. Stages end stage | cts in show all pringe Sight is | s do<br>n in<br>odu<br>32 is<br>num | I by g the i one wi figure cts, ra made abers i nsists | th a girnging up | Waven hof tour | oits tallace below wo less nur | to the e tree w. 8 bits evels nbers s and |            |      |     |    |

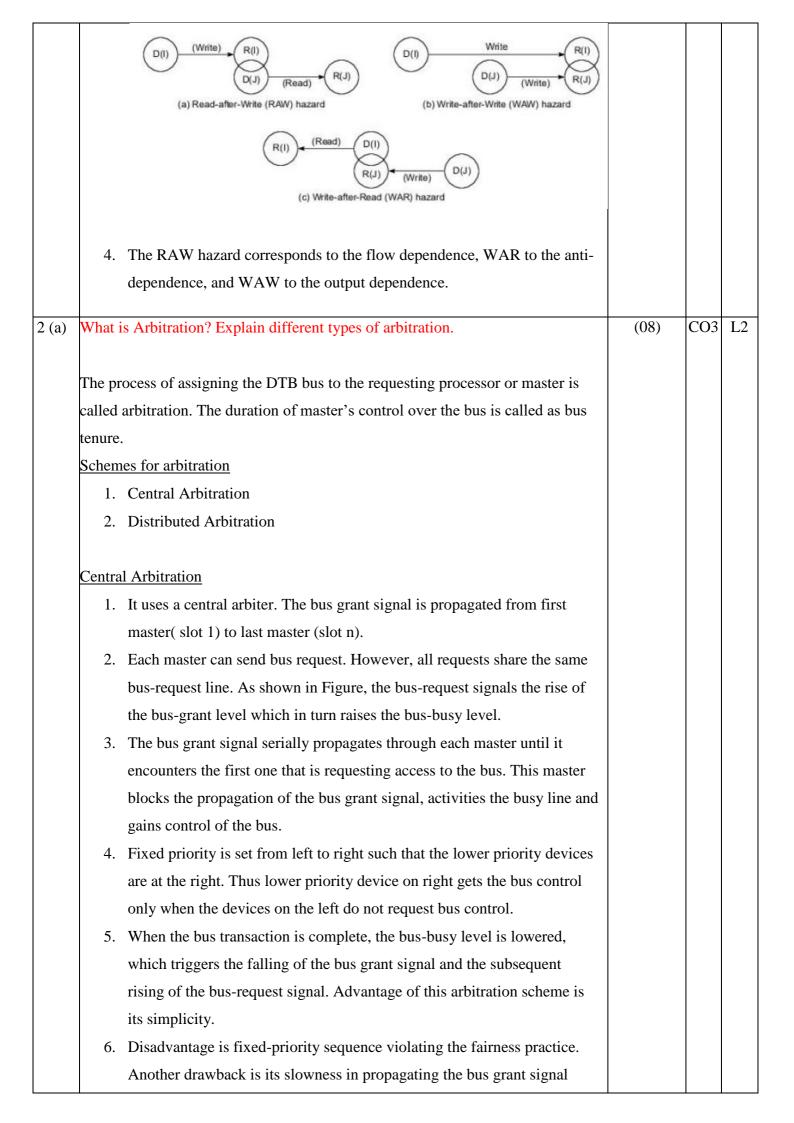

- along the daisy chain.

- 7. Whenever a higher-priority device fails, all the lower-priority devices on the right of the daisy chain cannot use the bus.

Independent Request and Grant: Instead of using shared request and grant lines as in Figure, multiple bus-request and bus-grant signal lines can be independently provided for each potential master as shown in figure. But the total number of signal lines required is larger. The arbitration among potential masters is still carried out by a central arbiter. However, any priority based or fairness-based bus allocation policy can be implemented. The advantage is their flexibility and faster arbitration time compared with the daisy-chained policy. The drawback is the large number of arbitration lines used.

#### Distributed Arbitration

1. Each potential master is equipped with its own arbiter and a unique

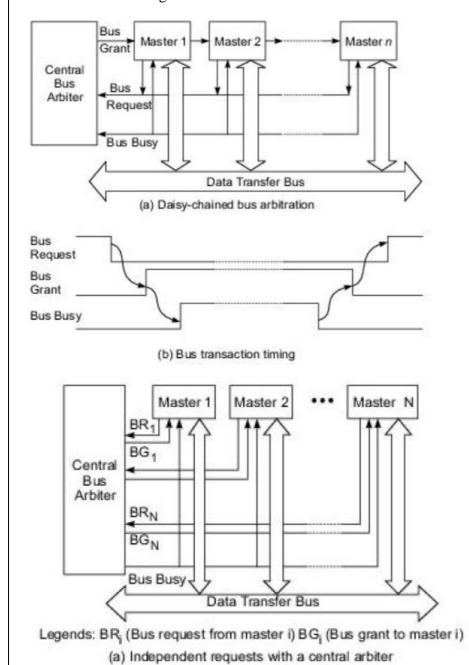

arbitration number. 2. When two or more devices compete for the bus, the winner is the one whose arbitration number is the largest. 3. All potential masters can send their arbitration numbers to the shared-bus request grant (SBRG) lines on the arbitration bus 4. Each arbiter compares the resulting number on the SBRG lines with its own arbitration number. If the SBRG number is greater, the requester is dismissed. At the end, the winner's arbitration number remains on the arbitration bus. After the current bus transaction is completed, the winner seizes control of the bus. 5. It is shown in figure given below Master 2 Master N Master 1 Arbiter 1 Arbiter 2 Arbiter N Data Transfer Bus Legends: BG (Bus grant) BB (Bus busy) AN (Arbitration number) (b) Using distributed arbiters CO3 L2 2 (b) Explain the concept of Store and Forward routing. (02)1. Packets are the basic unit of information flow in store and forward network. 2. A packet is transmitted from a source node to a destination node through a sequence of intermediate nodes. 3. When a packet reaches an intermediate node, it is first stored in the buffer. Then it is forwarded to the next node if the desired output channel and a packet buffer in the receiving node are both available. 4. The latency in store-and-forward networks is directly proportional to the distance (the number of hops) between the source and the destination, this routing scheme was implemented in the first generation of multicomputer.

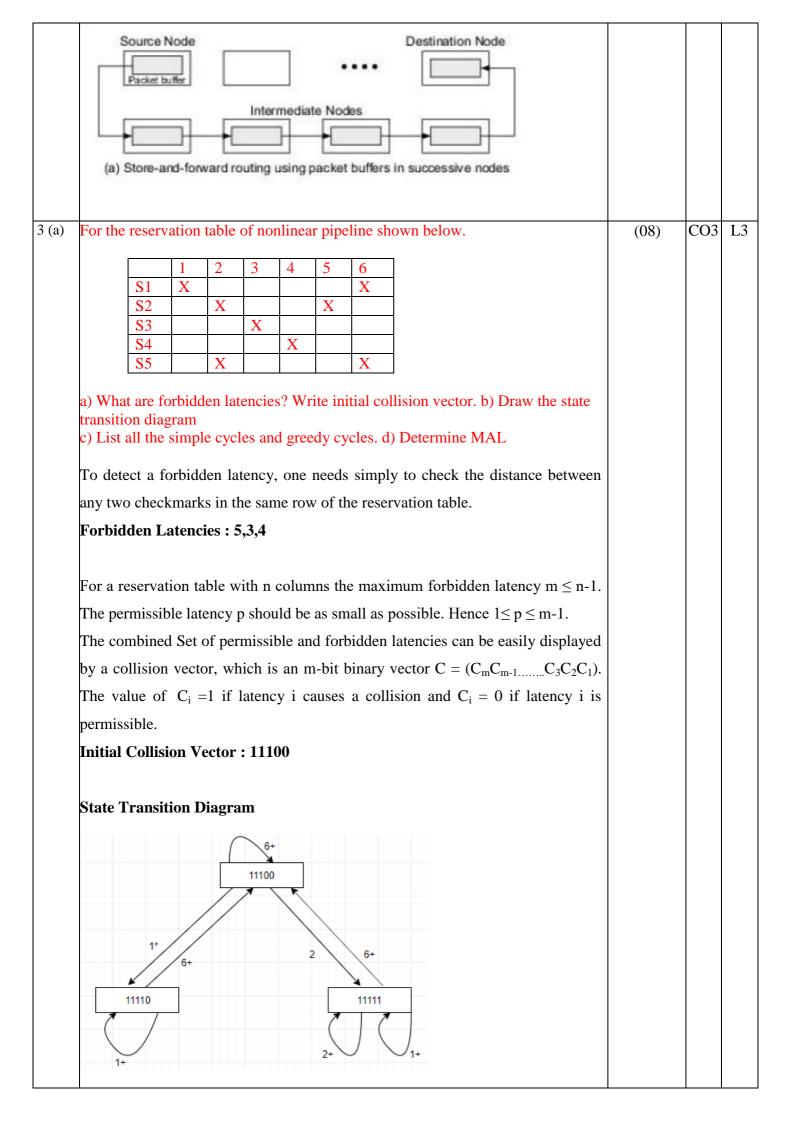

|       | Simple Cycles: (1),(1,6),(2),(2,6)                                                                                                                                                                                                                                                                                                                   |      |     |     |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|

|       | Greedy Cycles : (2),(1,6) MAL : 2                                                                                                                                                                                                                                                                                                                    |      |     |     |

| 3 (b) | Define following terms                                                                                                                                                                                                                                                                                                                               | (02) | CO3 | L1  |

|       | 1. Latency Cycle 2. Greedy Cycle                                                                                                                                                                                                                                                                                                                     |      |     |     |

|       |                                                                                                                                                                                                                                                                                                                                                      |      |     |     |

|       | Latency Cycle: It is is a latency sequence which repeats the same subsequence (cycle)                                                                                                                                                                                                                                                                |      |     |     |

|       | indefinitely.                                                                                                                                                                                                                                                                                                                                        |      |     |     |

|       | A greedy cycle is one whose edges are all made with minimum latencies from their                                                                                                                                                                                                                                                                     |      |     |     |

|       | respective starting states                                                                                                                                                                                                                                                                                                                           |      |     |     |

| 4 (a) | Explain any two Context Switching policies.                                                                                                                                                                                                                                                                                                          | 02   | CO4 | L2  |

|       | Four context switching policies are given below.                                                                                                                                                                                                                                                                                                     |      |     |     |

|       | Switch on cache miss: This policy corresponds to the case where a context is preempted                                                                                                                                                                                                                                                               |      |     |     |

|       | when it causes a cache miss. Let R be the average interval between misses and L the                                                                                                                                                                                                                                                                  |      |     |     |

|       | time required to satisfy the miss. Here, the processor switches contexts only when it is                                                                                                                                                                                                                                                             |      |     |     |

|       | certain that the current one will be delayed for a significant number of cycles.                                                                                                                                                                                                                                                                     |      |     |     |

|       | Switch on every load: This policy allows switching on every load independent of                                                                                                                                                                                                                                                                      |      |     |     |

|       | whether it will cause a miss or not. R represents the average interval between loads.                                                                                                                                                                                                                                                                |      |     |     |

|       | Switch on every instruction: This policy allows switching on every instruction,                                                                                                                                                                                                                                                                      |      |     |     |

|       | independent of whether it is a load or not. In other words, it interleaves the instructions                                                                                                                                                                                                                                                          |      |     |     |

|       | from different threads on a cycle-by-cycle basis. Successive instructions become                                                                                                                                                                                                                                                                     |      |     |     |

|       | independent, which will benefit pipelined execution. However, the cache miss may                                                                                                                                                                                                                                                                     |      |     |     |

|       | increase due to breaking of locality.                                                                                                                                                                                                                                                                                                                |      |     |     |

|       | Switch on block of instruction: Blocks of instructions from different threads are                                                                                                                                                                                                                                                                    |      |     |     |

|       | interleaved. This will improve the cache-hit ratio due to locality. It will also benefit                                                                                                                                                                                                                                                             |      |     |     |

|       | interioused. This will improve the eache intractor due to recallty. It will discontinue                                                                                                                                                                                                                                                              |      |     |     |

|       | single-context performance                                                                                                                                                                                                                                                                                                                           |      |     |     |

| 1 (b) | single-context performance  Explain the sequential and weak consistency model with a neat diagram                                                                                                                                                                                                                                                    | (08) | CO3 | 1.2 |

| 4 (b) | single-context performance  Explain the sequential and weak consistency model with a neat diagram.                                                                                                                                                                                                                                                   | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.                                                                                                                                                                                                                                                                               | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model                                                                                                                                                                                                                                                 | (08) | CO3 | L2  |

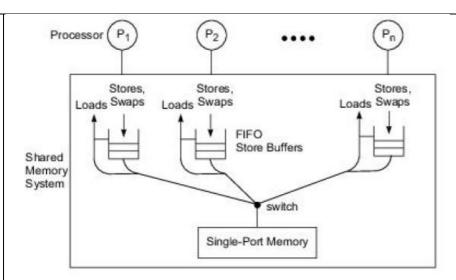

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in                                                                                                                                                         | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the                                                                         | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in                                                                                                                                                         | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the processors.                                                             | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the                                                                         | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the processors.                                                             | (08) | CO3 | L22 |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the processors.                                                             | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the processors.                                                             | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the processors.  Processors  P1  P2  P3  Pn  Shared  Memory                 | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the processors.  Processors  P1  P2  P3  Pn  Pn  Pn  Pn  Pn  Pn  Pn  Pn  Pn | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the processors.  Processors  P1  P2  P3  Pn  Shared  Memory                 | (08) | CO3 | L2  |

| 4 (b) | Explain the sequential and weak consistency model with a neat diagram.  Sequential Consistency Model  In this model, loads, stores and swaps of all processors appear to execute serially in single global memory order that conforms to the individual program order of the processors.  Processors  P1  P2  P3  Pn  Shared  Memory                 | (08) | CO3 | L2  |

- time, and a switch that connects this memory to one of the processors for the duration of each memory operation.

- 2. The order in which the switch is thrown from one processor to another determines the global order of memory-access operations which is observed by all processors.

- 3. Also the strong ordering of all the shared memory accesses in the sequential consistency model preserves the program order in all processors.

- 4. Also another processor is not allowed to access a shared memory until the recent value written to shared memory has been globally performed. This may require the propagation of all shared-memory accesses to all processors, which is rather time-consuming and costly.

- 5. Also sequential consistency model has poor scalability.

Lamport's Definition: A multiprocessor system is sequentially consistent if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program.

Dubois, Seheurich, and Briggs(DBS) (1986) have provided the following two sufficient conditions to achieve sequential consistency in shared-memory access:

- 1. Before a load is allowed to perform with respect to any other processor, all previous load accesses must be globally performed and all previous store accesses must be performed with respect to all processors.

- 2. Before a store is allowed to perform with respect to any other processor, all previous load accesses must be globally performed and all previous store accesses must be performed with respect to all processors.

Strong Ordering introduces unnecessary processor/cache waiting time and reduces the concurrency.

#### Weak Consistency Model

The weak consistency TSO model developed by Sun Microsystems SPARC architecture is described below. The memory events store and swap are placed in a dedicated store buffer of each processor. Thus the order in which these memory events are performed is the same as the order in which the processor issued them (in program order).

- 1. The memory order corresponds to the order in which the switch is thrown from one processor to another.

- 2. A load by a processor first checks its store buffer to see if it contains a store to the same location. If it does, then the load returns the value of the most recent such store. Otherwise, the load goes directly to memory.

- 3. A swap is placed in the store buffer like a store and it blocks the processor like a load. In other words, swap blocks until the store buffer is empty and then proceeds to the memory.

## A TSO Formal Specification

- 1. A load access is always returned with the latest store to the same memory location issued by any processor in the system.

- 2. If two stores appear in a particular program order, then they must also appear in the same memory order.

- 3. If a memory operation follows a load in program order, then it must also follow the load in memory order.

- 4. A store operation is atomic with respect to other stores.

- 5. No other store can interleave between the load and store parts of a swap.

- 6. All stores and swaps must eventually terminate.

The weak consistency model may offer better performance than the sequential consistency model at the expense of more complex hardware software support and more programmer awareness of the imposed restrictions.

5 (a) With a neat diagram explain the architecture of connection machine CM2.

The Connection Machine CM-2 produced by Thinking Machines Corporation was a fine-grain MPP computer using thousands of bit-slice PEs in parallel to achieve a peak processing speed of above 10 Gflops.

CO<sub>4</sub>

(10)

L2

#### Program execution paradigm

- 1. The microinstructions are issued from the front end to the backend processing array when data-parallel operations are applied.

- 2. The sequencer breaks down those microinstructions and broadcast them to all data processors in the array.

- 3. Data sets and results could be exchanged between the front-end and the processing array in one of three ways i.e. broadcasting, global combining and scalar memory bus.

#### The Processing Array

- 1. The processing array contained from 4K to 64K bit-slice data processors (or PEs), all of which were controlled by a sequencer.

- 2. All processors could access their memories simultaneously. All processors executed the broadcast instructions in a lockstep manner.

- 3. The processors exchanged data among themselves in parallel through the router,

NEWS grid, or scanning mechanism. from/to Front-end Computer Sequencer Global Result Bus Scalar Memory Bus Instruction Broadcast Bus P Thousands of Processors Memories M Router/NEWS/Scanning VO 1/0 Framebuffer Controller Controller I/O Bus I/O Bus Framebuffer Out

# Processing Node

- 1. A CM2 processing node consists of two processor chips and some memory and floating-point chips.

- 2. The processor chips were paired in each node sharing a group of memory chips. Each processor chip contained 16 processors. The parallel instruction set, called Paris, included nano-instructions for memory load and store, arithmetic and logical, and control of the router, NEWS grid, and hypercube interface, floating point, I/O, and diagnostic operations.

## Hyper-cube Router

- Special hardware was built on each processor chip for data routing among the

processors. The router nodes on all processor chips were wired together to form

a Boolean n-cube. A full configuration of CM-2 had 4096 router nodes on

processor chips interconnected as a 12-dimensional hypercube.

- All 16 processors belonging to the same node were equally capable of sending a

message from one vertex to any other processor at another vertex of the 12cube.

## The NEWS Grid

- 1. The "NEWS" grid was based on the fact that each processor has a north, east, west, and south neighbor in the various grid configurations.

- 2. These flexible interconnections among the processors made it very

efficient to route data on dedicated grid configurations based on the application requirements. Scanning and Spread Mechanism 1. It is used for fast data combining and spreading in the NEWS grid. 2. Scanning operation could simultaneously scan in every row of a grid along a particular dimension for the partial sum of that row, the largest or smallest value, or bitwise OR, AND, or exclusive OR. 3. Spreading could send a value to all other processors across the chips. I/O and Data vault 4. High-speed I/O channels were available from 2 to 16 channels for data and for image I/O operations. 5. Peripheral devices attached to I/O channels included a data vault, CM-HIPPI system, CM-IOP system etc. The data vault was a disk-based mass storage system for storing program files and large data bases. CO4 L2 6 (a) What are the implementation models of SIMD? Explain in detail (10)There are two implementation models for SIMD as given below Distributed-Memory Model 1. A distributed-memory SIMD computer consists of an array of PEs which is controlled by the same array control unit. 2. Program and data are loaded into the control memory through the host computer. 3. An instruction is sent to the control unit for decoding. If it is a scalar or program control operation, it will be directly executed by a scalar processor attached to the control unit. If the decoded instruction is a vector operation, it will be broadcast to all the PEs for parallel execution. Scalar Mass Storage Processor Scalar Instructions Network Control Array Control Memory Host I/O Control Unit (Program and Data) Computer (User) Instr. Vector Instructions Broadcast Bus (Instructions PE<sub>2</sub> PEn and Constants) Data Bus LM<sub>2</sub> LM. LM<sub>n</sub> PE: Processing Element LM: Local Memory Data Routing Network (a) Using distributed local memories (e.g. the Illiac IV) 4. Partitioned data sets are distributed to all the local memories attached to the PEs through a vector data bus.

- 5. The Illiac IV was such an early SIMD machine consisting of 64 PEs with local memories interconnected by an 8\*8 mesh.

- 6. The PEs is interconnected by a data-routing network which performs inter-PE data communications such as shifting, permutation, and other routing operations.

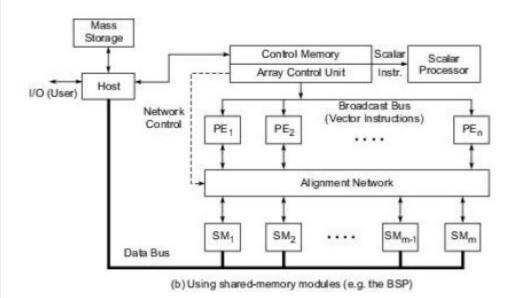

## Shared Memory Model

- 1. All the PEs are connected to a shared memory.

- 2. An alignment network is used as the inter-PE memory communication network. Again this network is controlled by the control unit.

- 3. The Burroughs Scientific Processor (BSP) had adopted this architecture, with n = 16 PEs updating m = 17 shared-memory modules through a 16\*17 alignment network.

- 4. The alignment network must be properly set to avoid access conflicts.

7(a) Explain the Concurrent OOP, Actor Model and Parallelism in COOP.

## Object-Oriented Model

- 1. It is parallel programming model.

- In this model, objects are dynamically created and manipulated. Processing is performed by sending and receiving messages among objects.

L2

CO5

(10)

3. Concurrent programming models are built up from low-level objects such as processes and semaphores and high level objects like monitors and program modules.

#### Concurrent OOP

The Concurrent Object Oriented programming is popular due to three reasons given below

- 1. Due to increased use of interacting processes.

- 2. For resource sharing and distributed problem solving.

3. For providing supercomputing power at a fraction of the traditional cost.

Objects are program entities which encapsulate data and operations into single computational units. The development of concurrent object-oriented programming (COOP) provides an alternative model for concurrent computing on multiprocessors or on multicomputer. Various object models differ in the internal behavior of objects and in how they interact with each other.

## An Actor Model

It is developed at MIT as one framework for COOP.

Actors are self-contained, interactive, independent components of a computing system that communicate by asynchronous message passing. Basic actor primitives include:

- 1. Create: Creating an actor from a behavior description and a set of parameters.

- 2. Send-to: Sending a message to another actor.

- 3. Become: An actor replacing its own behavior by a new behavior.

Each message may cause an object (actor) to modify its state, create new objects, and send new messages. The actor model is particularly suitable for multicomputer implementations.

#### Parallelism in COOP

Two common patterns of parallelism have been found in the practice of COOP.

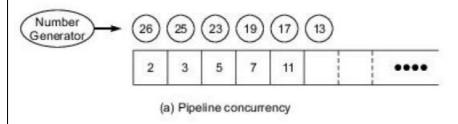

## 1. Pipeline Concurrency

First, pipeline concurrency involves the overlapped enumeration of successive solutions and concurrent testing of the solutions as they emerge from an evaluation pipeline.

Example: Prime number generation pipeline. Numbers enter from the left end and is eliminated if it is divisible by the prime number tested at a pipeline stage. All the numbers being forwarded to the right of a pipeline stage are those indivisible by all the prime numbers tested on the left of that stage.

## 2. Divide-and-conquer concurrency

It involves the concurrent elaboration of different subprograms and the combining of their solutions to produce a solution to the overall problem.

Example: Multiplication of a list of numbers [10, 7, -2, 3, 4, -11, -3] using a divide and- conquer approach. The numbers are re-presented as leaves of a tree. The problem can be recursively subdivided into sub problems of multiplying two

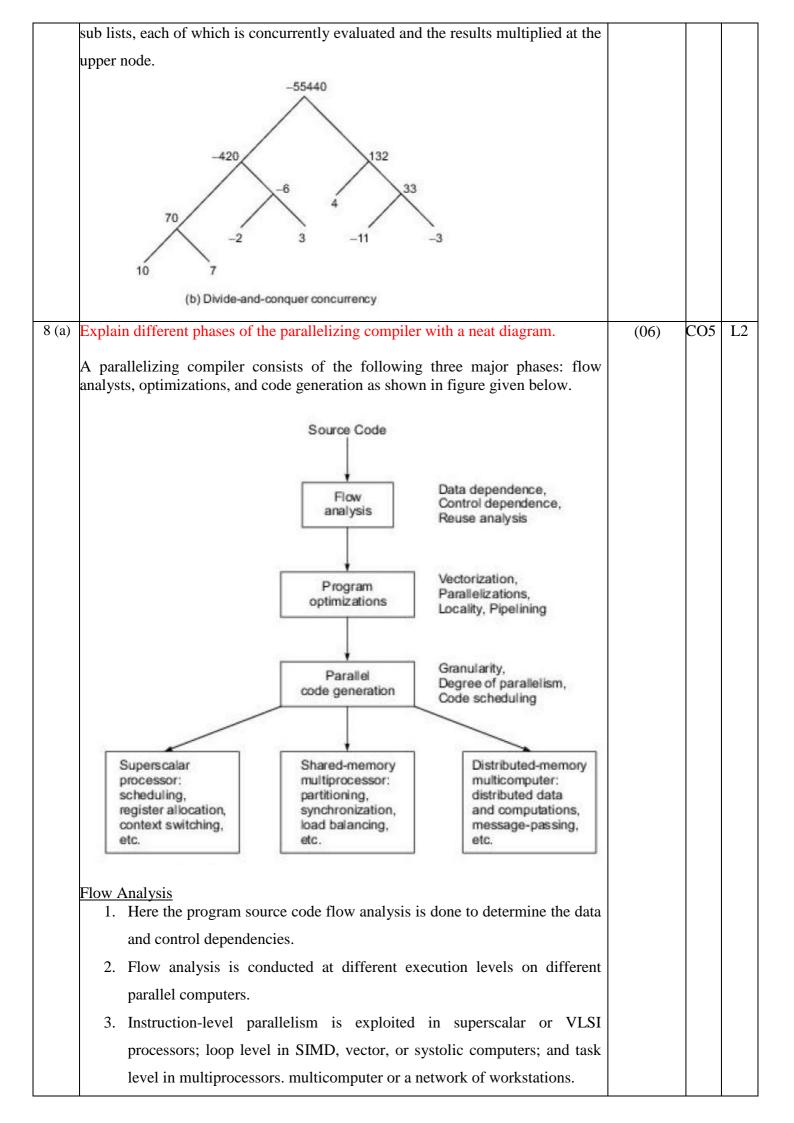

4. The flow analysis must also reveal code/data reuse and memory-access patterns.

# Program Optimization

- The transformation of the program can be done at loop level, locality level or perfecting level with the ultimate goal of reaching global optimization. The optimization often transforms a code into "better" form in the same representation language. These transformations should be machine-independent.

- 2. The ultimate goal of program optimization is to maximize the speed of code execution, minimization of code length and of memory accesses and the exploitation of parallelism in programs.

- 3. Both local and global optimizations are needed in most programs. Sometimes the optimization should be conducted at the algorithmic level and must involve the programmer.

- 4. Various optimization techniques include vectorization using pipelined hardware, parallelization using multiple processors, elimination of unnecessary branches or common expressions.

## Parallel Code Generation

- 1. Code generation usually involves transformation from one representation to another, called an Intermediate form.

- 2. Parallel code generation is difficult in super scalar processor due to register allocation and synchronization overhead when codes are partitioned for multiprocessor execution.

- 3. Compiler directives can be used to help generate parallel code when automated code generation cannot be implemented easily.

- 4. Two well-known exploratory optimizing compilers were developed over mid 1980: one was Parafrase at the University of Illinois, and the other was the PFC (Parallel FORTRAN Converter) at Rice University.

## Parafrase and Parafrase 2

- It transforms sequential Fortran 77 programs into forms suitable for vectorization or parallelization. Parafrase contains more than 100 program transformations which are encoded as passes.

- 2. The output of Parafrase is the converted concurrent program.

- 3. Different programs use different pass list and thus go through different sequences of transformations. The pass lists can be optimized for specific machine architectures and specific program constructs. Parafrase 2 was developed for handling programs written in C and Pascal, in addition to convening FORTRAN codes.

| The PI | FC and ParaScope                                                                                      |      |     |    |

|--------|-------------------------------------------------------------------------------------------------------|------|-----|----|

| 4.     | It translated FORTRAN 77 code into FORTRAN 90 code.                                                   |      |     |    |

| 5.     | The PFC package was also extended to PFC+ for parallel code generation                                |      |     |    |

|        | on shared-memory multiprocessors and also it supports the ParaScope                                   |      |     |    |

|        | programming environment.                                                                              |      |     |    |

|        |                                                                                                       |      |     |    |

| _      | n the concept of Full Map Directories with neat diagram for Directory protocol.                       | (04) | CO4 | L2 |

| Full-M | IAP Directories                                                                                       |      |     |    |

| 1.     | For each shared data object the directory entry contains one bit per                                  |      |     |    |

|        | processor which represents if copy of block is present or absent in the                               |      |     |    |

|        | corresponding processor's cache and a dirty bit/clean bit field.                                      |      |     |    |

| 2.     | If the dirty bit is set, then one and only one processor's bit is set and that                        |      |     |    |

|        | processor can write into the block.                                                                   |      |     |    |

| 3.     | The figure given below illustrates three different states of a full-map                               |      |     |    |

|        | directory.                                                                                            |      |     |    |

|        | Shared memory X: C Data  Shared memory X: C Data                                                      |      |     |    |

|        | Cache Cache Cache Cache X: Data Cache X: Data Cache X: Data Read X Read X Read X Read X Read X Read X |      |     |    |

|        | X: D Data                                                                                             |      |     |    |

|        | Cache Cache X: Data  (a) Three states of a full-map directory                                         |      |     |    |

| 4.     | In the first state, location X is missing in all of the caches in the system.                         |      |     |    |

|        | The second state results from three caches (Cl, C2, and C3) requesting                                |      |     |    |

|        | copies of location X. Three pointers [processor bits] are set in the entry to                         |      |     |    |

|        | indicate the caches that have copies of the block of data. In the first two                           |      |     |    |

|        | states, the dirty bit on the left side of the directory entry is set to clean                         |      |     |    |

|        | (C) indicating that no processor has permission to write to the block of                              |      |     |    |

|        | data. The third state results from cache C3 requesting write permission                               |      |     |    |

|        | for the block. In the final state, the dirty bit is set to dirty {D}, and there                       |      |     |    |

|        | is a single pointer to the block of data in cache C3.                                                 |      |     |    |

- (1) Cache C3 detects that the block containing location X is valid but that the processor does not have permission to write to the block, indicated by the block's write-permission bit in the cache.

- (2) Cache C3 issues a write request to the memory module containing location X and stalls processor P3.

- (3) The memory module issues invalidate requests to caches Cl and C2.

- (4) Caches Cl and C2 receive the invalidate requests, set the appropriate bit to indicate that the block containing location X is invalid, and send acknowledgments back to the memory module.

- (5) The memory module receives the acknowledgments, sets the dirty bit, clears the pointers to caches Cl and C2, and sends write permission to cache C3.

- (6) Cache C3 receives the write permission message, updates the state in the cache, and reactivates processor P3.

# Disadvantage

It is not scalable

Lot of memory overhead due to N pointers for each directory entry. Thus, the total memory overhead scales as the square of the number of processors  $O(N^2)$ .