| USN |  |

|-----|--|

|-----|--|

## Internal Assesment Test - II

| Sub:  | DIGITAL SYSTI                                                                                                                                                                                      | EM DESIGN | N         |                    |          |            |          | Code:   | 18El | E35 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|--------------------|----------|------------|----------|---------|------|-----|

| Date: | 15/10/2019                                                                                                                                                                                         | Duration: | 90 mins   | Max Marks:         | 50       | Sem:       | 3rd      | Branch: | EE   | E   |

|       |                                                                                                                                                                                                    | A         | nswer Any | FIVE FULL (        | Question | ns         |          |         |      |     |

|       |                                                                                                                                                                                                    |           |           |                    |          |            |          | Marks   | OI   | BE. |

|       |                                                                                                                                                                                                    |           |           |                    |          |            |          |         | CO   | RBT |

|       | (a) Describe the working (b) Distinguish between                                                                                                                                                   |           |           | with its truth tab | le.      |            |          | 7+3=10  | CO3  | L2  |

|       | (a) With a neat logic diagram describe the working of D flip-flop with truth table and derive the Characteristics Equation.  (b) Distinguish between combinational circuit and sequential circuit. |           |           |                    |          |            | 6+4=10   | CO3     | L2   |     |

|       | Explain the working of Master slave JK Flip-flop with waveforms and functional table (truth table) and show how the race around is overcome.                                                       |           |           |                    |          |            | CO3      | L4      |      |     |

|       | <ul><li>(a) Analyze the role of SR Flip-flop in switch debouncer circuit.</li><li>(b) Compare between Synchronous and Asynchronous sequential circuit with valid points.</li></ul>                 |           |           |                    |          | 7+3=10     | CO3      | L4      |      |     |

|       | (a) Illustrate the signifitring triggering. (b) Complete the output initial condition as 0.  CLK  S  1  R  0                                                                                       |           |           |                    |          |            |          |         | CO3  | L3  |

|       | Explain the operation<br>Characteristics Equation                                                                                                                                                  |           |           |                    | the Ch   | aracterist | ics tabl | e, 10   | CO3  | L4  |

## Answers:

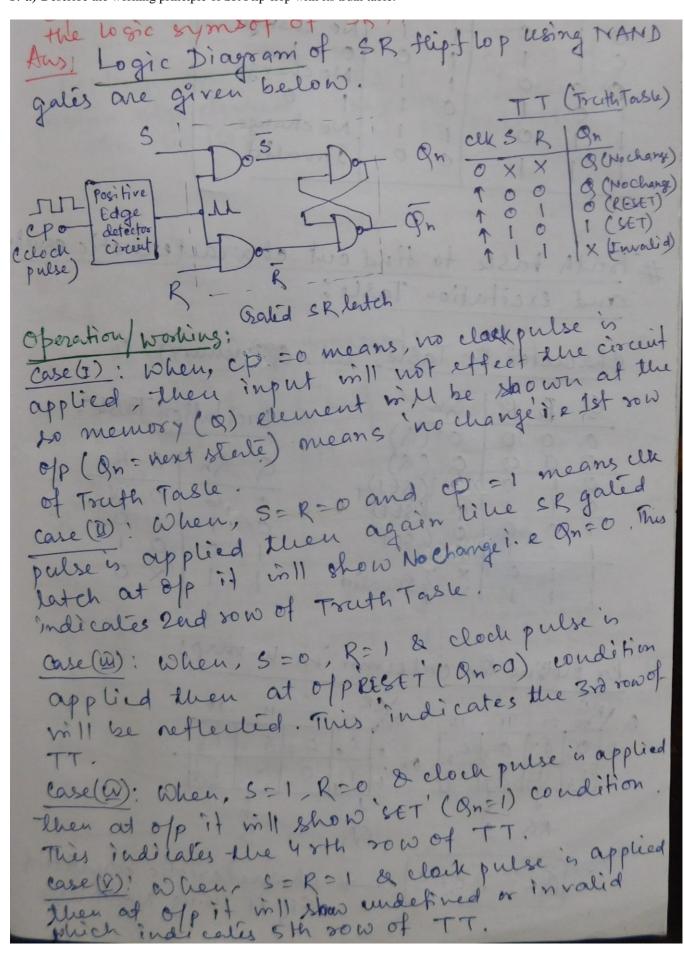

1. a) Describe the working principle of SR Flip-flop with its truth table.

| latch                                                                                                       | flip-flop                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| DIT does not requiere clock                                                                                 | O A flip-flop have                                                                                                             |

| (i) A. latch is on asynch.                                                                                  | (1) A flip flop is a synchro                                                                                                   |

| device i.e when they are enabled the of changes immediately if the i/p changes changes.                     | Here the change on of p<br>is defermined by the transition of clock signal transition of clock signal from low to high or high |

| DIt is level sensitive                                                                                      | DIt is level as well as cage sensitive device.                                                                                 |

| D'These are simples to design as there is no clock signal.                                                  | D'These are more complex<br>to design as they have<br>clock signal and it has<br>to be routed carefully                        |

| latch is faster as they don't have to wait for any clock signal.  The power requerement of a latch is less. | De flép-flops one compara<br>fively slower than latch<br>due to clock signal.<br>De ver requerement<br>of a flép-flop is more  |

| A latch works beiser<br>on the enaste signal.                                                               | based on the clock signal.                                                                                                     |

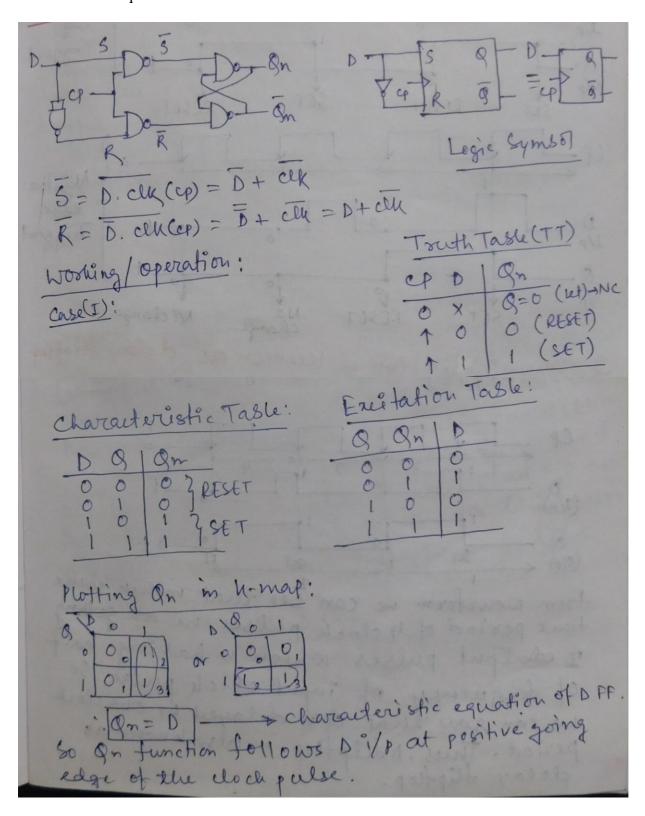

2. (a) With a neat logic diagram describe the working of D flip-flop with truth table and derive the Characteristics Equation.

(b) Distinguish between combinational circuit and sequential circuit.

| Combinational Circuits Sequential Circuits                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------|

| (I) The these circuits, the (I) In these circuits, the                                                                              |

| all times dependent on not only on the present                                                                                      |

|                                                                                                                                     |

| 1 Memory unit is not past history of these                                                                                          |

| required in these cred in Memory unit is required in These are faster in speed in Memory unit is required to store the past of high |

| baca 10 Till a company serior                                                                                                       |

| input and output sittle                                                                                                             |

| galis. C'excells.                                                                                                                   |

|                                                                                                                                     |

| Enere circuits are D'Enere circuits are lay la design.                                                                              |

| (v) Enample! Paralled (1) Example! Series                                                                                           |

| Adder. Adder.                                                                                                                       |

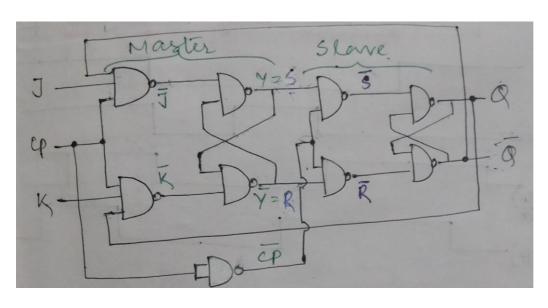

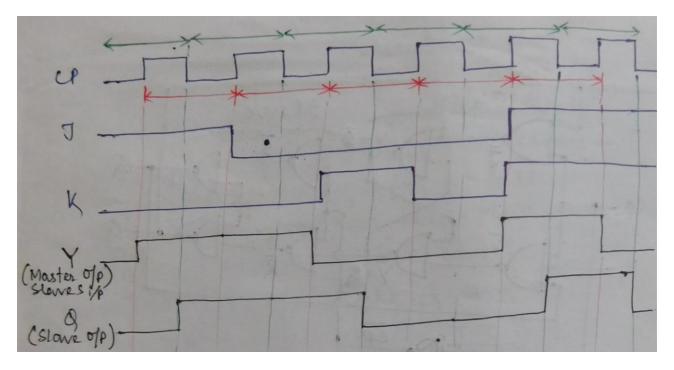

3. Explain the working of Master slave JK Flip-flop with waveforms and functional table (truth table) and show how the race around is overcome.

fig. shows the Jk master slave thep flop, which consists of 2 flip-flops named as one's Master another is slave. slave always follows mastir. Doth the stip flops are positive level toggered but an inverter is connected to the clock input of the slerve flipflop a hich forces et to to geger at the negative level. Therefore, the information present at the Jandk imputs is transmitted to the ofp of master fligtly on the positive doch pulse and it is held there until the negative doch pulse occurs, after which it is allowed to pass this ugh to the output of the slowe of means slowe flip-flop uses the SR input at the negative clock pulse to delermine its ofp state of and of. Case(I): when , J= k=0, the Clk JK | 9n of of master remains Thus the ofp of bleive also (1) II or Q (NO) O (RESET) 1 (SET) remains some at the 10 II 10 & (Toggle) (D) IL -ve clock. Case(1): When, J=0 & 4=1. The master resels on the +ve clock. The high 7 of p of master goes to the Ri/p of the slave. So, at -ve clock slave nesels, again copying the action of the marter. case(w): when, Joh & 400, the master sels on the positive clock. The high Y ofp of mastin drives the 5°1/P of the sleve, so ad - reclark slave sets, copying the action of marster. case(1): When, J= K=1, master toggtes on the positive clock and slave then copies the ofp of master on the negative clock.

In JK flip-flop as we know, at J=K=1 condition, a continuous toggling is happening at the output side which is known as "race around condition". This condition can be avoided by using three methods as

- i) Keeping propagation delay higher than clock period.

- ii) Using of edge triggered clock pulses for the operation.

- iii) Using Master Slave flip-flop.

However, from the above timing diagram it is clearly seen that at J=K=1 condition, there is no chance of toggling at the output as master flip-flop works at positive level triggered clock pulse and slave flip-flop works at negative clock pulse simeltaneously. So by using the master slave flip-flop we can avoid this race around condition at J=K=1 condition.

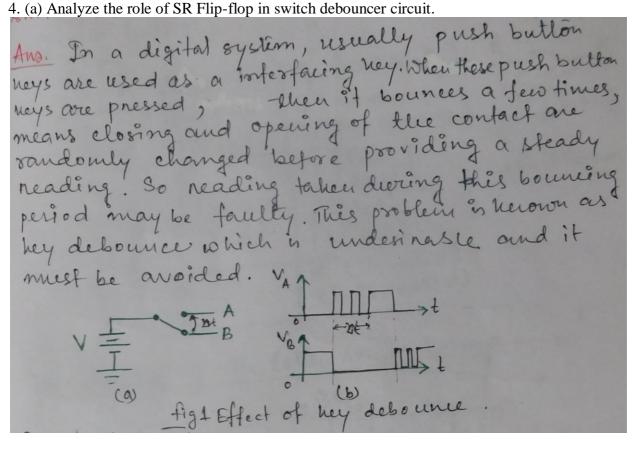

4. (a) Analyze the role of SR Flip-flop in switch debouncer circuit.

One way to avoid key debounce problem is lo use SR Latch. The circult which is used to avoid keybounce with SR latch is called a switch debouncer. Here, Fig 1(a), shows a smitch which is connected to b terminal so, B is I and A is O . when it moves from B to A they during At time period it will bounces and a toggle condition's occurred. So two pull down resistors one conhected across the i/p terminal a of SR latch as shown in hg.2. When key is out position A then 501 and gai mean'v. When transition happens between A to B · Fig: Smitch debouncer of it will take some time (let new), twing that time position A and B both are in high impedance state (means los coursent will flow). Due to these peristors (pull down) these high impedances are prelled down to gero. So cohemerer-lue contact point is in between A and B then 1/p of SR latch mill be Zero which will maintain the steady state of of the latch.

(b) Compare between Synchronous and Asynchronous sequential circuit with valid points.

| Synchrous as Circuits  The these circuits one memory elements one clocked the change in memory element upon memory element upon memory element upon activations of clock signal activations of clock signal speed of clock depends on time delays involeved. | memory elements are memory elements are either unclocked flep flops either unclocked flep flops or time delay elements.  There the change in input signals can affect memory element at memory element at |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D'Easier to design.                                                                                                                                                                                                                                          | 1 More difficult to<br>design.                                                                                                                                                                            |

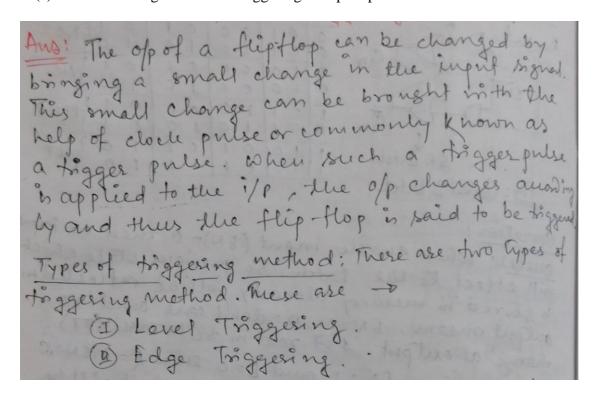

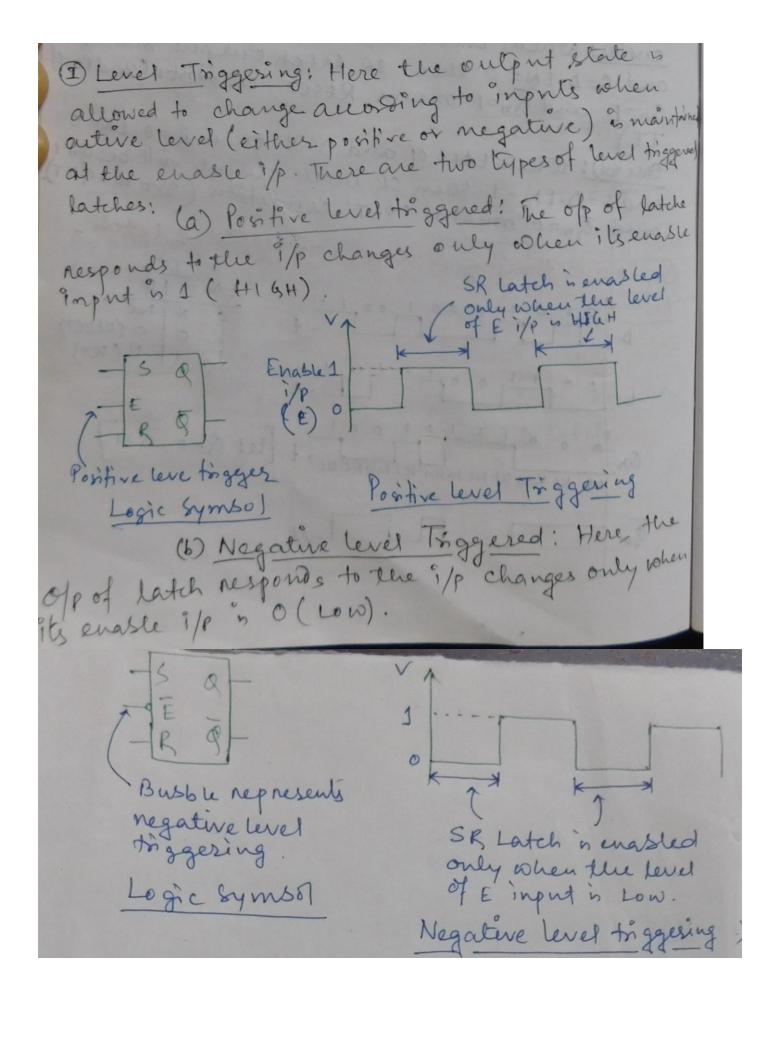

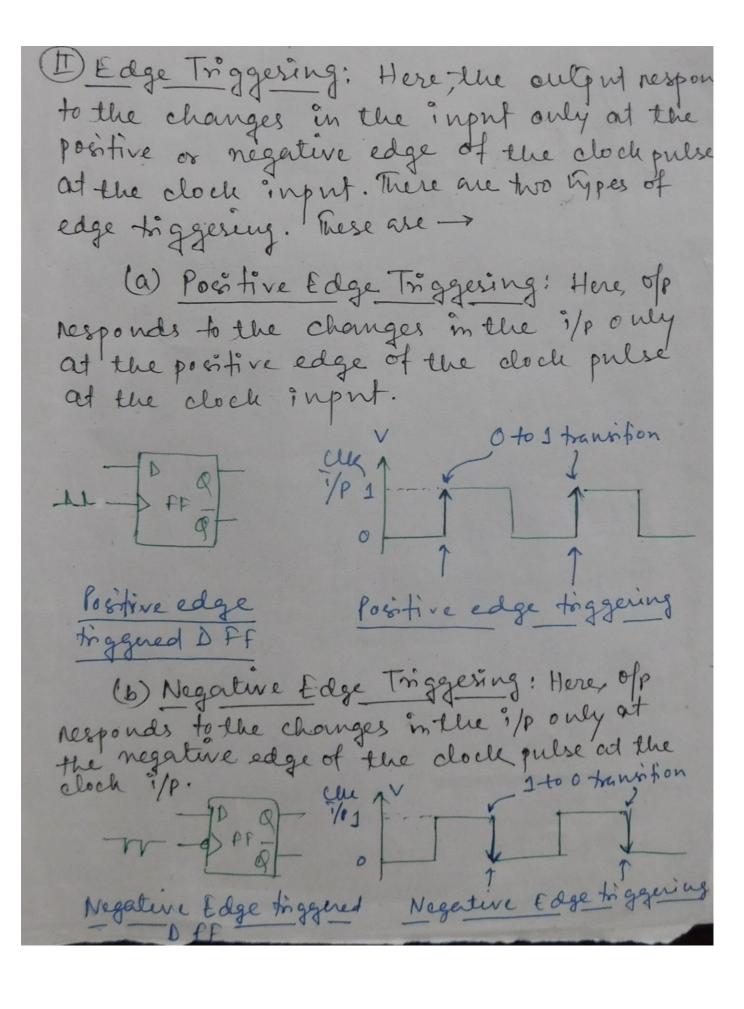

5. (a) Illustrate the significance of triggering in flip-flop and mention various methods for triggering.

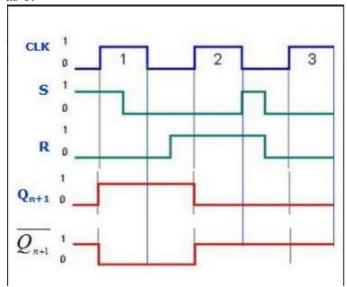

(b) Complete the output waveform for the following combination of SR Flip flop. Consider initial condition as 0.

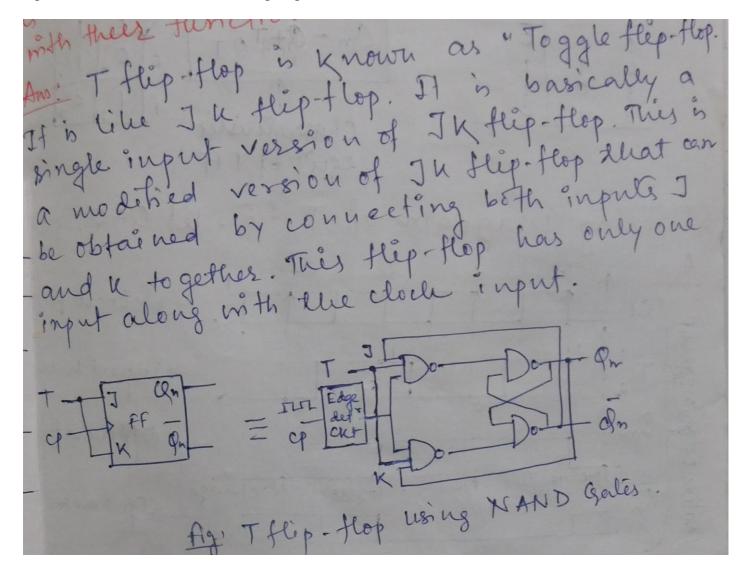

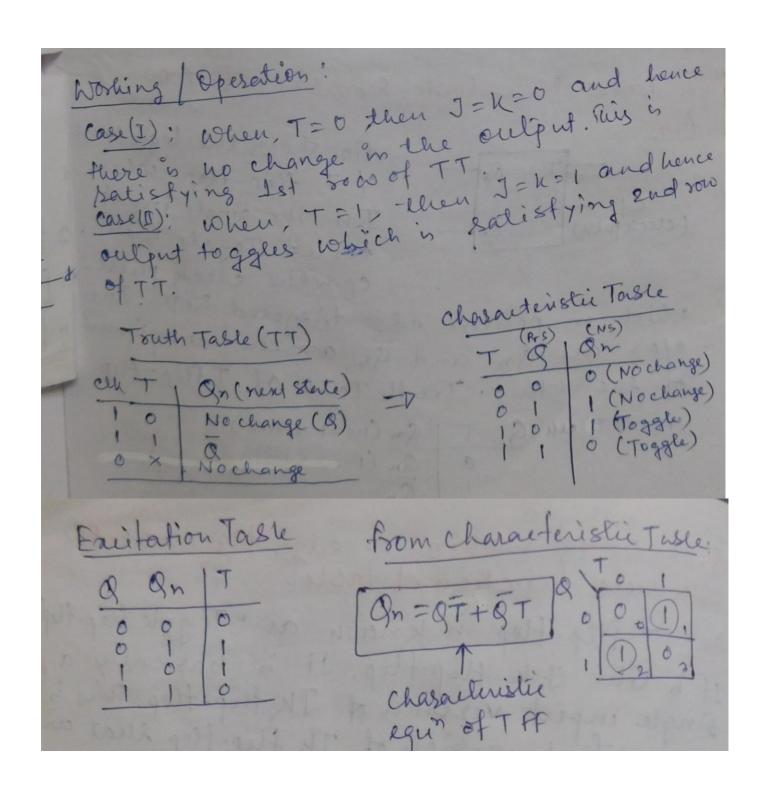

6. Explain the operation of T Flip-flop with truth table. Derive the Characteristics table, Characteristics Equation and Excitation table for T flip flop.