# CMR INSTITUTE OF TECHNOLOGY Solutons of Internal Assessment Test - III Sub: DIGITAL SYSTEM DESIGN Code: 18EE35 Sem: 3rd (A Section) Branch: EEE Faculty Name: Dr. ARIJIT DATTA

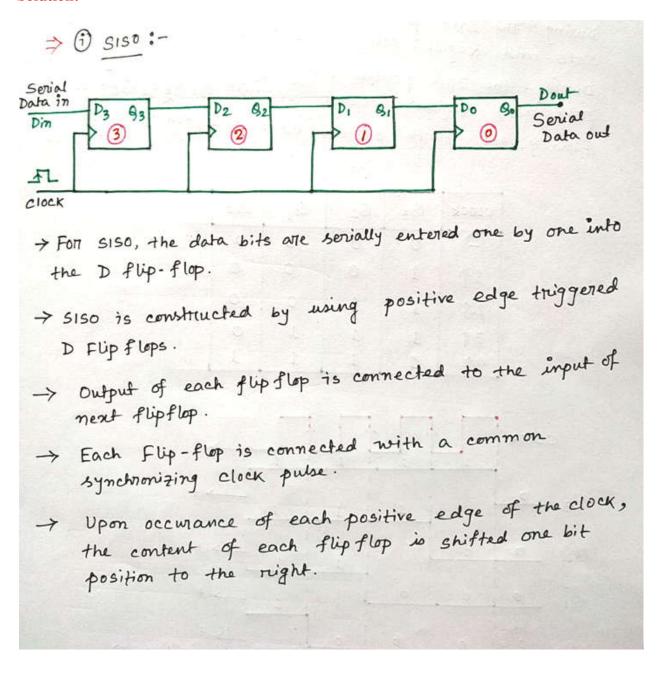

#### 1. Draw the logic diagram for the following modes of Shift Register:

#### SISO, SIPO, PISO, PIPO

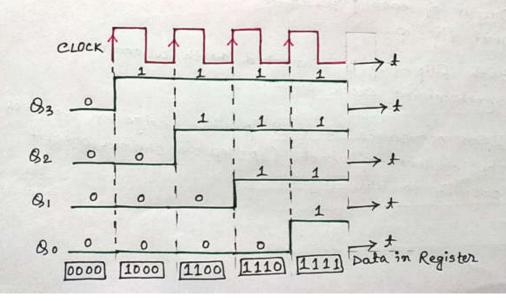

Eg. Let us consider, immittal register is cleaned. So, . B3B2B1B0 = 0000.

Now, Let us serially data 1111 is applied. When data. 1111 is applied serially, i.e left most 1 is applied as Din. At the arrival of 1st positive edge of clock:—

Din=1, 83828180=1000

During, the 2nd positive edge of clock, the 82 Flipflop sets and Register content becomes. 83 828,80 = 1100.

During, the 3nd positive edge of clock, the 81 Flipflop During, the 3nd positive edge of clock, the 81 Flipflop sets and Register content becomes 83828180 = 1110.

Finally, the fourth positive edge of clock gives 83828,80 = 1111

| CLOCK | Bg | 82 | 8, | 80 |

|-------|----|----|----|----|

| - 4   | 0  | 0  | 0  | 0  |

| 11    | 1  | 0  | 0  | 0  |

| 21    | 1  | 1  | 0  | 0  |

| 3↑    | 1  | 1  | 1  | 0  |

| 41    | 1  | 1  | 1  | 1  |

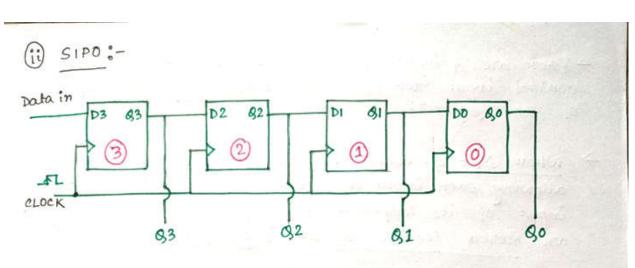

In this case, the data bits are entered into the Register in the same manner as discussed for the case of SISO. But the outputs are collected in parallel. Once the data are storted, each bit appears on its nespective output line and all the bits are available simultaneously.

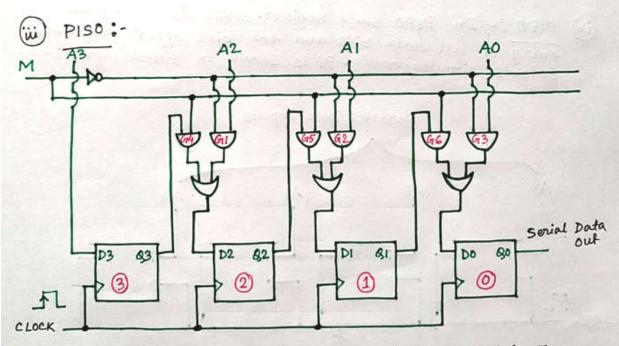

In this type, the bits are entered in parallel. The above Figure shows a 4 bit parallel in serial out shift negister.

P. T. 0

- → There are 4 input lines A3, A2, A1, A0. M is the control input which decides shift on loading operation of the Register.

- → When M = 0, Grates G1, G2 and G3 are enabled allowing each input data bit to be applied to D input of its respective Flipflop. Thus all four bits are stored/loaded to the flipflops.

- → when M=1, gates G1, G2 and G3 one disabled and gates G4, G5 and G6 one enabled. This allows the data bits to shift right from one stage to the next. This corresponds to shifting of data.

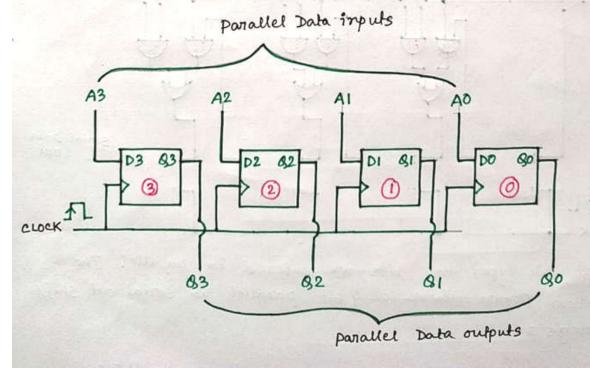

- (iv) PIPO: In PIPO shift negister, there is simultaneous entry of all data bits and the bits appear on parallel outputs simultaneously. 9t is shown in below figure: -

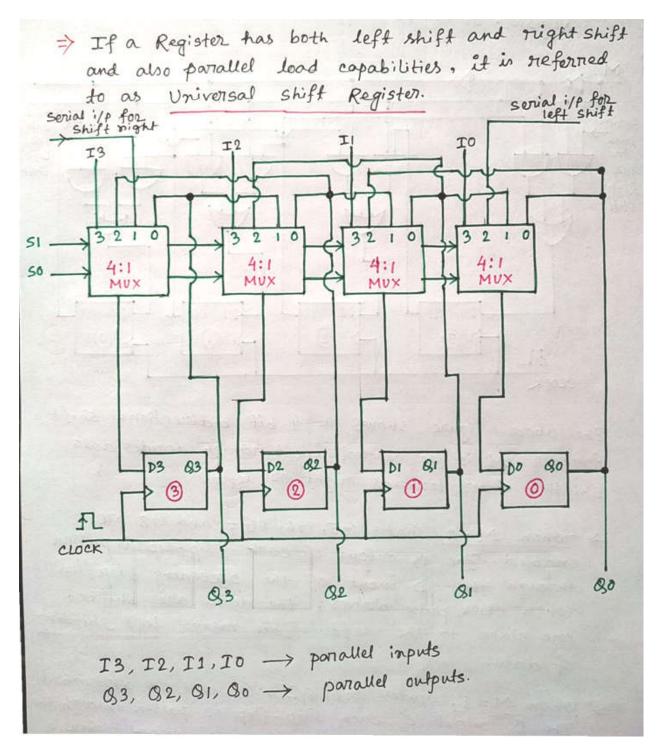

### 2. With neat logic diagram explain the operation of Universal shift register with Mode control table.

→ 9+ consists of 4 flipflops and 4 Multiplexers. The four Multiplexers have two common select inputs 51 and So. and they select appropriate input for D flip-flop. The below table shows the negister operation depending on the select lines of multiplexer.

| Register<br>Operation | control | Mode |

|-----------------------|---------|------|

| Operation             | So      | SI   |

| No change             | 0       | 0    |

| Shift Right           | 1       | ٥    |

| Shift Left            | O       | 1    |

| parallel Load         | 1       | 1    |

> When \$150 = 00, input 0 is selected and the present value of the negister is applied to the D inputs of the flip-flops. This tresults no change in Register value.

> when SISO = 01, input 1 is selected and circuit connections are such that it operates as a right

shift Register.

→ When SISO = 10, input 2 is selected and circuit connections are such that it operates as a left shift Register.

→ Finally when 5.50 = 11, the binary information on the parallel input lines is transferred into the negister simultaneously and it is a parallel load operation.

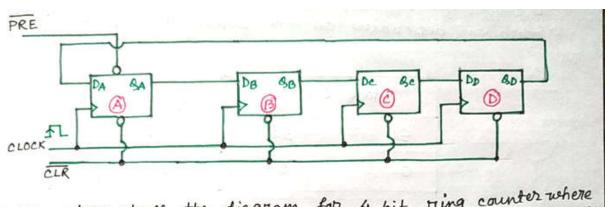

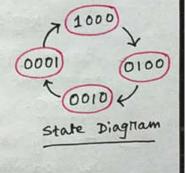

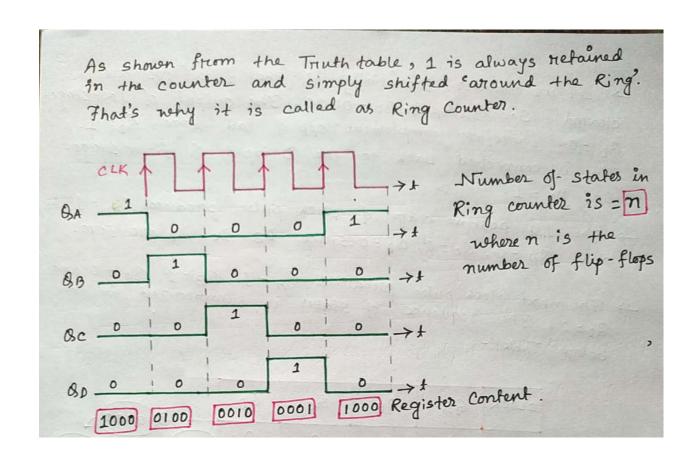

## 3. Analyze the operation of Ring Counter (MOD-4 or 4 bit) with logic diagram, truth table, timing diagram and state diagram.

- > The above shows the diagnam for 4 bit ring counter where g output of each stage is connected D input of next flip-flop and the output of last stage is fed back to the input of first stage.

- → PRE makes the output of first stage as 1 and the nemaining outputs are made 0 by CLR. Let us consider innitially BABBBC BD = 1000.

- → The 1st clock pulse produces BB = 1 and the remaining outputs are 0. According to the clock pulses, a sequence of four states are produced which is listed below:—

| CLOCK | GA. | 98 | ge | 90 |

|-------|-----|----|----|----|

| 20    | 1   | 0  | 0  | 0  |

| 11    | 0   | 1  | 0  | 0  |

| 21    | 0   | 0  | 11 | D  |

| 31    | 0   | 0  | 0  | 1  |

| 41    | 1   | 0  | 0  | 0  |

## 4. Design a synchronous counter with counting sequence 0, 2, 3, 6, 5, 1, 0... using D Flipflop.

\* \* flote, we are considering that whenever counter gets an invalid state then it will tresh to innutial value.

On Onti D

| . 0.     | G <sub>B</sub> | g <sub>c</sub> | O Ati | GB+1. | Beti | DA | DB | Dc |

|----------|----------------|----------------|-------|-------|------|----|----|----|

| GA       | 00             |                |       | 1     | 0    | 0  | 1  | 0  |

| 0        | 0              | 0              | 0     | 1     | 0    | 0  | 0  | 0  |

| 0        | 0              | . 1            | 0     | 0     |      | •  | 4  | 1  |

| 0        | 1              | 0              | 0     | 1     | 1    | 0  | 1  | ^  |

| 0        | 1              | 1              | 1     | 1     | 0    | 1  | 1  | 0  |

|          |                |                | 0     | n     | . 0  | 0  | 0  | 4  |

| ivalid 1 | 0              | 0              | U     | 0     | 1    | 0  | 0  | 1  |

| 1        | 0              | 1              | 0     | 0     |      | 1  | 0  | 1  |

| 1        | 1              | 0              | 1     | 0     | 1    | 1  |    | 2  |

| 1        | -              | 1              |       | 0     | 0    | 0  | 0  | 0  |

| nvalid 1 | 1              | 1              | 0     |       |      |    |    |    |

| A & B |    |     |    | 8ABB  |       | - 11 | 10 |

|-------|----|-----|----|-------|-------|------|----|

| 00    | 01 | 11  | 10 | OC 10 | 0 01  | To   | To |

| 0     | 0  | (1) | 0  | 0     | 1 (1) | -    | 0  |

| 0     | 1  | 0   | 0  | 1     | 0 1   | 10   | 0  |

| SASBB + |     | 11 | - 10 |

|---------|-----|----|------|

| 00      | 101 |    | 0    |

| 0 0     | 1   | 1) | 0    |

| 0       | 0   | 0  | (1)  |

Dc = 8B Bc + 8A BB 8c

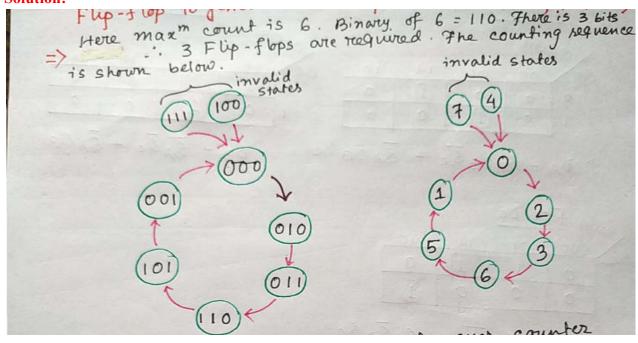

## **5.** Design a Synchronous MOD-6 counter using T flip-flop. Solution:

For designing of counter using clocked T flip-flop we have to follow a similar procedure as that for the design using clocked JK flip-flop.

| Q <sub>n</sub> | Q <sub>n+1</sub> | T |

|----------------|------------------|---|

| 0              | 0                | 0 |

| 0              | 1                | 1 |

| 1 :0           | 0                | 1 |

| 1              | 1                | 0 |

Table 4.10.2

**Step 1**: Find number of flip-flops required to build the counter.

Flip-flops required are :  $2^n \ge N$

Here N = 6 :: n = 3

i.e. three flip flops are required.

Step 2: Write an excitation table for T flip-flop.

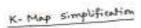

Step 3: Determine the transition table.

| Pre | esent st | tate | N    | ext sta | te   | Flip- | flop in | puts |

|-----|----------|------|------|---------|------|-------|---------|------|

| QA  | QB       | Qc   | QA+1 | QB+1    | Qc+1 | TA    | 76      | 70   |

| 0   | 0        | 0    | 0    | 0       | 1    | 0     | 0       | 1    |

| 0   | 0        | 1    | 0    | 1       | 0    | 0     | 1       | 1    |

| 0   | 1        | 0    | 0    | 1       | 1    | 0     | 0       | 1    |

| 0   | 1        | 1    | 1    | 0       | 0    | 1     | 1       | 1    |

| 1   | 0        | 0    | 1    | 0       | 1    | 0     | 0       | 1    |

| 1   | 0        | 1    | 0    | 0       | 0    | 1     | 0       | 1    |

| 1   | 1        | 0    | ×    | ×       | ×    | ×     | ×       | ×    |

| 4   | 1        | 1    | ×    | ×       | ×    | ×     | ×       | X    |

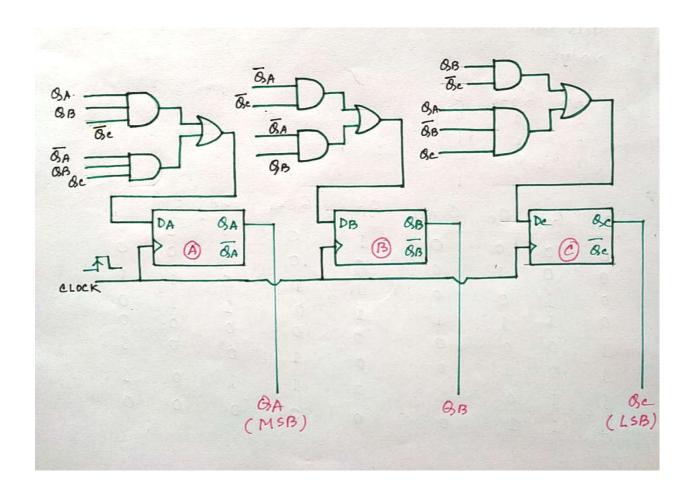

Step 5 : Implement the counter.

Q<sub>A</sub> (MSB), Q<sub>C</sub> (LSB)

Q<sub>A</sub> (MSB), Q<sub>C</sub> (LSB)

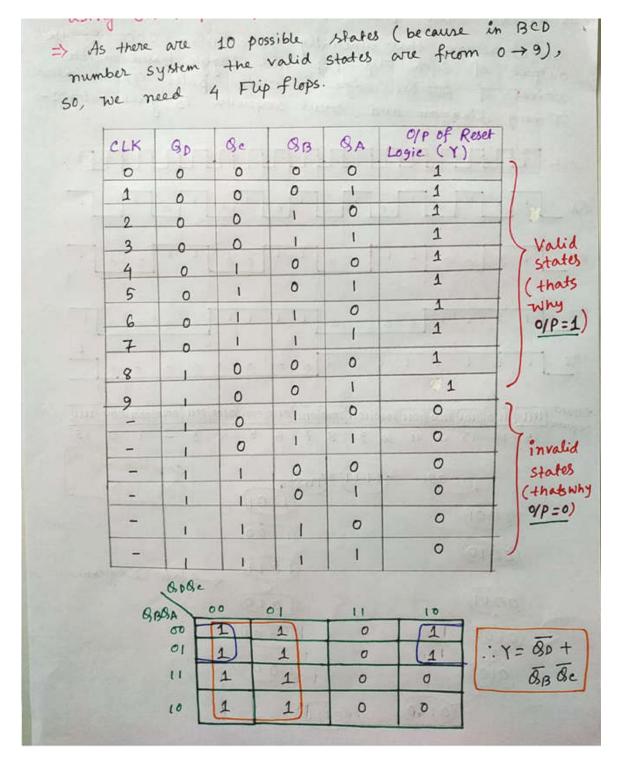

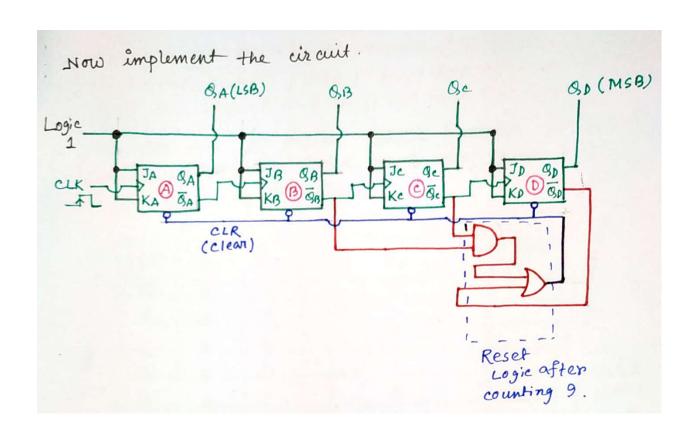

## 6. Design a MOD-10 (BCD) Asynchronous counter with logic diagram, timing diagram and state diagram.

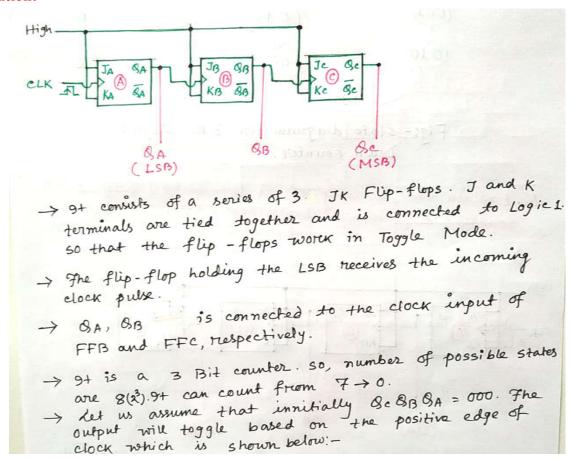

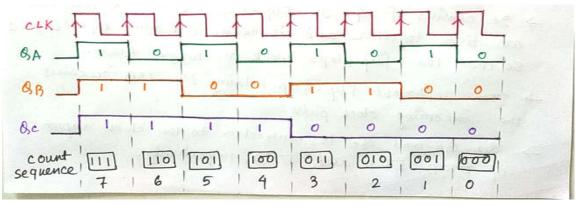

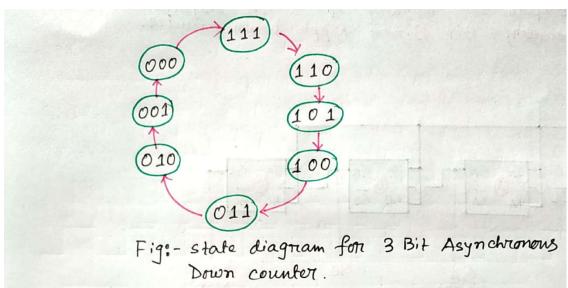

## 7. Explain the working of 3-bit Asynchronous down counter configured using JK flip-flop with logic diagram, timing diagram and state diagram. Solution: