| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

## **Internal Assesment Test - III**

| Sub: | <b>Basic Electronics</b> | Code: 18ELN14 |  |  |  |  |  |  |

|------|--------------------------|---------------|--|--|--|--|--|--|

|      |                          |               |  |  |  |  |  |  |

Marks

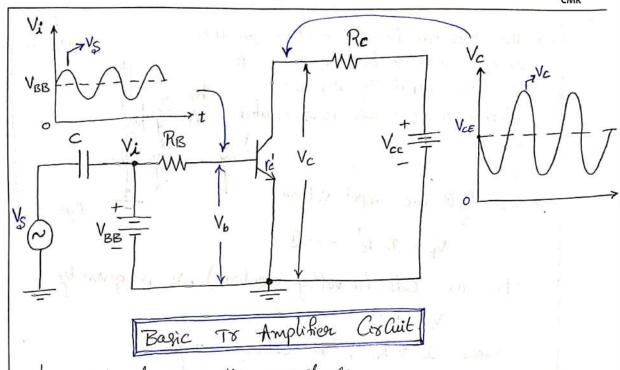

## 1.a Explain the working of transistor as Voltage amplifier

[6]

BJT as an Amplifier: (Voltage Amplifier)

- -> Amplification is the process of linearly increasing the amplitude of an eleactrical signal and is one of the major properties of Transistor.

- -> BJT is biased in Active region (linear region), the EB Junction has low resistance due to forward bias (F.B) and CB Junction has a high resistance due to R.B.

- Transistor amplifies Current because the Collector Current is equal to the base Current multiplied by Current gain is.

i.e Ic = B. Ib

- -> The Base Current is small Compared to the Collector Current & comittee Current, Because of this Collector Current approximately equal to the comittee Current.

- Anna A.C. Voltage Vs., Super imposed on the dc bias vtg VBB by Scapa Citive Coupling as shown in figure.

- re integral ac emitter regisfance

- → An A.c voltage Vs to be amplified is super imposed on the d.c bias voltage VBB by Capacitive Coupling shown above. The d.c bias voltage Vcc is Connected to the Collector through Collector resistor Rc.

- -> The a.c input voltage Vs produces an a.c base Current which results in much larger a.c voltage across Re, which is amplified and inverted version of ac input voltage as shown in above waveform.

- A.C. Equivalent Cut is written to analyze the Voltage gain of amplifier.

- Equivalent CirCuit Can be obtained by making all DC bias Voltage equal to zero i.e.  $V_{BR}=0$  and  $V_{CC}=0$ .

**CO1**

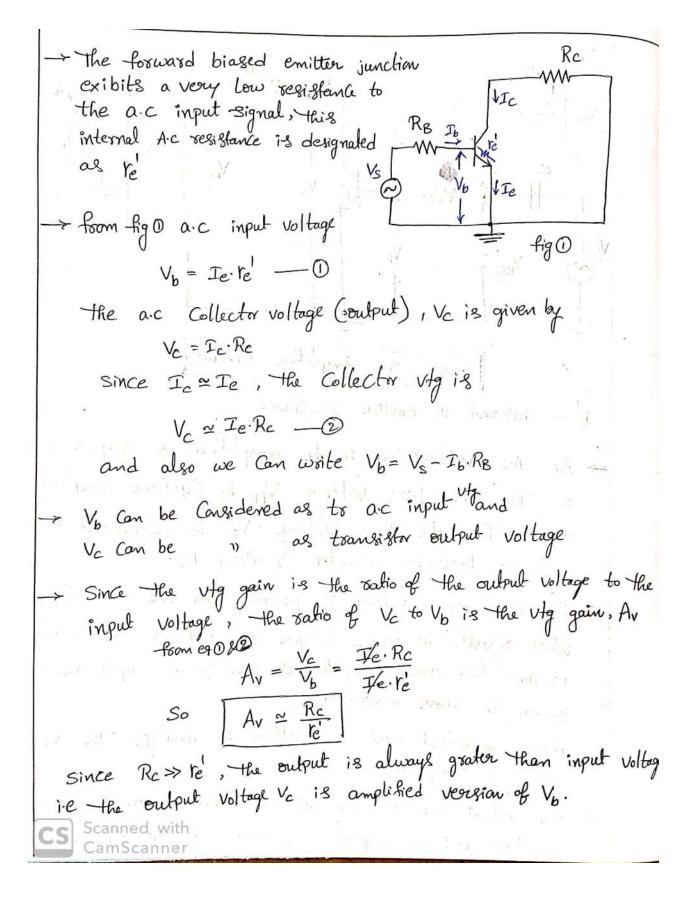

- (a) When  $V_{IN}$  = 0 V, the transistor is in cutoff (acts like an open switch) Therefore,  $V_{CE}$  =  $V_{CC}$  = 10 V

- (b) Since  $V_{CE(sat)}$  is neglected, assume  $V_{CE(sat)} = 0 \text{ V}$

$$I_{C(sat)} = \frac{V_{CC}}{R_{C}} = \frac{10 \text{ V}}{1.0 \text{ k}\Omega} = \frac{18 \text{ mA}}{10 \text{ M}} \text{ MA}$$

$$I_{B(min)} = \frac{I_{C(sat)}}{\beta} = \frac{18 \text{ mA}}{200} = \frac{50 \text{ mA}}{100 \text{ mA}} = \frac{50 \text{ mA}}$$

This is the value of  $I_B$  necessary to drive the transistor to the point of saturation. Any further increase in  $I_B$  will ensure the transistor remains the saturation but there cannot be any further increase in  $I_C$

(c) When the transistor is on,  $V_{BE} \sim 0.7$  V. The voltage across  $R_B$  is  $V_{R_n} = V_{IN} - V_{BE} \simeq 5 \, V - 0.7 \, V = 4.3 \, V$

Calculate the maximum value of  $R_B$  needed to allow a minimum  $I_B$  of 50  $\mu A$  using Ohm's law as follows:

$$R_{B(max)} = \frac{V_{R_n}}{I_{B(min)}} = \frac{4.3 \text{ V}}{50 \text{ }\mu\text{A}} = 860 \text{k}\Omega$$

860 Km

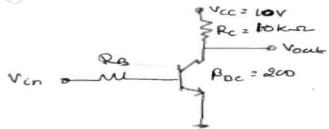

List the types of feedback system. Derive the gain with feedback expression for Voltage series [10] feedback amplifier.

There are four basic types : Voltage Series feedback 2) Voltage-shunt feedback & Current-Series feedback (4) Curent-Shunt feedback. -> Here, voltage defens to connecting the output feedback network. tapping off some outper Seves refers to connecting the feedback signal i the I'mput sighal voltage. - shurt refers to connecting the feedback signal with an input church source eries fledback connection increases the input less While Shimt feedback Connections decreases the input Res Voltage Feedback decreases the output impedam increases the output impedar y dighainput and lower output impedance are desired for Both of these are voltage-Sevier feedback connection. To be the last to the

edback signal by is connected in series with Vo = A Vé = A (Vs-Vf) > Vo(1+AB) = AVs PINOS = A 1+AB -> eqn3 shows first gain with feedback is the amplifier gain reduced by factor (I+AB). - voltage gain & with

3

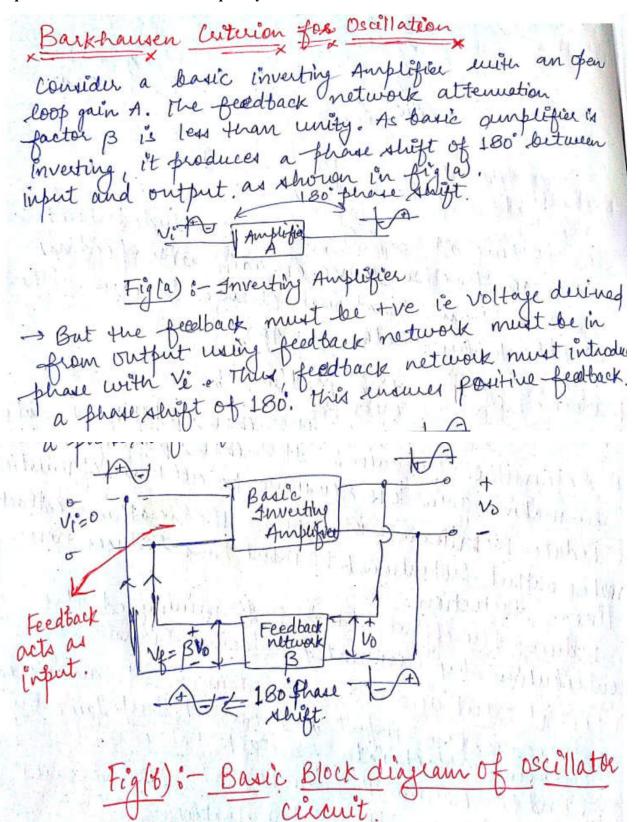

Consider a fictitions voltage input of Amplifier so Vo = AVi - B V& = B Vo - (2) so put ve from eg Vg=BAV For oscillator, we want that feedback should du've the simplifier hence by acts as Vi -> Vg is sufficient to act as u, when 1AB = 1 The two condition are required to work the would as an oscillator are called Barkhau Criterion for Oscillation. Barkhauren Criterion States Hat :- 1 I The total shase shift around a loop, ax signal proceeds from input through amplifier feedback network back to input again, completing a loop is precisely 0° or 360°. & the magnitude of the product of the open loop gain of amplifier (4) and magnitude of the fuedback factor & 12 curity [AB]=1 Satisfying above conditions, circuit works as an oscillated producing sustained oscillations of

Constant frequency and amplitude.

(D (AB)>1 > When total phase shift around a log 1s 0' 0' 360' and (AB)>1, then output os cillate but the oscillations are of growing type. are with constant frequency called as sustained oscillation when total phase she she she she as

4 Explain the construction and working of JFET with drain characteristics and transfer [10] characteristics.

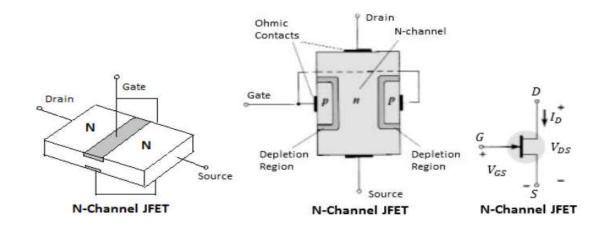

# FABRICATION OF N-CHANNEL JFET: (Construction)

- A narrow bar of N-type semiconductor material is taken. At its middle part, two havily doped ptype regions are formed by diffusion.

- 2. The junction form two P-N diodes or gates. The area between the gates is called a channel.

- 3. One end of the N-type bar is called as source terminal 'S'.

- 4. The other end of the N-type bar is called as drain terminal 'D'.

- 5. The souce and drain terminal may be interchanged.

- When a potential difference is established between source and drain, a current flows from one end to the other end in N-type material.

- 7. This current consists of majority carriers i.e. electrons.

- 8. Following notations for FET should be remembered.

- a) SOURCE: The source 'S' is the terminal through which majority carrier enter the bar.

- b) DRAIN: The drain 'D' is the terminal through which the majority carrier leave the bar.

- c) GATE: These are heavily doped regions which forms two P-N junctions.

- d) CHANNEL: The space between two gates through which majority carriers pass.

#### **OPERATION OF N-CHANNEL FET:**

N-Channel JFET

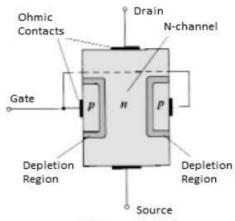

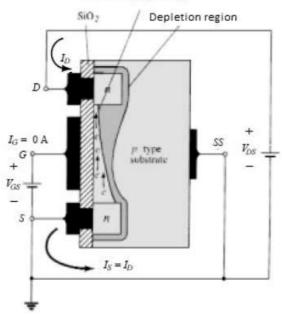

- When no volatges are applied, the depletion regions were uniformly distributed.

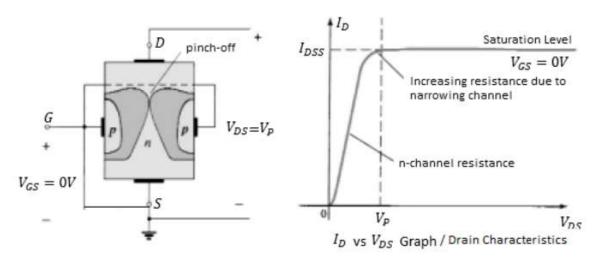

- 2. As a positive voltage is applied across the channel and the gate is connected directly to the source to establish the condition  $V_{GS} = 0V$ . Then the width of the depletion region starts increasing.

- 3. As  $V_{DD}$  is applied , the electrons are drawn to the drain terminal, hence a current will flow in a defined direction.

- 4. The path of charge flow clearly define that  $I_D = I_S$

- 5. The depletion region is wider near the top of both the P-type material.

- Assume a uniform resistance in the N-channel, we can break down the resistance into some division.

- The upper region of the P-type material will be reverse biased by 1.5V comparision with the lower region.

- We know from the diode operation, the greater the applied reverse bias, the wider is the depletion region. Hence the depletion region is shown like this.

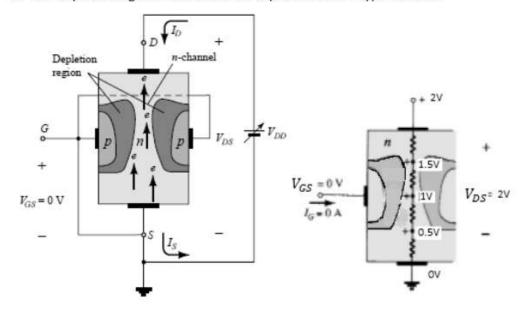

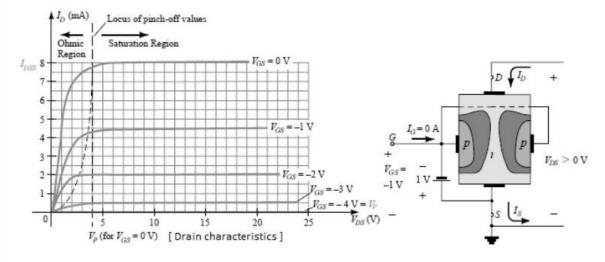

- 9. As  $V_{DS}$  increases and approaches a level referred as  $V_p$ , the depletion region will widen, causing a reduction in channel width. The reduced path of conduction causes the resistance to increase.

- 10. When two depletion region touch the condition is referred to as pinch-off.

- 11. The level of  $V_{DS}$  that establishes this condition is known as pinch-off voltage and denoted as  $V_P$

- 12. In actuallity pinch-off suggests, the current  $I_D$  is pinched off and drop to 0V, but in reality a very small channel still exists, with a very high current density. Hence the  $I_D$  doesn't drop at pinch-off but maintains the saturation level.

- 13.  $I_{DSS}$  is the maximum drain current for a JFET and is defined by the condition  $V_{GS}=0V$  and  $V_{DS}\geq |V_P|$

- 14. The voltage from gate to source  $V_{GS}$  is the controlling voltage of JFET. The reason to apply –ve bias  $V_{GS}$  is to establish depletion region similar to those obtained with  $V_{GS}=0V$  but at lower level of  $V_{DS}$ . Hence saturation level can be achieved at lower  $V_{DS}$ .

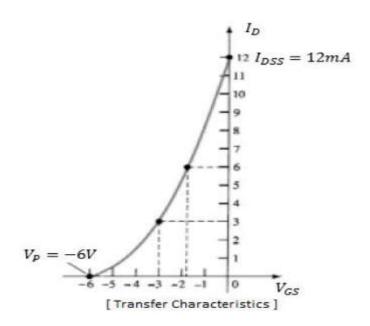

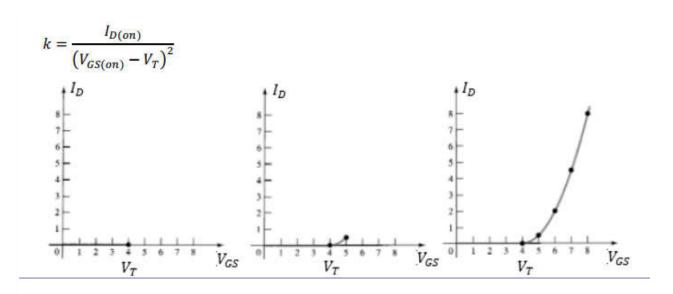

## TRANSFER CHARACTERISTICS:

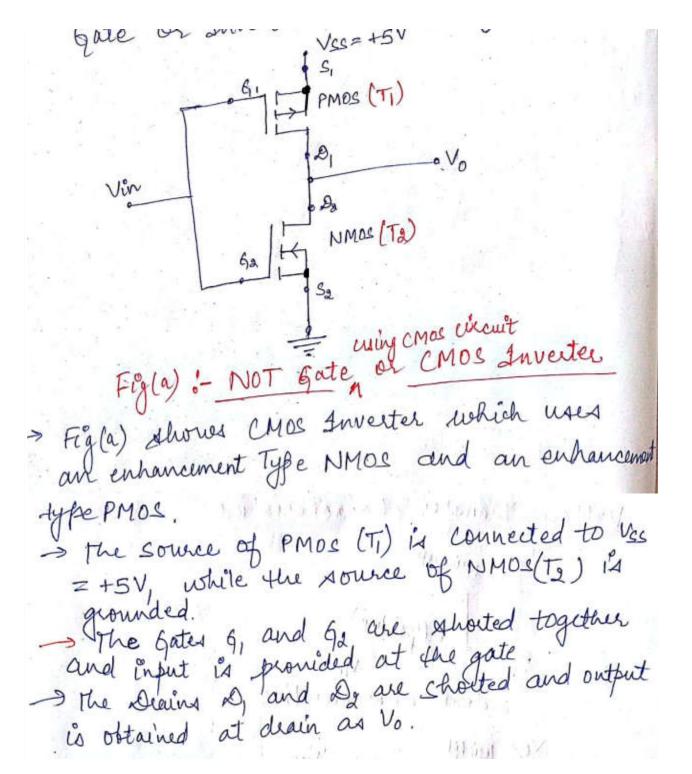

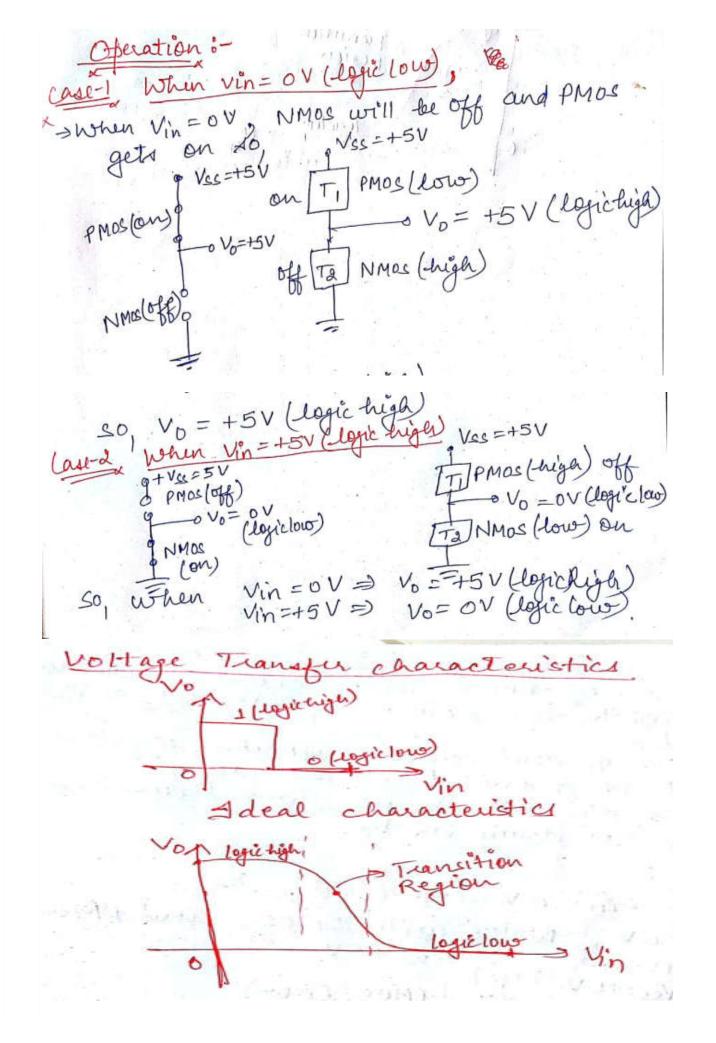

5(a) Explain the working of CMOS Inverter with relevant circuit.

-> CMOS is Complementary Metal Oxide Semiconductor which is a technology used for constructing integrity.

Chautt.

-> CMOS circuity has took advantages:

(1) Low static former consumption.

(1) High Noise Immunity.

-> CMOS circuits use a combination of ptype and N

Type Mosfet's to implement logic gates and other digital Circuits.

CMOS circuit to can be used to implement Not cmos circuit to can be used to implement Not cmos circuit to can be used to implement Not cmos circuit to can be used to implement Not cmos circuit to can be used to implement Not cmos circuit to can be used to implement Not cmos circuit to can be used to implement Not cmos circuit to can be used to implement Not complement of the construction of the cons

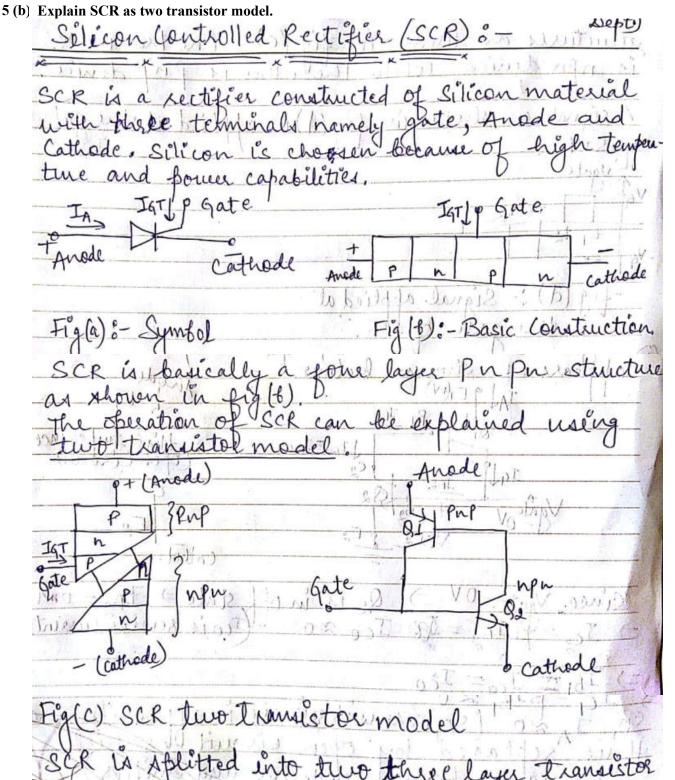

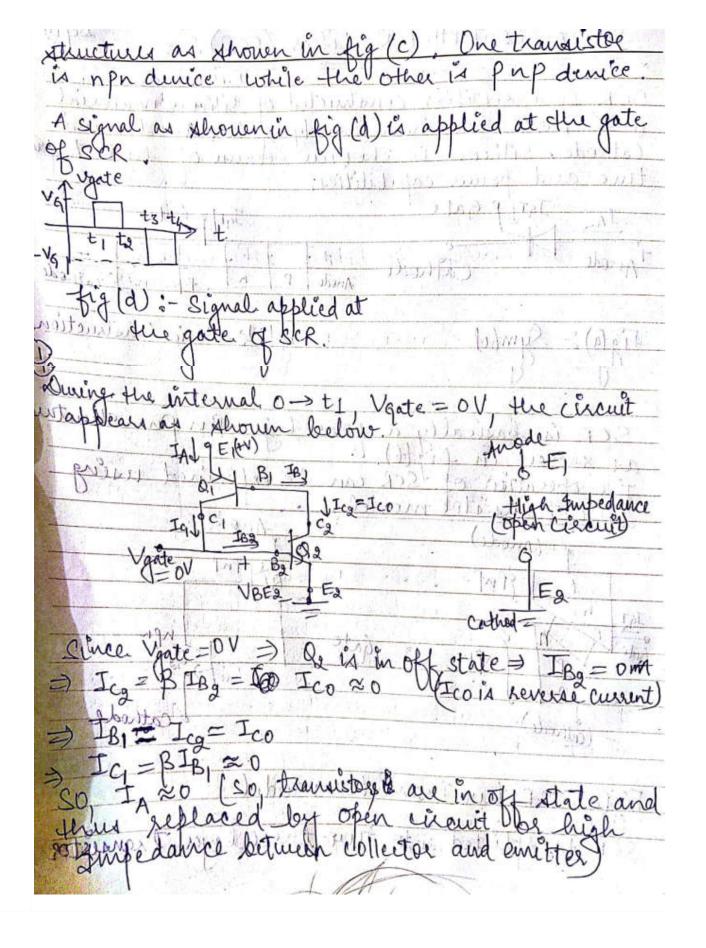

voltais as turns on and their there is Icy = BIBy in the circuit ramistos Q, curent of toposion to latholde resistance | RSCR = large RSCR in very Short liment the gate signal thus negative 13 Natural commutation or Anade Current Inte Forced - Commutation Technique

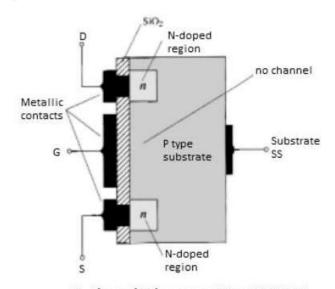

Explain the construction and working of n channel enhancement type MOSFET with relevant drain characteristics and transfer characteristics.

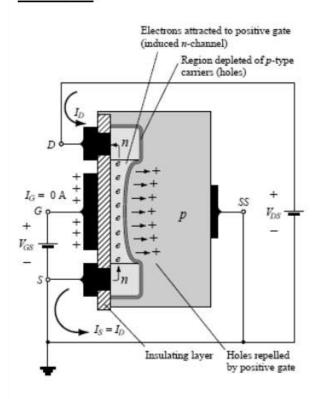

## Construction of N-channel Enhancement type MOSFET:

The construction of n-channel enhancement type MOSFET is similar to the construction of depletion type MOSFET. Here the channel between the two n-doped regions is absent. This is the primary difference between the construction of depletion type and enhancement type MOSFET.

N- Channel Enhancement Type MOSFET

#### OPERATION:

- 1. Although some positive  $V_{DS}$  is applied, as the  $V_{GS}=0V$ , no channel exists hence the current through the device is 0A i.e.  $I_D=I_S=0A$

- 2. As some positive voltage  $V_{GS}$  is applied to the gate terminal, the positive potential at the gate will pressure the holes in the p-substrate. Electron in the p substrate will be attracted to the positive gate and accumulated in the region near to the surface of  $SiO_2$  layer.

- As V<sub>GS</sub> increases in magnitude, the concentration of electron near SiO<sub>2</sub>surface increases.

- V<sub>GS</sub> has to be increased until the induced N-type region can support the flow of current.

- 5. The level of  $V_{GS}$  that results in the significant increase in drain current is called the threshold voltage and represented as  $V_T$  or  $V_{GS(Th)}$

- 6. The current is nonexistent with  $V_{GS} = 0V$  and enhanced by the application of positive gate to source voltage, this type of MOSFET is called as enhancement type MOSFET.

- Both depletion and enhancement type MOSFET have enhancement type region.

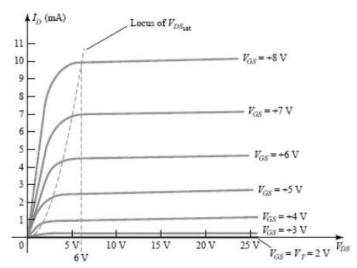

- 8. If we keep  $V_{GS}$  as constant and increase the  $V_{DS}$ then the drain current will increase and reach the saturation level.

Applying KVL to the terminal

$$V_{DG} = V_{DS} - V_{GS}$$

Let  $V_{GS} = 8V$  and  $V_{DS} = 2$  to 5V (i.e. increasing from 2 to 5V)

$V_{DG}$  drops from -6V to -3V

This reduction in gate to drain voltage will reduce the attractive force for free carriers, causes reduction in channel width.

- The channel will be reduced to the point of pinch off and saturation condition will be established.

- 11. But any further increase in  $V_{DS}$  at the fixed value of  $V_{GS}$  will not affect the saturation level of  $I_D$  until breakdown condition occurs.

$$V_{DS(Sat)} = V_{GS} - V_T$$

- 12. For fixed  $V_T$  ,higher the level of  $V_{GS}$  the greater will be the saturation level of  $V_{DS}$

- 13. For  $V_{GS}$  less than the threshold voltage, the drain current of an enhancement type MOSFET is 0mA.

- 14. As  $V_{GS}$  increases from  $V_T$ , the resulting saturation level for  $I_D$  also increases.

- 15. For  $V_{GS} > V_T$ , the drain current is related to the applied gate to source voltage by the following relationship.

$$I_D = k(V_{GS} - V_T)^2$$

Where k = constant and it is a function of the construction of the device

7(a) For a N-channel JFET if  $I_{DSS} = 8mA \& V_P = V_{GS(off)} = -5V$ , calculate  $I_D$  at  $V_{GS} = -3 V$  and  $V_{GS}$  at  $I_D = 3 V$ [5] mA.

$$\widehat{J}_{Q} \qquad \widehat{I}_{D} = \widehat{I}_{DSS} \left[ 1 - \frac{V_{GS}}{V_{P}} \right]^{2}$$

$$\widehat{I}_{D} = 1.28 \text{ mA}$$

$$V_{QS} = V_{P} \left( 1 - \sqrt{\frac{I_{D}}{I_{DSS}}} \right) = -1.938V$$

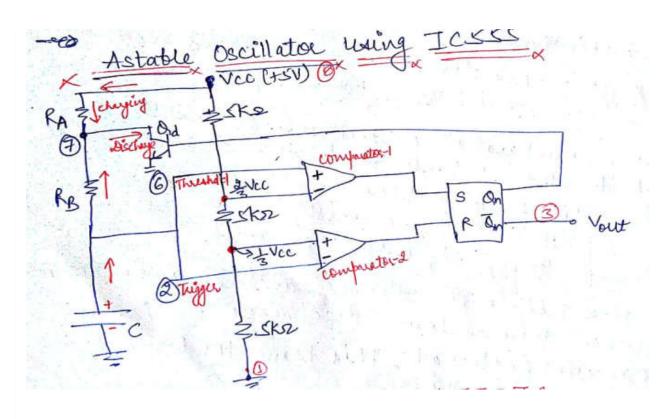

7(b) Explain the working of 555 Timer as a stable oscillator with necessary equations.

TC 555 Timer :- It is a versatile analog-digital thegeted circuit. Entire license is housed in an 8-pin facky Pin diagram of IC SSS :- It has 8 pins.

[5]

Ground []° 8] + VCC

Trigger [2 IC 7] Dischaye

Output [3 555 6] Threshold

Reset [4 5] Control voltage.

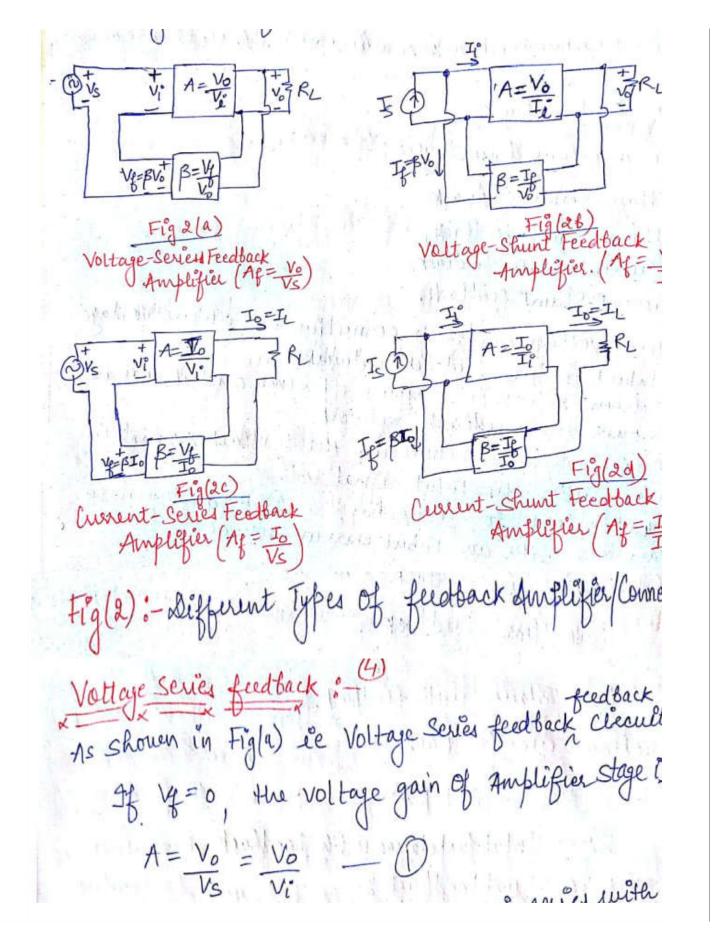

Figla) About ICSCS connected as Astable oscillator, pultividuator. The two external revistances PA, to trigger input. The two external revistances PA, RB and a capacitor C is used in the circuit.

The circuit has no stable state. The circuit changes its state alternately. Hence the operation is also called free Running non-sinusoidal oscillator

The since  $Q_{n-1} \Rightarrow Q_n = 0$   $Q_n =$

Now due capacitor voltage is also a shreshold voltage. While charging, capacitor voltage increases and thus threshold holtage increases. When it exceeds 2 Vcc, then comparator-1 output goes high which sets the flip-flop and they on is high and On becomes low Discharging Time Constan is RBC. -> When touparator & capacitor voltage becomes less trom Comparator-& output goes-high, resetting the flip-flop. This cycle repeats. -> when capacitor charges, output is high while when it is discharging the output is low. changing via RA and RB & discharging via RB. > Capacitor Cuthert Capaciti +Vcc Voltage < ono+Vcc (5V) 8 4 7 3 IC RB: DIOLUF rematic diagram

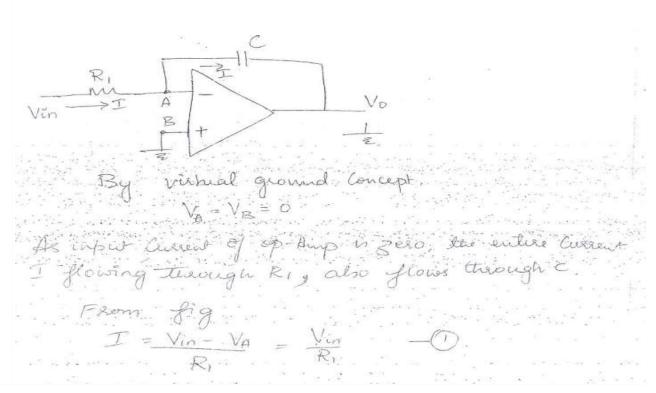

8(a) Explain the working of Integrator using op-amp and derive the output expression.

[5]

From Ofp xide,

$$I = C \frac{d(V_A - V_O)}{dt}$$

$$I = -C \frac{dV_O}{dt} - 2$$

$$\frac{V_{in}}{R_1} = -C \frac{dV_O}{dt}$$

Win and the constant of integration of input hence called integration for the constant of integration of the constant of integration in Ramp want from Square in Square in Atlanguage.

Also Draw wave forms

Vo=-(2.V1+3.V2+6.V3)

$$V_0 = -\frac{\left[\frac{R_f}{R_1}\left(V_1\right) + \frac{R_f}{R_2}.V_2 + \frac{R_f}{R_3}.V_3\right]}{\frac{R_f}{R_1} = 2}$$

$$\frac{R_f}{R_1} = 2 \qquad \frac{R_f}{R_2} = 3 \qquad \frac{R_f}{R_3} = 6$$

$$\frac{Rf}{R_1} = 2 \qquad \frac{Rf}{R_2} = 3 \qquad \frac{Rf}{R_3} = 0$$

alsuming

$$R_2 = 10 \text{ km}$$

$R_1 = 5 \text{ km}$   $R_2 = 3.3 \text{ km}$   $R_3 = 1.66 \text{ km}$