| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

|                                                                                                                                                                                |                                                                                                                                                            | Intern            | al Assessme                   | nt Test 3 – DEC | 2020      | (Scheme & S | Solution)                                   |             | ACCRESITED WITH AT GROOT |    |     |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------|-----------------|-----------|-------------|---------------------------------------------|-------------|--------------------------|----|-----|--|

| Sub:                                                                                                                                                                           | POWER ELE                                                                                                                                                  | POWER ELECTRONICS |                               |                 | Sub Code: |             |                                             | Branch: ECE |                          |    |     |  |

| Date:                                                                                                                                                                          | 16-12-2020                                                                                                                                                 | Duration:         | 90 mins<br>(2pm to<br>3.30pm) | Max Marks:      | 50        | Sem / Sec   | 7 <sup>th</sup> Semester, Sections-A,B,C,D. |             |                          |    |     |  |

|                                                                                                                                                                                |                                                                                                                                                            |                   |                               |                 |           |             |                                             |             | OB                       |    | E   |  |

|                                                                                                                                                                                |                                                                                                                                                            | An                | swer any FIV                  | VE FULL Quest   | ions      |             |                                             |             | MARK<br>S                | СО | RBT |  |

| With a neat diagram and waveforms, explain the principle of operation of step down chopper with RL load and derive the expression for the peak ripple current of the inductor. |                                                                                                                                                            |                   |                               |                 |           |             |                                             | [10]        | CO2                      | L3 |     |  |

| Sol                                                                                                                                                                            | n.                                                                                                                                                         |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

| Diagram & Waveforms= 4 marks, Explanation = 3 marks, Derivation= 3 marks.                                                                                                      |                                                                                                                                                            |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

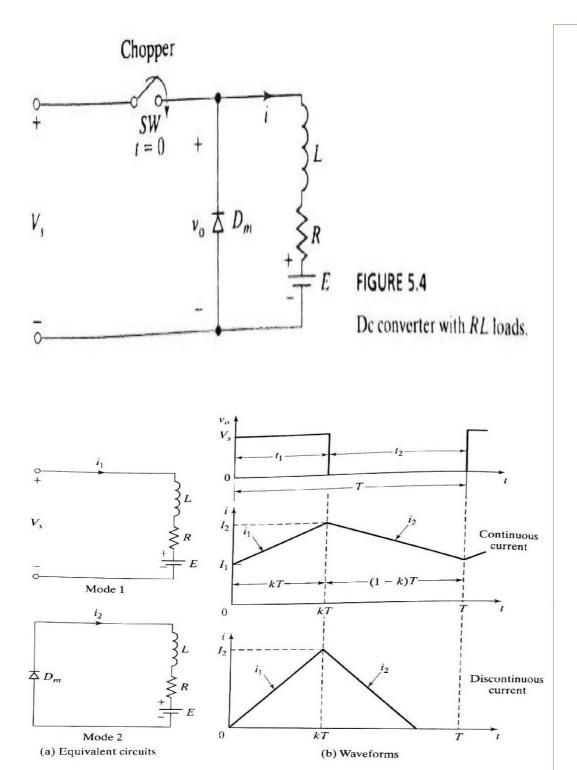

| <ul> <li>A converter with an RL load is shown in Figure 5.4.</li> </ul>                                                                                                        |                                                                                                                                                            |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

| • The operation of the converter can be divided into 2 modes.                                                                                                                  |                                                                                                                                                            |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

| • During mode 1, the converter is switched on.                                                                                                                                 |                                                                                                                                                            |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

| • The current flows from the supply to the load.                                                                                                                               |                                                                                                                                                            |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

| • During mode 2, the converter is switched off.                                                                                                                                |                                                                                                                                                            |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

|                                                                                                                                                                                | $ \bullet  \text{ The load current continues to flow through freewheeling diode } D_m. \\$                                                                 |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

|                                                                                                                                                                                | • The equivalent circuits for these modes are shown in Figure 5.5a.                                                                                        |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

|                                                                                                                                                                                | <ul> <li>The load current &amp; output voltage waveforms are shown in Figure 5.5b with the assumption<br/>that the load current rises linearly.</li> </ul> |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

|                                                                                                                                                                                | <ul> <li>However, the current flowing through an RL load rises or falls exponentially with a time<br/>constant.</li> </ul>                                 |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

|                                                                                                                                                                                | • The load time constant $(\tau=L/R)$ is generally much higher than the switching period T.                                                                |                   |                               |                 |           |             |                                             |             |                          |    |     |  |

Thus, the linear approximation is valid for many circuit conditions.

Simplified expressions can be derived within reasonable accuracies.

FIGURE 5.5

Equivalent circuits and waveforms for *RL* loads.

The load current for mode 1 can be found from

$$V_s = Ri_1 + L\frac{di_1}{dt} + E$$

which with initial current  $i_1(t=0) = I_1$  gives the load current as

$$i_1(t) = I_1 e^{-tR/L} + \frac{V_s - E}{R} (1 - e^{-tR/L})$$

(5.19)

This mode is valid  $0 \le t \le t_1 (=kT)$ ; and at the end of this mode, the load current becomes

$$i_1(t = t_1 = kT) = I_2$$

(5.20)

The load current for mode 2 can be found from

$$0 = Ri_2 + L\frac{di_2}{dt} + E$$

With initial current  $i_2(t=0) = I_2$  and redefining the time origin (i.e., t=0) at the beginning of mode 2, we have

$$i_2(t) = I_2 e^{-tR/L} - \frac{E}{R} (1 - e^{-tR/L})$$

(5.21)

This mode is valid for  $0 \le t \le t_2 [= (1 - k)T]$ . At the end of this mode, the load current becomes

$$i_2(t=t_2) = I_3 (5.22)$$

At the end of mode 2, the converter is turned on again in the next cycle after time,  $T = 1/f = t_1 + t_2$ .

Under steady-state conditions,  $I_1 = I_3$ . The peak-to-peak load ripple current can be determined from Eqs. (5.19) to (5.22). From Eqs. (5.19) and (5.20),  $I_2$  is given by

$$I_2 = I_1 e^{-kTR/L} + \frac{V_s - E}{R} \left( 1 - e^{-kTR/L} \right)$$

(5.23)

From Eqs. (5.21) and (5.22),  $I_3$  is given by

$$I_3 = I_1 = I_2 e^{-(1-k)TR/L} - \frac{E}{R} \left( 1 - e^{-(1-k)TR/L} \right)$$

(5.24)

Solving for  $I_1$  and  $I_2$  we get

$$I_1 = \frac{V_S}{R} \left( \frac{e^{kz} - 1}{e^z - 1} \right) - \frac{E}{R} \tag{5.25}$$

where  $z = \frac{TR}{L}$  is the ratio of the chopping or switching period to the load time constant.

$$I_2 = \frac{V_s}{R} \left( \frac{e^{-kz} - 1}{e^{-z} - 1} \right) - \frac{E}{R}$$

(5.26)

The peak-to-peak ripple current is

$$\Delta I = I_2 - I_1$$

which after simplifications becomes

$$\Delta I = \frac{V_s}{R} \frac{1 - e^{-kz} + e^{-z} - e^{-(1-k)z}}{1 - e^{-z}}$$

(5.27)

The condition for maximum ripple,

$$\frac{d(\Delta I)}{dk} = 0 ag{5.28}$$

gives  $e^{-kz} - e^{-(1-k)z} = 0$  or -k = -(1-k) or k = 0.5. The maximum peak-to-peak ripple current (at k = 0.5) is

$$\Delta I_{\text{max}} = \frac{V_s}{R} \tanh \frac{R}{4fL} \tag{5.29}$$

For  $4fL \gg R$ ,  $\tanh \theta \approx \theta$  and the maximum ripple current can be approximated to

$$\Delta I_{\text{max}} = \frac{V_s}{4fL} \tag{5.30}$$

Note: Equations (5.19) to (5.30) are valid only for continuous current flow. For a large off-time, particularly at low-frequency and low-output voltage, the load current may be discontinuous. The load current would be continuous if  $L/R \gg T$  or  $Lf \gg R$ . In case of discontinuous load current,  $I_1 = 0$  and Eq. (5.19) becomes

$$i_1(t) = \frac{V_s - E}{R} (1 - e^{-tR/L})$$

and Eq. (5.21) is valid for  $0 \le t \le t_2$  such that  $i_2(t = t_2) = I_3 = I_1 = 0$ , which gives

$$t_2 = \frac{L}{R} \ln \left( 1 + \frac{RI_2}{E} \right)$$

Because at t = kT, we get

$$i_1(t) = I_2 = \frac{V_s - E}{R} \left( 1 - e^{-kz} \right)$$

which after substituting for  $I_2$  becomes

$$t_2 = \frac{L}{R} \ln \left[ 1 + \left( \frac{V_s - E}{E} \right) \left( 1 - e^{-kz} \right) \right]$$

# Condition for continuous current: For $I_1 \ge 0$ , Eq. (5.25) gives

$$\left(\frac{e^{kz}-1}{e^z-1}-\frac{E}{V_s}\right) \ge 0$$

which gives the value of the load electromotive force (emf) ratio  $x = E/V_s$  as

$$x = \frac{E}{V_s} \le \frac{e^{kz} - 1}{e^z - 1} \tag{5.31}$$

With a neat circuit diagram and wave form, explain buck regulator.

Soln.

Figure & waveforms= 5marks, Explanation = 5 marks.

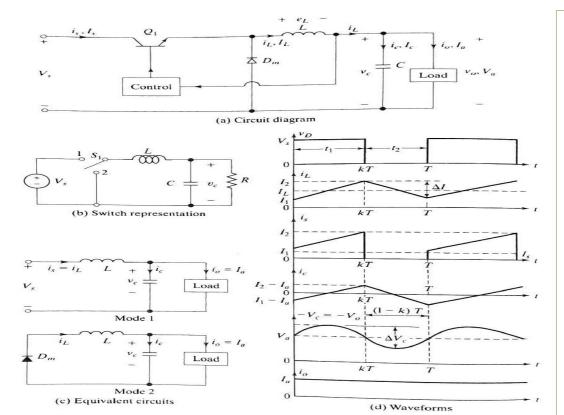

- In a buck regulator, the average output voltage V<sub>a</sub> is less than the input voltage, V<sub>s</sub> hence the name "buck".

- It is a very popular regulator.

- The circuit diagram of a buck regulator using a power BJT is shown in Figure 5.17a.

- This is like a step-down converter.

- Transistor Q<sub>1</sub> acts as a controlled switch & diode D<sub>m</sub> is an uncontrolled switch.

- They operate as 2 single-pole-single-through (SPST) bidirectional switches.

- The circuit in Figure 5.17a is often represented by 2 switches as shown in Figure 5.17b.

- The circuit operation can be divided into 2 modes.

- Mode 1 begins when transistor  $Q_1$  is switched on at t=0.

- The input current, which rises, flows through filter inductor L, filter capacitor C, & load resistor R.

- Mode 2 begins when transistor Q<sub>1</sub> is switched off at t=t<sub>1</sub>.

- The inductor current continues to flow through L, C, load, and diode D<sub>m</sub>.

- The inductor current falls until transistor Q<sub>1</sub> is switched on again in the next cycle.

- The equivalent circuits for the modes of operation are shown in Figure 5.17c.

- The waveforms for the voltages and currents are shown in Figure 5.17d for a continuous

[10] CC

CO2

L3

current flow in the inductor L.

- It is assumed that the current rises & falls linearly.

- In practical circuits, the switch has a finite, nonlinear resistance.

- Its effect can generally be negligible in most applications.

- Depending on the switching frequency, filter inductance, & capacitance, the inductor current could be discontinuous.

The voltage across the inductor L is, in general,

$$e_L = L \frac{di}{dt}$$

Assuming that the inductor current rises linearly from  $I_1$  to  $I_2$  in time  $t_1$ ,

$$V_s - V_a = L \frac{I_2 - I_1}{t_1} = L \frac{\Delta I}{t_1}$$

(5.52)

or

$$t_1 = \frac{\Delta I L}{V_s - V_a} \tag{5.53}$$

and the inductor current falls linearly from  $I_2$  to  $I_1$  in time  $t_2$ ,

$$-V_a = -L \frac{\Delta I}{t_2} \tag{5.54}$$

or

$$t_2 = \frac{\Delta I L}{V_a} \tag{5.55}$$

where  $\Delta I = I_2 - I_1$  is the peak-to-peak ripple current of the inductor L. Equating the value of  $\Delta I$  in Eqs. (5.52) and (5.54) gives

$$\Delta I = \frac{(V_s - V_a)t_1}{L} = \frac{V_a t_2}{L}$$

FIGURE 5.17

Buck regulator with continuous  $i_L$ .

Substituting  $t_1 = kT$  and  $t_2 = (1 - k)T$  yields the average output voltage as

$$V_u = V_s \frac{t_1}{T} = kV_s \tag{5.56}$$

Assuming a lossless circuit,  $V_sI_s=V_aI_a=kV_sI_a$  and the average input current

$$I_s = kI_a \tag{5.57}$$

Peak-to-peak inductor ripple current. The switching period T can be expressed as

$$T = \frac{1}{f} = t_1 + t_2 = \frac{\Delta I L}{V_s - V_a} + \frac{\Delta I L}{V_a} = \frac{\Delta I L V_s}{V_a (V_s - V_a)}$$

(5.58)

which gives the peak-to-peak ripple current as

$$\Delta I = \frac{V_a(V_s - V_a)}{fLV_s} \tag{5.59}$$

or

$$\Delta I = \frac{V_s k (1 - k)}{fL} \tag{5.60}$$

[10]

CO<sub>2</sub>

L3

3. Explain the operation of a step-up chopper with resistive load. For a step up chopper, derive the expression for output voltage and show that the output voltage is greater than the input voltage.

Circuit diagram & waveforms = 4 marks, Explanation = 4 marks, Derivation = 2 marks.

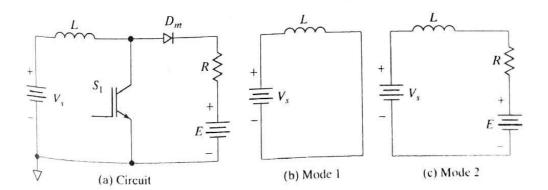

- A step-up converter with a resistive load is shown in Figure 5.9a.

- When switch  $S_1$  is closed, the current rises through L & the switch.

- The equivalent circuit during mode 1 is shown in Figure 5.9b.

- The current is described by

$$V_s = L \frac{d}{dt} i_1$$

which for an initial current of  $I_1$  gives

$$i_1(t) = \frac{V_s}{L}t + I_1 \tag{5.39}$$

FIGURE 5.9

Step-up converter with a resistive load.

which is valid for  $0 \le t \le kT$ . At the end of mode 1 at t = kT,

$$I_2 = i_1(t = kT) = \frac{V_s}{I_c}kT + I_1$$

(5.40)

When switch  $S_1$  is opened, the inductor current flows through the RL load.

The equivalent circuit is shown in Figure 5.9c and the current during mode 2 is described by

$$V_s = Ri_2 + L\frac{di_2}{dt} + E$$

which for an initial current of  $I_2$  gives

$$i_2(t) = \frac{V_s - E}{R} \left( 1 - e^{\frac{-iR}{L}} \right) + I_2 e^{\frac{-iR}{L}}$$

(5.41)

which is valid for  $0 \le t \le (1 - k)T$ . At the end of mode 2 at t = (1 - k)T,

$$I_1 = i_2[t = (1 - k)T] = \frac{V_s - E}{R} \left[ 1 - e^{-(1-k)z} \right] + I_2 e^{-(1-k)z}$$

(5.42)

where z = TR/L. Solving for  $I_1$  and  $I_2$  from Eqs. (5.40) and (5.42), we get

$$I_1 = \frac{V_s kz}{R} \frac{e^{-(1-k)z}}{1 - e^{-(1-k)z}} + \frac{V_s - E}{R}$$

(5.43)

$$I_2 = \frac{V_s kz}{R} \frac{1}{1 - e^{-(1-k)z}} + \frac{V_s - E}{R}$$

(5.44)

The ripple current is given by

$$\Delta I = I_2 - I_1 = \frac{V_s}{R}kT \tag{5.45}$$

These equations are valid for  $E \le V_s$ . If  $E \ge V_s$  and the converter switch  $S_1$  is opened, the inductor transfers its stored energy through R to the source and the inductor current is discontinuous.

When the converter is turned on, the voltage across the inductor is

$$v_L = L \frac{di}{dt}$$

and this gives the peak-to-peak ripple current in the inductor as

$$\Delta I = \frac{V_s}{L} t_1 \tag{5.34}$$

The average output voltage is

$$v_o = V_s + L \frac{\Delta I}{t_2} = V_s \left( 1 + \frac{t_1}{t_2} \right) = V_s \frac{1}{1 - k}$$

(5.35)

Explain how the choppers are classified with reference to load voltage and load current with relevant circuits.

[10] CO2

L2

Soln.

Each of 5 types- Explanation & diagram= 2marks \*5= 10 marks.

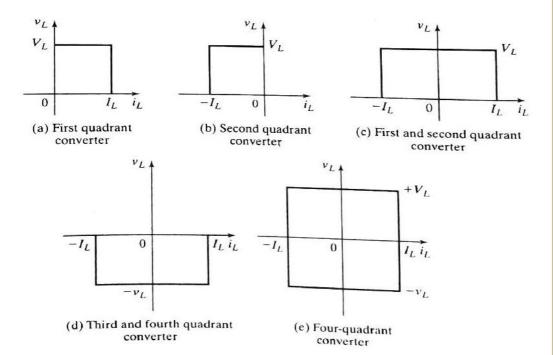

- Depending on the directions of current & voltage flows, dc converters can be classified into 5 types:

- 1) First quadrant converter

- 2) Second quadrant converter

- 3) First and second quadrant converter

- 4) Third and fourth quadrant converter

- 5) Four-quadrant converter

FIGURE 5.11

De converter classification.

With a neat circuit diagram and wave forms explain the working of a single phase voltage source inverter, also derive the related expressions.

[10] CC

CO3 L3

Soln.

Circuit & Waveforms= 5 marks, Explanation= 5 marks.

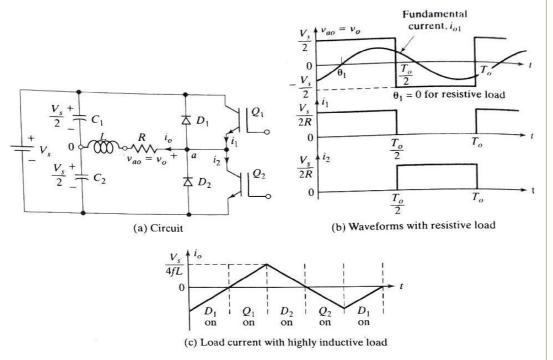

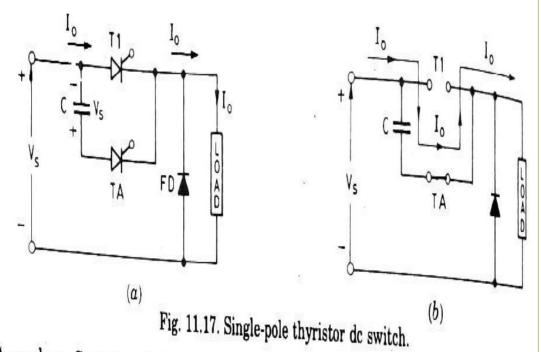

- The principle of single-phase inverters can be explained with Figure 6.2a.

- The inverter circuit consists of 2 choppers.

- When only transistor  $Q_1$  is turned on for a time  $T_o/2$ , the instantaneous voltage across the load  $v_o$  is  $V_s/2$ .

- If only transistor  $Q_2$  is turned on for a time  $T_0/2$ ,  $-V_s/2$  appears across the load.

- The logic circuit should be designed such that  $Q_1 \& Q_2$  are not turned on at the same time.

- Figure 6.2b shows the waveforms for the output voltage & transistor currents with a resistive load.

- It should be noted that the phase shift is  $\theta_1$ =0 for a resistive load.

- This inverter requires a three-wire dc source, & when a transistor is off, its reverse voltage is V<sub>s</sub> instead of V<sub>s</sub>/2.

- This inverter is known as a **half-bridge inverter**.

FIGURE 6.2 Single-phase half-bridge inverter.

With a neat diagram and waveforms, explain the principle of operation of a single phase current source inverter and DC link inverter.

[10] CO3

L3

Soln.

Current Source inverter – diagram & explanation= 5marks, DC link inverter- diagram & explanation= 5 marks.

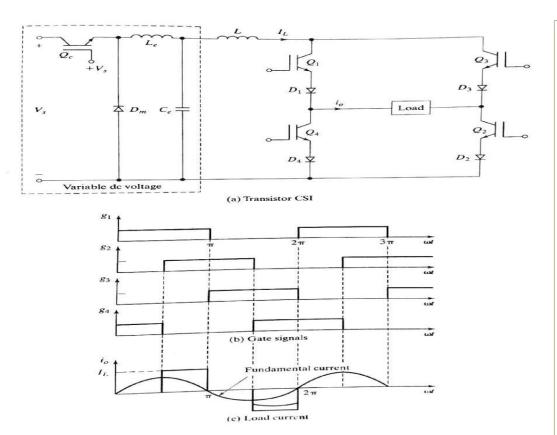

- In the previous sections, the inverters are fed from a voltage source.

- The load current is forced to fluctuate from positive to negative, & vice versa.

- To cope with inductive loads, the power switches with freewheeling diodes are required.

- In a current-source inverter (CSI), the input behaves as a current source.

FIGURE 6.36

Single-phase current source.

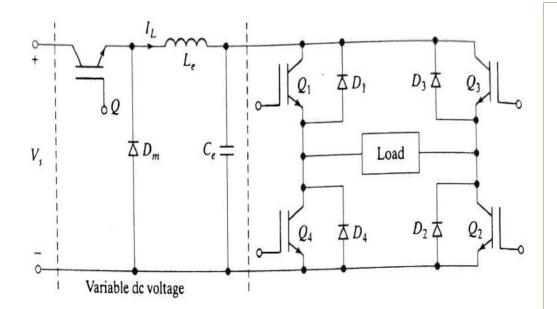

- The output voltage of an inverter can be controlled by varying the modulation index (or pulse widths).

- Also, we need to maintain the dc input voltage constant.

- However, in this type of voltage control, a range of harmonics would be present on the output voltage.

- The pulse widths can be maintained fixed to eliminate or reduce certain harmonics.

- The output voltage can be controlled by varying the level of dc input voltage.

- Such an arrangement as shown in Figure 6.38 is known as a **variable dc-link inverter**.

- This arrangement requires an additional converter stage.

- If it is a converter, the power cannot be fed back to the dc source.

- To obtain the desired quality & harmonics of the output voltage, the shape of the output voltage can be predetermined.

- This is shown in Figure 6-1b or Figure 6.36.

- The dc supply is varied to give variable ac output.

#### FIGURE 6.38

Variable dc-link inverter.

7 Explain different types of static switches with relevant circuits.

Soln.

Explaining Static switch=2 marks, AC Static switch- Figure & explanation = 4 marks, DC static switch - Figure & explanation = 4 marks.

- A switch having no moving parts is called a static switch.

- Power semiconductor devices which can be turned on & off within a few microseconds can be used as fast-acting static switches.

- For high-power applications, thyristors are being used as static switches.

- For low-power applications, power transistors are preferred.

- Static switches are of 2 types:

- AC switches

- DC switches

- If the input is ac, ac SSs are used & for dc input, dc SSs are used.

- Switching speed for ac switches is governed by the supply frequency & turn-off time of thyristors.

- For dc static switches, the switching speed depends on the commutation circuitry & turn-off time of fast thyristors.

- AC switches may be single-phase or three-phase.

[10]

CO3 L2

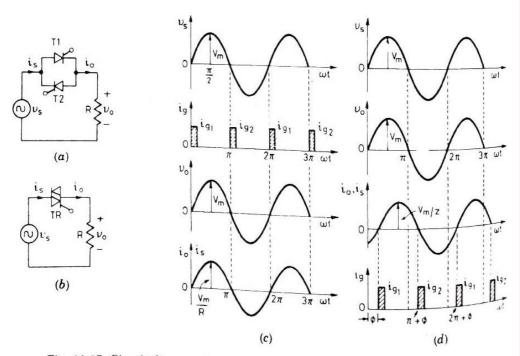

The circuit diagram of a single-phase ac switch is shown in Fig. 11.15 (a). Here two thyristors are connected in anti-parallel. For resistive load in Fig. 11.15 (a), the waveforms for source voltage  $v_s$ , triggering pulse  $i_{g1}$  for T1 and pulse  $i_{g2}$  for T2, load voltage  $v_0$  and load current  $i_0$  are shown in Fig. 11.15(c). Note that T1 is triggered at  $\omega t = 0^\circ$ ,  $\omega t = 2\pi$ , .... and T2 is triggered at  $\omega t = \pi$ ,  $3\pi$  ..... when the load current waveform is passing through zero. For RL load, output or load current  $i_0$  lags  $v_0$  by load power-factor angle  $\phi = \tan^{-1} \frac{\omega L}{R}$ . For RL load, T1 must be triggered at  $\omega t = \phi$ ,  $2\pi + \phi$ ,.... and T2 at  $\pi + \phi$ ,  $3\pi + \phi$  and so on, Fig. 11.15(d). A triac TR can replace two anti-parallel thyristors as shown in Fig. 11.15(b). For triac, only one pulse  $i_g = i_{g1} = i_{g2}$  in each half cycle will be required.

Fig. 11.15. Circuit diagram for single-phase ac switch (a) using two thyristors (b) using one triac (c) waveforms for R load (d) waveforms for RL load.

- As stated before, in dc switches, the input voltage is dc.

- Power semiconductor devices used in a dc switch may be transistors, thyristors or GTOs.

- When thyristor is used, it must have forced commutation circuitry as an integral part of dc switch.

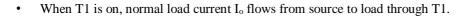

- One such circuit giving the principle of operation of a dc switch is shown in Fig.11.17(a).

- Here T1 is the main thyristor & TA is the auxiliary thyristor.

- Capacitor C is charged to source voltage V<sub>s</sub> with lower plate positive.

- For breaking the dc circuit, auxiliary thyristor TA is turned on.

- Capacitor C at once applies a reverse voltage across T1 turning it off at once.

in turned . A

- After this, load current flows as shown in Fig.11.17(b).

- Capacitor now gets charged from  $+V_s$  to  $-V_s$  and current through TA falls below its holding current to turn it off.

CO3

[10]

L2

- Subsequently, freewheeling diode takes over & load current eventually decays to zero.

- 8 Explain what is an inverter? Also, explain different performance parameters of inverter.

Soln.

Inverter explanation= 2 marks, 4 performance parameters = 2marks \* 4= 8 marks.

- DC-to-AC converters are known as **inverters**.

- The function of an inverter is to change a dc input voltage to a symmetric ac output voltage of desired magnitude & frequency.

- The output voltage could be fixed or variable at a fixed or variable frequency.

- A variable output voltage can be obtained.

- This is done by varying the input dc voltage & maintaining the gain of the inverter constant.

- On the other hand, if the dc input voltage is fixed & it is not controllable, a variable output voltage can be obtained.

- This is done by varying the gain of the inverter, which is normally accomplished by pulse-width-modulation (PWM) control within the inverter.

- The **inverter gain** may be defined as the ratio of the ac output voltage to dc input voltage.

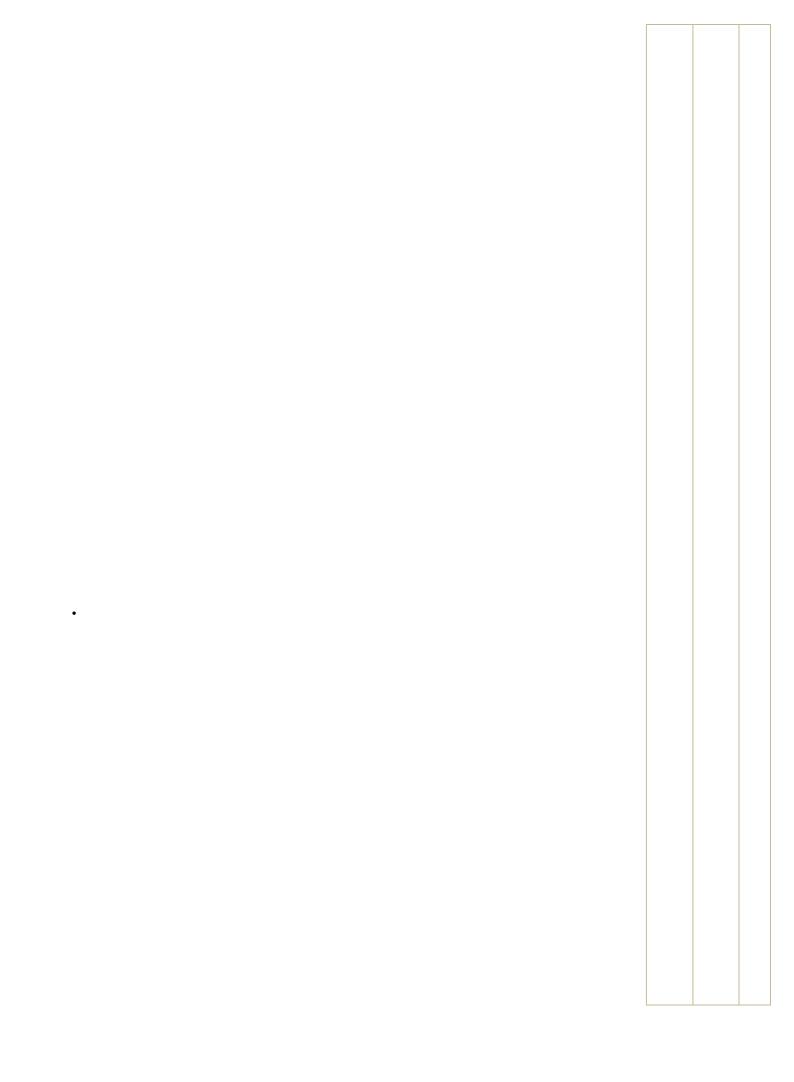

- The input voltage to an inverter is dc & the output voltage (or current) is ac as shown in Figure 6.1a.

- The output should ideally be an ac of pure sine wave.

- But the output voltage of a practical inverter contains harmonics or ripples as shown in Figure

6.1b

- The inverter draws current from the dc input source only when the inverter connects the load to the supply source.

- The input current is not pure dc, but it contains harmonics as shown in Figure 6.1c.

- The quality of an inverter is normally evaluated in terms of the following performance parameters.

FIGURE 6.1

Input and output relationship of a dc-ac converter.

The output power is given by

$$P_{\rm ac} = I_o V_o \cos \theta \tag{6.1}$$

$$=I_0^2R\tag{6.1a}$$

where  $V_o$  and  $I_o$  are the rms load voltage and load current,  $\theta$  is the angle of the load impedance, and R is the load resistance.

The ac input power of the inverter is

$$P_{S} = I_{S}V_{S} \tag{6.2}$$

where  $V_S$  and  $I_S$  are the average input voltage and input current.

The rms ripple content of the input current is

$$I_r = \sqrt{I_i^2 - I_s^2} (6.3)$$

where  $I_i$  and  $I_s$  are the rms and average values of the dc supply current.

The ripple factor of the input current is

$$RF_s = \frac{I_r}{I_s} \tag{6.4}$$

The power efficiency, which is the ratio of the output power to the input power, will depend on the switching losses, which in turn depends on the switching frequency of the inverter.

Harmonic factor of *n*th harmonic ( $HF_n$ ). The harmonic factor (of the *n*th harmonic), which is a measure of individual harmonic contribution, is defined as

$$HF_n = \frac{V_{on}}{V_{o1}} \quad \text{for } n > 1 \tag{6.5}$$

where  $V_{o1}$  is the rms value of the fundamental component and  $V_{on}$  is the rms value of the *n*th harmonic component.

Total harmonic distortion (THD). The total harmonic distortion, which is a measure of closeness in shape between a waveform and its fundamental component, is defined as

THD =

$$\frac{1}{V_{o1}} \left( \sum_{n=2,3,...}^{\infty} V_{on}^2 \right)^{1/2}$$

(6.6)

**Distortion factor (DF).** THD gives the total harmonic content, but it does not indicate the level of each harmonic component. If a filter is used at the output of inverters, the higher order harmonics would be attenuated more effectively. Therefore, a knowledge of both the frequency and magnitude of each harmonic is important. The DF indicates the amount of HD that remains in a particular waveform after the harmonics of that waveform have been subjected to a second-order attenuation (i.e., divided by  $n^2$ ). Thus, DF is a measure of effectiveness in reducing unwanted harmonics without having to specify the values of a second-order load filter and is defined as

$$DF = \frac{1}{V_{o1}} \left[ \sum_{n=2.3}^{\infty} \left( \frac{V_{on}}{n^2} \right)^2 \right]^{1/2}$$

(6.7)

The DF of an individual (or nth) harmonic component is defined as

$$DF_n = \frac{V_{on}}{V_{o1}n^2} \quad \text{for } n > 1$$

(6.8)

Lowest order harmonic (LOH). The LOH is that harmonic component whose frequency is closest to the fundamental one, and its amplitude is greater than or equal to 3% of the fundamental component.

## **Key Points of Section 6.2**

• The performance parameters, which measure the quality of the inverter output voltage, are HF, THD, DF, and LOH.

NOTE: THE QUESTIONS SHOULD BE NEATLY WRITTEN & ANSWERED IN STUDENT'S OWN HANDWRITING. ON TOP OF EACH PAGE, WRITE YOUR NAME & USN BEFORE MAKING A PDF AND UPLOADING THE PDF IN GOOGLE CLASSROOM. TOTAL TIME TAKEN SHOULD NOT EXCEED 2 HOURS FOR BOTH ANSWERING & UPLOADING THE PDF (1.5 HOURS FOR ANSWERING + 0.5 HOURS FOR UPLOADING PDF). PDF SUBMITTED AFTER 2 HOURS OR NOT AS PER THE ABOVE INSTRUCTIONS WILL NOT BE VALUATED AND MARKS ALLOTED WILL BE ZERO FOR THE TEST.

### **ALL THE BEST**