# Sixth Semester B.E. Degree Examination, Feb./Mar. 2022 VLSI Design

Time: 3 hrs.

Max. Marks: 80

Note: Answer any FIVE full questions, choosing ONE full question from each module.

## Module-1

- a. With neat diagrams, explain the operation of nMOS enhancement mode transistor. (06 Marks)

- b. Explain the following non-ideal effects of MOS device

- i) Channel length modulation

- ii) Body effect

- iii) Noise margin.

(10 Marks)

#### OF

- 2 a. With neat diagrams, discuss the nMOS fabrication process steps. (08 Marks)

- b. Explain the CMOS inverter DC characteristics with neat diagrams and equations. (08 Marks)

## Module-2

- 3 a. Draw the circuit diagram and stick diagram for the expression  $f = \overline{A(B+C)}$  using nMOS and CMOS design styles. (08 Marks)

- b. With neat diagrams, explain λ-based design rules for wires, transistors and contacts in nMOS and CMOS process.

(08 Marks)

#### OR

- 4 a. Derive an equation for rise time and fall time with respect to CMOS inverter. (10 Marks)

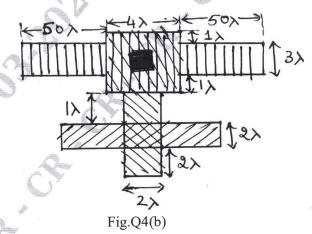

- b. Estimate the total area capacitance for the structure shown in Fig.Q4(b). Consider  $5\mu m$  technology with relative C values for metal =  $0.075\Box Cg$  and polysilicon =  $0.1\Box Cg$ .

(06 Marks)

### Module-3

- 5 a. Identify various scaling models and derive the scaling factors for any eight device parameters. (10 Marks)

- b. Explain the operation of 4-bit barallel shifter with neat diagram.

(06 Marks)

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice. Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages

(06 Marks)

OR

Implement 4-bit carry look ahead adder using Multiple Output Domino Logic (MODL) with (08 Marks) necessary equations. b. With neat circuit diagram and truth table, explain the operation of Manchester carry chain (08 Marks)

adder.

Module-4

Explain the operation of (n + 1) bit parity generator with relevant circuit diagram and stick 7 (08 Marks) diagram.

b. Implement 4:1 MUX using switch logic with relevant truth table and equations. Also write (08 Marks) the stick diagram.

OR

With neat diagram, explain design abstraction for FPGA (Filed Programmable Gate Array). (08 Marks)

(08 Marks) Explain the architecture of field programmable gate array.

> BANGALORE - 560 037 Module-5

Explain the operation of 4 transistor dynamic memory and 6 transistor CMOS memory cells (10 Marks) with sense amplifier circuit with neat circuit diagrams.

Explain the operation of D-latch using nMOS and CMOS design styles.

OR

Identify various fault models and explain each fault model with relevant diagrams and 10

Explain the operation of built in logic block observation (BILBO) used in testing. (04 Marks)