| USN |  |  |  |  |  |  |  |  |  |  |

|-----|--|--|--|--|--|--|--|--|--|--|

|-----|--|--|--|--|--|--|--|--|--|--|

|       |                                                                                                 | Intern                | a Assessment Te     | 501    | Deceniidei    | 2021           | -       |       |     |    |

|-------|-------------------------------------------------------------------------------------------------|-----------------------|---------------------|--------|---------------|----------------|---------|-------|-----|----|

| Sub:  | Analog and Digital                                                                              | l Electronics         |                     |        | Sub Code:     | 18CS33         | Branch  | : ISE |     |    |

| Date: | 17/12/2021                                                                                      | Duration: 90 min      | 's Max Marks:       | 50     | Sem/Sec:      | III / A,B and  | С       |       | OBE |    |

|       |                                                                                                 |                       | MARKS               | СО     | RBT           |                |         |       |     |    |

| 1     | Define Implicants, Combinational Circuits. Explain prime and essential prime implicants with 10 |                       |                     |        |               |                |         |       |     | L2 |

|       | example. Find the                                                                               | minterm & maxter      | n expansion of F(a  | a,b,c, | d)=a'(b'+d)+  | -acd'. Show t  | hat a'c |       |     |    |

|       | +b'c'+ab=a'b                                                                                    | b' + bc + ac'         |                     |        |               |                |         |       |     |    |

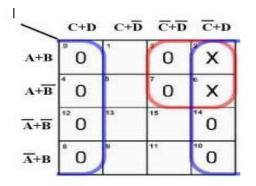

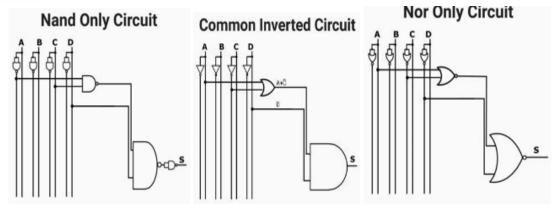

| 2     | What is K-map &                                                                                 | k explain limitations | of K-map? Solve     | F(A,   | B,C,D) =      |                |         | 10    | CO3 | L2 |

|       | ПМ(0,3,4,7,810,12                                                                               | 2,14).IID(2,6) using  | K map to get minim  | mum    | POS express   | sion and imple | ement   |       |     |    |

|       | using basic, NAND only and NOR only gates.                                                      |                       |                     |        |               |                |         |       |     |    |

| 3     | What is Quine- McCuskey Method? Find the minimum SOP for the function.F (A,10                   |                       |                     |        |               |                |         | 10    | CO3 | L1 |

|       | B, C, D) = $\Sigma$ m(0,4,5,10,11,13,15) + $\Sigma$ d(1, 10, 15) using Quine McCuskey method.   |                       |                     |        |               |                |         |       |     |    |

| 4     | Consider the following logic function $F(A, B, C, D) = \Sigma m(0,4,5,10,11,13,14,15)$ . 10     |                       |                     |        |               |                |         |       | CO3 | L1 |

|       | a) Find two different minimum circuits which implements F using AND and OR gates.               |                       |                     |        |               |                |         |       |     |    |

|       | Identify two haza                                                                               | ards in each circuit. |                     |        |               |                |         |       |     |    |

|       | b) Find an AND-                                                                                 | OR circuit for F whi  | ch as no hazards.   |        |               |                |         |       |     |    |

|       | c) Find an OR- A                                                                                | ND circuit for F wh   | ich as no hazards.  |        |               |                |         |       |     |    |

| 5     | What is Multiple                                                                                | exer? Build 8: 1 M    | ux using basic ga   | tes.   |               |                |         | 10    | CO3 | L3 |

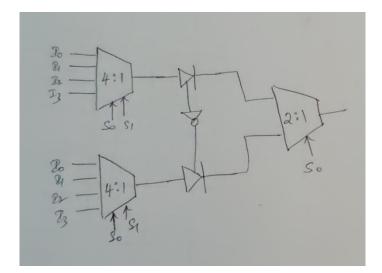

| 6     | What is Buffer?                                                                                 | Explain different th  | ee state buffers. C | Consti | ruct 8-to-1 N | IUX using tw   | 'o 4-   | 10    | CO3 | L3 |

|       | to-1 MUXes, two                                                                                 | three-state buffers,  | and one inverter.   |        |               |                |         |       |     |    |

#### Internal Assessment Test 1 – December 2021

| Faculty Signature |  |  |  |  |  |  |  | CC | I Signature |  |

|-------------------|--|--|--|--|--|--|--|----|-------------|--|

| USN               |  |  |  |  |  |  |  |    |             |  |

# HOD Signature

## Internal Assessment Test 1 – December 2021

| Sub:  | Analog and Digita                                                                               | l Electronics    |               |                  |        | Sub Code:     | 18CS33          | Branch  | : ISE |     |     |

|-------|-------------------------------------------------------------------------------------------------|------------------|---------------|------------------|--------|---------------|-----------------|---------|-------|-----|-----|

| Date: | 17/12/2021                                                                                      | Duration:        | 90 min's      | Max Marks:       | 50     | Sem/Sec:      | III / A,B and C | 5       |       | 0]  | BE  |

|       | Answer any FIVE FULL Questions                                                                  |                  |               |                  |        |               |                 |         |       | СО  | RBT |

| 1     | Define Implicants, Combinational Circuits. Explain prime and essential prime implicants with 10 |                  |               |                  |        |               |                 |         | 10    | CO3 | L2  |

|       | example. Find the                                                                               | e minterm &      | maxterm ex    | xpansion of F(a  | ı,b,c, | d)=a'(b'+d)+  | acd'. Show the  | nat a'c |       |     |     |

|       | +b'c'+ab=a'b                                                                                    | $b' + bc + ac^2$ | ,             |                  |        |               |                 |         |       |     |     |

| 2     | What is K-map &                                                                                 | & explain lim    | itations of H | K-map? Solve     | F(A,I  | 3,C,D) =      |                 |         | 10    | CO3 | L2  |

|       | ПМ(0,3,4,7,810,1                                                                                | 2,14).ПD(2,6     | 6) using K n  | nap to get minir | num    | POS express   | sion and imple  | ement   |       |     |     |

|       | using basic, NAND only and NOR only gates.                                                      |                  |               |                  |        |               |                 |         |       |     |     |

| 3     | What is Quine- McCuskey Method? Find the minimum SOP for the function.F (A,                     |                  |               |                  |        |               |                 | (A,     | 10    | CO3 | L1  |

|       | B, C, D) = $\Sigma$ m(0,4,5,10,11,13,15) + $\Sigma$ d(1, 10, 15) using Quine McCuskey method.   |                  |               |                  |        |               |                 |         |       |     |     |

| 4     | Consider the fo                                                                                 | llowing log      | ic function   | F(A, B, C, D)    | =Σ n   | n(0,4,5,10,11 | ,13,14,15).     |         | 10    | CO3 | L1  |

|       | a) Find two diff                                                                                | erent minim      | um circuits   | which implem     | ents   | F using AN    | D and OR ga     | ates.   |       |     |     |

|       | Identify two haza                                                                               | ards in each o   | circuit.      |                  |        |               |                 |         |       |     |     |

|       | b) Find an AND-                                                                                 | OR circuit fo    | or F which a  | is no hazards.   |        |               |                 |         |       |     |     |

|       | c) Find an OR- A                                                                                | AND circuit f    | or F which    | as no hazards.   |        |               |                 |         |       |     |     |

| 5     | What is Multiple                                                                                | exer? Build      | 8: 1 Mux u    | using basic gat  | tes.   |               |                 |         | 10    | CO3 | L3  |

| 6     | What is Buffer?                                                                                 | Explain diff     | erent three s | state buffers. C | onstr  | uct 8-to-1 N  | IUX using tw    | o 4-    | 10    | CO3 | L3  |

|       | to-1 MUXes, two                                                                                 | o three-state    | buffers, and  | one inverter.    |        |               |                 |         |       |     |     |

# <u>Scheme of Evaluation</u> <u>Internal Assessment Test 1 – December 2021</u>

| Sub:  | Analog and Digital Electronics |           |        |               |    |      |     | Code:   | 18CS33 |

|-------|--------------------------------|-----------|--------|---------------|----|------|-----|---------|--------|

| Date: | 17/12/2021                     | Duration: | 90mins | Max<br>Marks: | 50 | Sem: | III | Branch: | ISE    |

### Note: <u>Answer Any five full questions.</u>

| Question<br>No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Marks D              | Max<br>Marks |     |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------|-----|

| 1               | Implicants:<br>A group of one or more 1's which are adjacent a group of one<br>or more 1s which are adjacent and can be combined on<br>a Karnaugh Map is called an implicants.<br>Combinational Circuit:                                                                                                                                                                                                                                                                                                                                  | 1M<br>1M             | 10M          | 10M |

|                 | The output of the combinational circuit depends on the values at<br>the input at any given time.<br><b>Definition of Prime and Essential Prime Implicants:</b><br><b>Problem Solution</b>                                                                                                                                                                                                                                                                                                                                                 | 1M<br>2M<br>6M       |              |     |

| 2               | <ul> <li><i>Karnaugh map/K map</i> is a method simplifying and manipulating switching functions. K map method is faster and easier to apply than other simplification methods.</li> <li>Limitations of K map:</li> <li>Complexity of K-map simplification process increases with the increase in the number of variables</li> <li>K map is manual technique and simplification process heavily depends on the human ability.</li> <li>Solving the function using K map</li> <li>Logic circuit diagram using NAND and NOR Gates</li> </ul> | 1M<br>2M<br>3M<br>4M | 10M          | 10M |

| 3               | The Quine-McCluskey method reduces the minterm<br>expansion (standard sum-of-products form) of a function to<br>obtain a minimum sum of products.<br>Steps<br>Prime Implicate Chart<br>Final expression                                                                                                                                                                                                                                                                                                                                   | 2M<br>5M<br>3M       | 10M          | 10M |

| 4 | Finding Static 1 and Static 0 Hazard                                                                                                                                 | 4M       | 10M | 10M |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-----|

|   | Hazard free equation in terms of AND-OR                                                                                                                              | 2M       |     |     |

|   | Hazard free equation in terms of OR - AND                                                                                                                            | 2M       |     |     |

| 5 | The multiplexer is a device that has multiple inputs<br>and single line output. The select lines determine<br>which input is connected to the output.                | 2M       | 10M | 10M |

|   | Implementation of 8:1 MUX using basic gates<br>Block Diagram<br>Truth Table<br>Expression<br>Logic Diagram                                                           | 8M       |     |     |

| 6 | A <b>buffer</b> has only a single input and a single output with behavior that is the opposite of an NOT gate. It simply passes its input, unchanged, to its output. | 1M       | 10M | 10M |

|   | Different types of three state buffers<br>Implementing 8:1 MUX using 4:1 MUX and Buffers                                                                             | 4M<br>5M |     |     |

| Sub:    | Analog and Digital Electronics |           |        |               |    |      |   | Code:   | 18CS33 |

|---------|--------------------------------|-----------|--------|---------------|----|------|---|---------|--------|

| Date: 1 | 17/12/2021                     | Duration: | 90mins | Max<br>Marks: | 50 | Sem: | Ш | Branch: | ISE    |

#### Scheme Of Evaluation Internal Assessment Test 1 – NOV 2021

Note: <u>Answer Any full five questions</u>

**Q. 1** Define Implicants, Combinational Circuits. Explain prime and essential prime implicants with example. Find the minterm & maxterm expansion of F(a,b,c,d)=a'(b'+d)+acd'. Show that a'c + b'c' + ab = a'b' + bc + ac'.

#### Implicants:

A group of one or more 1's which are adjacent a group of one or more 1s which are adjacent and can be combined on a Karnaugh Map is called an **implicants**.

#### **Combinational Circuits:**

Combinational Circuits are circuits made up of different types of logic gates. The output of the combinational circuit depends on the values at the input at any given time.

#### Prime and Essential Prime Implicants:

A group of square or rectangle made up of bunch of adjacent minterms which is allowed by definition of K-Map are **called prime** implicants (**PI**). Consider a Boolean function, F = AB + ABC + BC. Implicants. are AB, ABC and BC. Prime implicants.

Essential prime implicants (EPI) are those prime implicants which always appear in final solution. Duplicate terms have been crossed out, because X + X = X. This expression can then be converted to decimal notation:

The maxterm expansion for f can then be obtained by listing the decimal integers (in the range 0 to 15) which do not correspond to minterms of f:

$f = \prod M(4, 6, 8, 9, 11, 12, 13, 15)$

Show that a'c + b'c' + ab = a'b' + bc + ac'.

We will find the minterm expansion of each side by supplying the missing variables. For the left side,

$\begin{aligned} a'c(b+b') + b'c'(a+a') + ab(c+c') \\ &= a'bc + a'b'c + ab'c' + a'b'c' + abc + abc' \\ &= m_3 + m_1 + m_4 + m_0 + m_7 + m_6 \end{aligned}$

For the right side,

$\begin{aligned} a'b'(c+c') + bc(a+a') + ac'(b+b') \\ &= a'b'c + a'b'c + abc + a'bc + abc' + abc' \\ &= m_1 + m_0 + m_7 + m_3 + m_6 + m_4 \end{aligned}$

Because the two minterm expansions are the same, the equation is valid.

Q.2 What is K-map & explain limitations of K-map? Solve  $F(A,B,C,D) = \Pi M(0,3,4,7,810,12,14)$ .  $\Pi D(2,6)$  using K map to get minimum POS expression and implement using basic, NAND only and NOR only gates.

*Karnaugh map/K map* is a method simplifying and manipulating switching functions. K map method is faster and easier to apply than other simplification methods.

## Limitations of K map:

- Complexity of K-map simplification process increases with the increase in the number of variables

- ➤ K map is manual technique and simplification process heavily depends on the human ability.

$S = (A + \overline{C}) \cdot (D)$

**Q.3** What is Quine- McCuskey Method? Find the minimum SOP for the function. F (A, B, C, D) =  $\Sigma$  m(0,4,5,10,11,13,15) +  $\Sigma$  d(1, 10, 15) using Quine McCuskey method.

**The Quine-McCluskey** method provides a systematic simplification procedure which can be readily programmed for a digital computer. The Quine-McCluskey method reduces the minterm expansion (standard sum-of-products form) of a function to obtain a minimum sum of products.

**Petrick's method** is a technique for determining all minimum sum-of-products solutions from a prime implicant chart

$F(A, B, C, D) = \Sigma m(2, 3, 7, 9, 11, 13) + \Sigma d(1, 10, 15)$  using Quine McCuskey method.

Q. 3: QM. Htd: F(A, B. C, D) = En(0, 4, 5, 10, 11, 13, 15) + Ed(1, 10, 15) Sop = 7 Salupion. Stage - 11 Stagein Stage -1 (0.1),000 - . (0,1,4,5) 0-0-ABCD 0 0000 1 (0,4,1,5) 0-0 - X 10,42-00 1.00012 (1,5)-0-01 4.01002 (4,5)2010 -5,01010 - abid 101010 - (5.13) -101 11 101 1 [10,11] 101 -13 1101 - (11,15) 1-11 151111 (13,15) 11-1 0, 4, 5, 10, 11, 13, 15 PZ = (6,13) bEd (10,11) aber (11,15) acd × (13,15) abc 4 (0,1.4.5) āē ~ × 🔿 EPI = F= abc + abc + ac Sop. REDMI NOTE 6 PRO abc, ac MIDUAL CAMERA, abc, acd, abc, ac

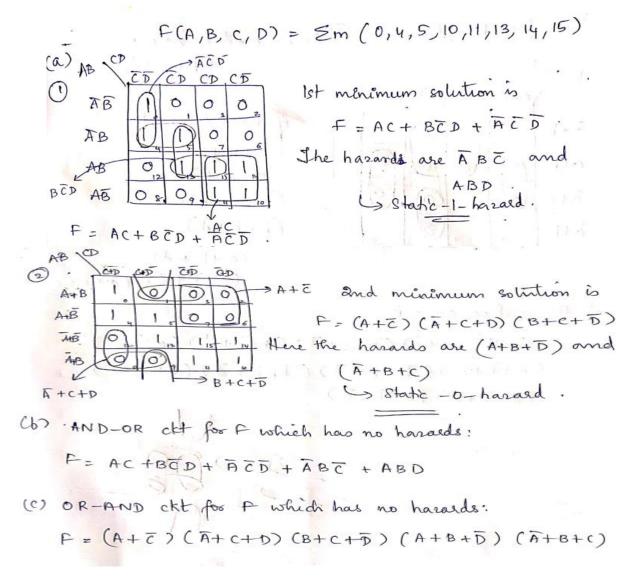

**Q.4** Consider the following logic function  $F(A, B, C, D) = \Sigma m(0,4,5,10,11,13,14,15)$ .

a) Find two different minimum circuits which implements F using AND and OR gates. Identify two hazards in each circuit.

b) Find an AND-OR circuit for F which as no hazards.

c) Find an OR- AND circuit for F which as no hazards.

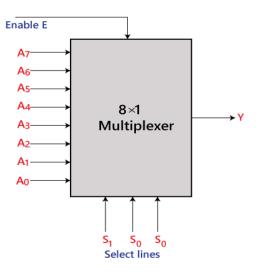

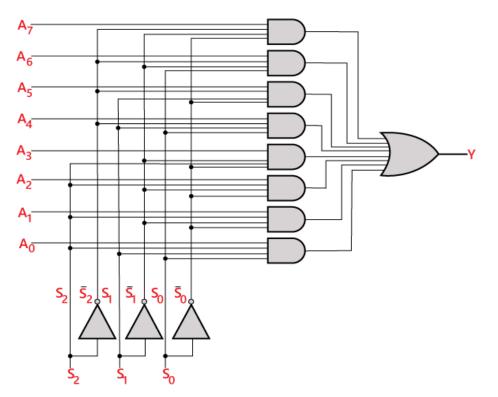

#### Q.5 What is Multiplexer? Build 8: 1 Mux using basic gates.

The multiplexer is a device that has multiple inputs and single line output. The select lines determine which input is connected to the output.

Block Diagram:

Truth Table:

|                       | INPUTS         |                |                |  |  |  |  |  |  |

|-----------------------|----------------|----------------|----------------|--|--|--|--|--|--|

| <b>S</b> <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Y              |  |  |  |  |  |  |

| 0                     | 0              | 0              | Ao             |  |  |  |  |  |  |

| 0                     | 0              | 1              | A1             |  |  |  |  |  |  |

| 0                     | 1              | 0              | A <sub>2</sub> |  |  |  |  |  |  |

| 0                     | 1              | 1              | A3             |  |  |  |  |  |  |

| 1                     | 0              | 0              | A <sub>4</sub> |  |  |  |  |  |  |

| 1                     | 0              | 1              | A <sub>5</sub> |  |  |  |  |  |  |

| 1                     | 1              | 0              | A <sub>6</sub> |  |  |  |  |  |  |

| 1                     | 1              | 1              | A <sub>7</sub> |  |  |  |  |  |  |

The logical expression of the term Y is as follows:

$Y = S_0'.S_1'.S_2'.A_0 + S_0.S_1'.S_2'.A_1 + S_0'.S_1.S_2'.A_2 + S_0.S_1.S_2'.A_3 + S_0'.S_1'.S_2 A_4 + S_0.S_1'.S_2 A_5 + S_0'.S_1.S_2 .A_6 + S_0.S_1.S_3.A_7 + S_0'.S_1'.S_2'.A_3 + S_0'.S_1'.S_2 A_4 + S_0.S_1'.S_2 A_5 + S_0'.S_1.S_2 .A_6 + S_0.S_1.S_3.A_7 + S_0'.S_1'.S_2 A_4 + S_0.S_1'.S_2 A_5 + S_0'.S_1.S_2 A_5 + S_0'.S_1.S_2 A_5 + S_0'.S_1.S_2 A_5 + S_0'.S_1 A_5 + S_0'.S_0$

Logical circuit of the above expression is given below:

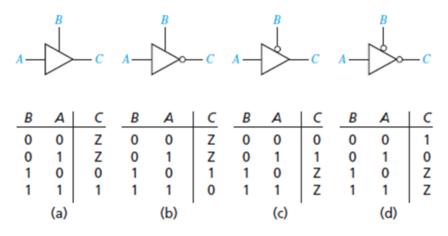

# **Q 6.** What is Buffer? Explain different three state buffers. Construct 8-to-1 MUX using two 4-to-1 MUXes, two three-state buffers, and one inverter.

A **buffer** has only a single input and a single output with behavior that is the opposite of an NOT gate. It simply passes its input, unchanged, to its output.

The following Figure shows the truth tables for four types of three-state buffers.

#### Fig: Four kinds of three state buffers

In Figures (a) and (b), the enable input B is not inverted, so the buffer output is enabled when B = 1 and disabled when B = 0. That is, the buffer operates normally when B = 1, and the buffer output is effectively an open circuit when B = 0. We use the symbol Z to represent this high-impedance state.

In Figure (b), the buffer output is inverted so that C = A' when the buffer is enabled.

The buffers in Figures (c) and (d) operate the same as in (a) and (b) except that the enable input is inverted, so the buffer is enabled when B = 0.

In the following Figure, the outputs of two three-state buffers are tied together. When B = 0, the top buffer is enabled, so that D = A; when B = 1, the lower buffer is enabled, so that D = C.