USN : \_\_\_\_\_

## CMR INSTITUTE OF TECHNOLOGY, BANGALORE DEPARTMENT OF COMPUTER SCIENCE AND ENGINEERING INTERNAL ASSESSMENT – I

Semester: 3 Subject: COMPUTER ORGANIZATION (18CS34) Faculty: Prof. Savitha S, Dr. R. Kesavamoorthy Date: 20/12/2021

Max Marks: 50

## **Instructions to Students:**

SYEARS

## ANSWER\_ANY 5 Question(s)

## Marks CO BT/CL

| Question<br># |  | Description                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Marks<br>Distribution |  |

|---------------|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|

| 1             |  | With a neat diagram, explain the basic operational concept of a computer<br>$Main memory$ $Processor-memory interface$ $PC$ $R_0$ $Control$ $R_1$ $R_{n-1}$ $ALU$ $R_{n-1}$ $R_{n-1}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |  |

|               |  |                                                                                                                                                                                       | <ul> <li>Figure 1.2 Connection between the processor and the main memory.</li> <li>The processor contains ALU, control-circuitry and many registers.</li> <li>The processor contains 'n' general-purpose registers R0 through Rn-1.</li> <li>The IR holds the instruction that currently need to be decoded and executed.</li> <li>The control-unit generates the timing-signals that determine when a given action is to take place.</li> <li>The PC contains the memory-address of the next-instruction to be fetched &amp; executed.</li> <li>During the execution of an instruction, the contents of PC are updated to point to next instruction.</li> </ul> | 2M                    |  |

| <ul> <li>The MAR holds the address of the memory-location to be accessed.</li> <li>The MDR contains the data to be written into or read out of the addressed location.</li> </ul>                                                                                                                                                                          |    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| <ul><li>Iocation.</li><li>MAR and MDR facilitate the communication with memory.</li></ul>                                                                                                                                                                                                                                                                  |    |  |

| IR –Instruction Register                                                                                                                                                                                                                                                                                                                                   |    |  |

| PC- Program counter                                                                                                                                                                                                                                                                                                                                        |    |  |

| MAR-Memory Address Register                                                                                                                                                                                                                                                                                                                                |    |  |

| MDR- Memory Data Register                                                                                                                                                                                                                                                                                                                                  |    |  |

| <ul> <li>The address of first instruction gets loaded into PC.</li> <li>The contents of PC (i.e. address) are transferred to the MAR &amp; control-unit</li> </ul>                                                                                                                                                                                         | 2M |  |

| issues Read signal to memory.                                                                                                                                                                                                                                                                                                                              |    |  |

| • After certain amount of elapsed time, the first instruction is read out of memory and placed into MDR.                                                                                                                                                                                                                                                   |    |  |

| <ul> <li>Next, the contents of MDR are transferred to IR. At this point, the instruction can be decoded &amp; executed.</li> </ul>                                                                                                                                                                                                                         |    |  |

| <ul> <li>To fetch an operand, its address is placed into MAR &amp; control-unit issues<br/>Read signal. As a result, the operand is transferred from memory into<br/>MDR, and then It is transferred from MDR to ALU. Likewise required<br/>number of operands is fetched into processor.</li> <li>Finally, ALU performs the desired operation.</li> </ul> |    |  |

|                                                                                                                                                                                                                                                                                                                                                            |    |  |

| <ul> <li>If the result of this operation is to be stored in the memory, then the result is sent to the MDR.</li> <li>The address of the location where the result is to be stored is sent to the MAR and a Write cycle is initiated.</li> </ul>                                                                                                            |    |  |

| At some point during execution, contents of PC are incremented to point to next<br>instruction in the program.                                                                                                                                                                                                                                             |    |  |

| <ul><li>Example:</li><li>An Instruction consists of 2parts, 1) Operation code (Op code) and 2)Operands.</li></ul>                                                                                                                                                                                                                                          |    |  |

| OPCODE OPERANDS                                                                                                                                                                                                                                                                                                                                            |    |  |

|                                                                                                                                                                                                                                                                                                                                                            |    |  |

| <ul> <li>The data/ operands are stored in memory.</li> <li>The individual instruction is brought from the memory to the processor.</li> <li>Then, the processor performs the specified operation.</li> <li>Let us see a typical instruction</li> </ul>                                                                                                     |    |  |

|                                                                                                                                                                                                                                                                                                                                                            |    |  |

| <ul> <li><u>ADD LOCA, R0</u></li> <li>This instruction is an addition operation. The following are the steps to</li> </ul>                                                                                                                                                                                                                                 |    |  |

| execute                                                                                                                                                                                                                                                                                                                                                    |    |  |

| the instruction:                                                                                                                                                                                                                                                                                                                                           |    |  |

| Step1: Fetch the instruction from main-memory into the processor.                                                                                                                                                                                                                                                                                          |    |  |

| Step2: Fetch the operand at location LOCA from main-memory into the processor.                                                                                                                                                                                                                                                                             |    |  |

| Step3: Add the memory operand(fetched contents of LOCA) to the contents of                                                                                                                                                                                                                                                                                 |    |  |

| register R0.                                                                                                                                                                                                                                                                                                                                               |    |  |

|    | Sten/: Store the result in BO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----|

|    | Step4: Store the result in R0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |    |

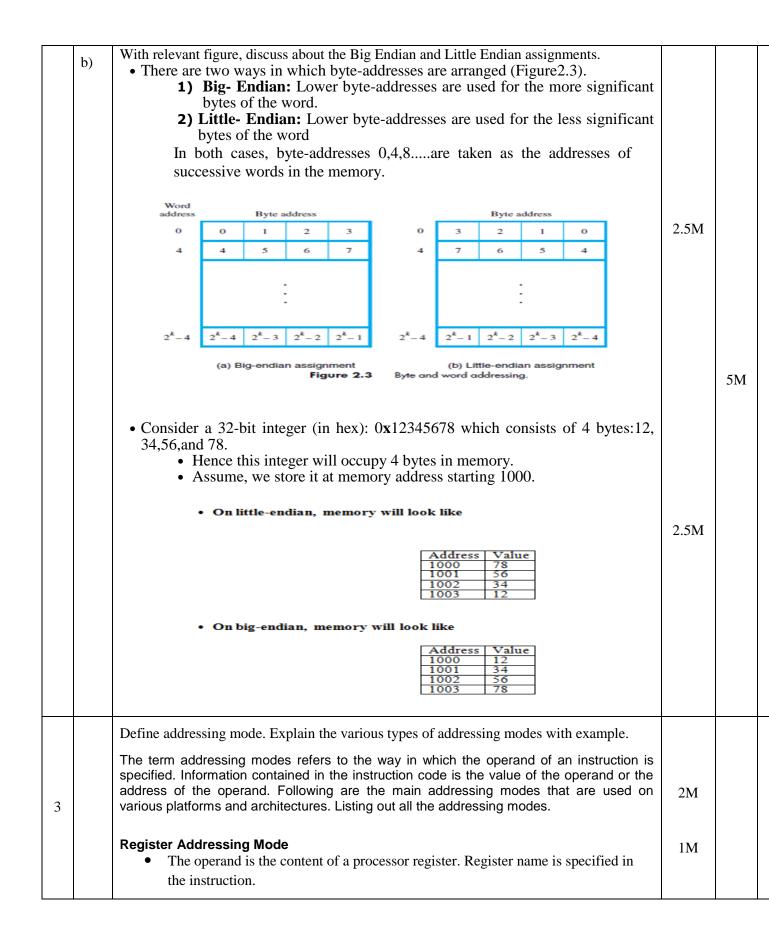

| b) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |    |

|    | <ul> <li>What is performance measurement? Explain the overall SPEC rating for the computer in a program suit.</li> <li>1 Performance measurement is the measure of how well a processor operates for a given bench mark.</li> <li>2 SPEC selects &amp; publishes the standard programs along with their test results for different application domains.(SPEC-System Performance Evaluation Corporation).</li> <li>3 SPEC Rating is given by</li> <li>SPEC Rating = (Running time of the reference Computer) / (Running time of the Computer Under test)</li> <li>If SPEC rating is 50, than computer under test is 50 times as fast as reference-computer.</li> <li>The test is repeated for all the programs in the SPEC suite.</li> <li>Then, the geometric mean of the results is computed.</li> <li>Let SPEC i=Rating for program 'i' in the suite.</li> <li>Overall SPEC rating for the computer is given by</li> <li>SPEC rating = (\prod_{i=1}^{n} SPEC_i)^{\frac{1}{2}}</li> <li>Where n= no. of programs in the suite.</li> </ul> | 2M<br>1M<br>2M       | 5M |

| a) | address processors in an accumulator organization.<br>$X = A \times B + C \times D$<br>One Address $X = A * B + C * D$ Two Address $X = A * B + C * D$ Three Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                      |    |

|    | Mov A,R1     Multiply B,R1       Load A     Multiply B,R1       MULTIPLY B     Mov C, R2       Store X     Add R1.R2       Load C     Mov R2,X       MULTIPLY D     Mov R2,X       Store Y     Load X       ADD Y     Store S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2M+<br>1.5M+<br>1.5M | 5M |

| • Effective Address of the Operand: Register name specified in the instruction                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| <b>ADD R0, R1</b> ; R1 <- R0 + R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |     |

| Immediate Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |     |

| <ul> <li>The operand is given explicitly in the instruction</li> <li>Effective Address of the Operand: Operand value given in the instruction</li> </ul>                                                                                                                                                                                                                                                                                                                                                             | 1M |     |

| <b>ADD #10, R1</b> ; R1 <- 10 + R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |     |

| Direct (or Absolute) Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |     |

| <ul> <li>The operand is a Memory location. The address of the memory location is given in the instruction explicitly.</li> <li>Effective Address of the Operand: Address of the memory location given directly in the instruction</li> </ul>                                                                                                                                                                                                                                                                         | 1M |     |

| ADD LOCA, R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |     |

| Indirect Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |     |

| <ul> <li>Here neither the operands nor the their addresses are given explicitly. The instruction provides the information from which the address of the operand is determined i.e., the instruction provides effective address of the operand using register or memory location. The indirection is denoted by () sign around register or memory.</li> <li>Effective Address of the Operand: (Ri) or (LOCA) is the contents of a register or the memory location whose address appears in the instruction</li> </ul> | 1M |     |

| Ex1: ADD LOCA, R1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |     |

| Ex2: ADD (R1), R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |     |

| Index Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |     |

| <ul> <li>The effective address of the operand is generated by adding a constant value to the contents of a register specified in the instruction. The register in this case is called as Index register.</li> <li>The operation is indicated as X(Ri).</li> <li>Effective Address of the Operand: X+Ri where X is a constant value (signed integer) and Ri is the index register.</li> </ul>                                                                                                                         | 1M | 10M |

| Ex1: ADD 5(R1), R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |     |

| Ex2: ADD 3(R1, R3), R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |     |

| Relative Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |     |

| <ul> <li>In this mode the content of the program counter is added to the address part of<br/>the instruction to obtain the effective address.</li> </ul>                                                                                                                                                                                                                                                                                                                                                             | 1M |     |

| <ul> <li>Effective Address: X+PC where X is a constant value (signed integer) and PC is</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                   |    |     |

| 1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |  |  |  |  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|    | the contents of the program counter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |  |  |  |  |

|    | Auto increment Addressing Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |  |  |  |  |

|    | <ul> <li>This is indirect mode with a modification. The effective address of the operand is the contents of a pointer register specified in the instruction. After accessing the operand, the contents of this pointer register is incremented automatically to point to the next entity.</li> <li>The mode is denoted by (Ri)+, where Ri is the pointer register.</li> <li>The + sign indicates that Ri is incremented after the operation.</li> <li>The increment operation is depending on the size of the accessed operand. Thus, the increment value is 1 for byte-size operands, 2 for word-size (16-bit) operands and 4 for long-word (32-bit) operands.</li> <li>This mode is useful when operands are stored consecutively in memory i.e., for array manipulation</li> </ul> |    |  |  |  |  |

|    | Move (R1)+, R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |  |  |  |  |

|    | Auto decrement Addressing ModeThis mode is useful to access an array in the reverse order. The value of the pointer register specified in the instruction is decremented first and this value is used as the effective address of the operand.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |  |  |  |  |

|    | <ul> <li>The mode is denoted by -(Ri), where Ri is the pointer register.</li> <li>The - sign indicates that Ri is decremented before accessing the operand.</li> <li>The decrement operation is depending on the size of the accessed operand.<br/>Thus, the decrement value is 1 for byte-size operands, 2 for word-size (16-bit) operands and 4 for long-word (32-bit) operands.</li> <li>This two modes (Autoincrement and Autodecrement) are useful to implement a data structure called Stack.</li> </ul>                                                                                                                                                                                                                                                                        | 1M |  |  |  |  |

|    | Move -(R1), R2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |  |  |  |  |

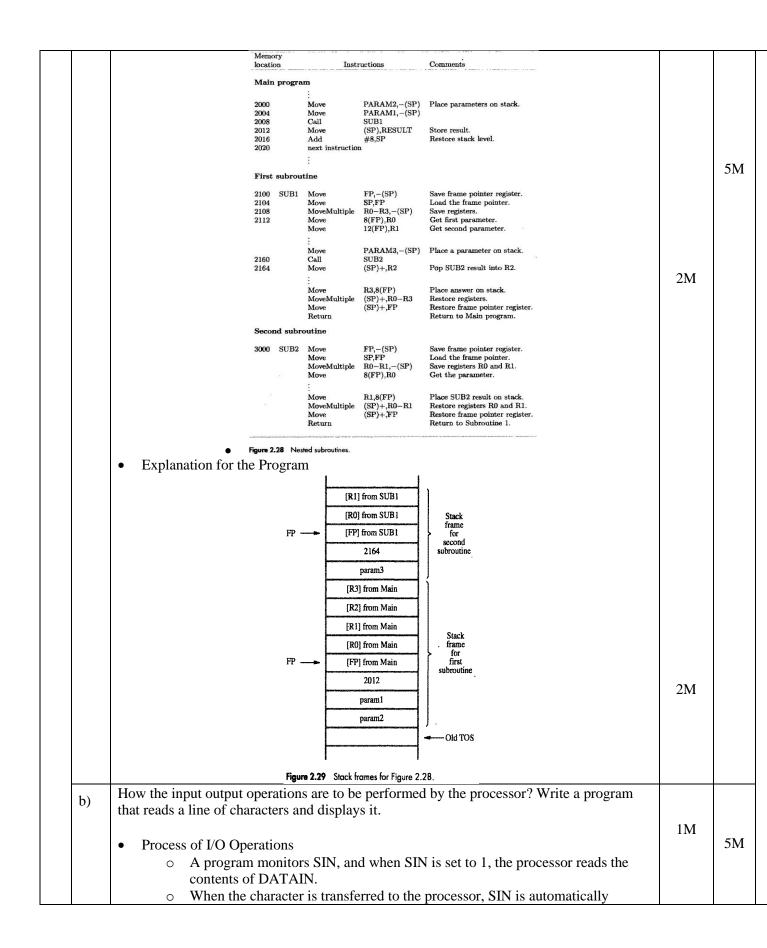

| a) | <ul> <li>Interpret the subroutine stack frame work with example.</li> <li>SP, FP and Stack Frame Stack Pointer A processor register is used to keep track of the address of the element of the stack that is at the top at any given time. This register is called the stack pointer (SP).</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |  |  |  |  |

| 4  | <ul> <li>Frame Pointer</li> <li>In addition to the stack pointer SP, it is useful to have another pointer register, called the frame pointer (FP), for convenient access to the parameters passed to the subroutine and to the local memory variables used by the subroutine.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |  |  |  |

|    | <ul> <li>Stack Frame</li> <li>During execution of the subroutine, there will be locations at the Top of the Stack that contain entries that are needed by the subroutine.</li> <li>These locations constitute a private workspace for the subroutine, that will be created at the time the subroutine is entered and freed up when the subroutine returns control to the calling program. Such space is called a stack frame.</li> </ul>                                                                                                                                                                                                                                                                                                                                              | 1M |  |  |  |  |

|    | Example Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |  |  |  |  |

|   |                                 | 1                                                                                                                           |                            |                         |                                                                                         | 1    |       |

|---|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------|-----------------------------------------------------------------------------------------|------|-------|

|   | cleared to 0.                   |                                                                                                                             |                            |                         |                                                                                         |      |       |

|   |                                 | <ul> <li>An analogous process takes place when characters are transferred from the<br/>processor to the display.</li> </ul> |                            |                         |                                                                                         |      |       |

|   |                                 |                                                                                                                             | <u> </u>                   |                         | TAOUT, and a status control flag, SOUT, are used for                                    |      |       |

|   |                                 |                                                                                                                             |                            |                         | OUT equals 1, the display is ready to receive a                                         |      |       |

|   |                                 | character.                                                                                                                  |                            |                         |                                                                                         |      |       |

|   |                                 |                                                                                                                             |                            |                         |                                                                                         |      |       |

|   |                                 | • Program                                                                                                                   |                            |                         |                                                                                         |      |       |

|   |                                 | • Explanation for the Program                                                                                               |                            |                         |                                                                                         |      |       |

|   |                                 |                                                                                                                             | Move                       | #LOC,R0                 | Initialize pointer register R0 to point to the address of the first location in memory  |      |       |

|   |                                 |                                                                                                                             |                            |                         | where the characters are to be stored.                                                  |      |       |

|   |                                 | READ                                                                                                                        | TestBit                    | #3,INSTATUS             | Wait for a character to be entered                                                      |      |       |

|   |                                 |                                                                                                                             | Branch=0                   |                         | in the keyboard buffer DATAIN.                                                          |      |       |

|   |                                 |                                                                                                                             | MoveByte                   | DATAIN,(R0)             | Transfer the character from DATAIN into<br>the memory (this clears SIN to 0).           |      |       |

|   |                                 | ECHO                                                                                                                        | TestBit                    | #3,OUTSTATUS            | Wait for the display to become ready.                                                   |      |       |

|   |                                 |                                                                                                                             | Branch=0                   | ECHO                    |                                                                                         |      |       |

| 1 |                                 |                                                                                                                             | MoveByte                   | (R0),DATAOUT            | Move the character just read to the display<br>buffer register (this clears SOUT to 0). | 2M   |       |

|   |                                 |                                                                                                                             | Compare                    | #CR,(R0)+               | Check if the character just read is CR                                                  | 2111 |       |

|   |                                 |                                                                                                                             |                            |                         | (carriage return). If it is not CR, then                                                |      |       |

|   |                                 |                                                                                                                             | Branch≠0                   | READ                    | branch back and read another character.                                                 |      |       |

|   |                                 |                                                                                                                             |                            |                         | Also, increment the pointer to store the next character.                                |      |       |

|   |                                 |                                                                                                                             |                            |                         |                                                                                         |      |       |

|   |                                 | Einen 0.0                                                                                                                   | <b>A</b>                   | 4                       |                                                                                         |      |       |

|   |                                 | rigure 2.2                                                                                                                  | • A program                | mai reads a line or chi | aracters and displays it.                                                               |      |       |

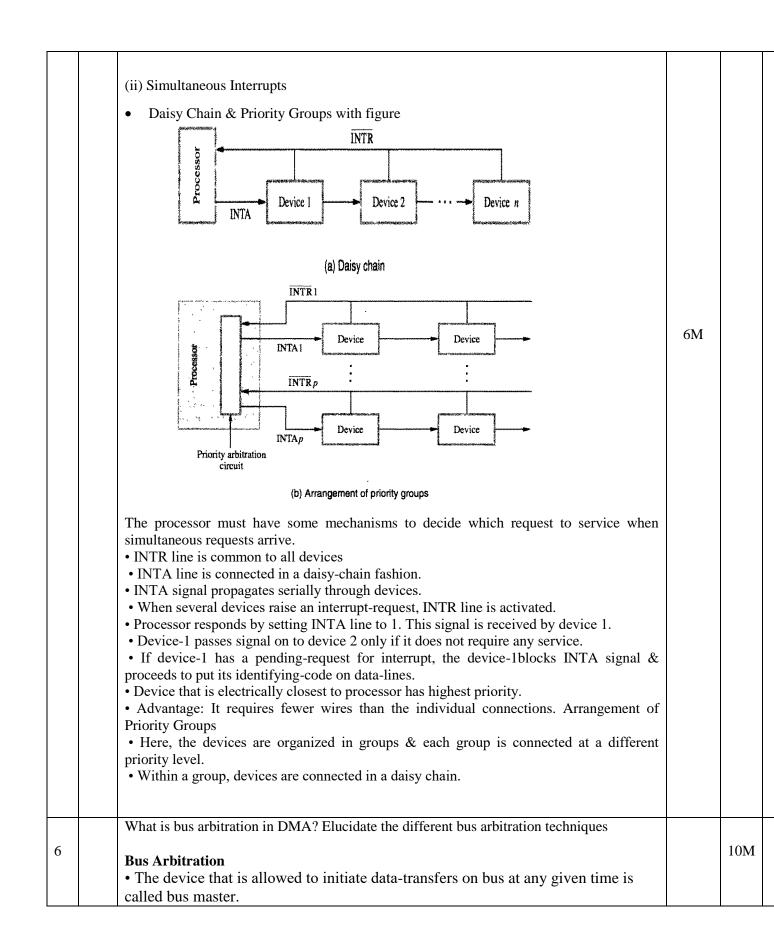

|   |                                 | Discuss                                                                                                                     | in detail a                | about                   |                                                                                         |      |       |

|   |                                 | (i) Inter                                                                                                                   | rupt Nesti                 | ng                      |                                                                                         |      |       |

|   |                                 | Drie                                                                                                                        | wity Schor                 | ne with figure          |                                                                                         |      |       |

|   |                                 | • FIIC                                                                                                                      | •                          | U                       | rocessor is the priority of the program being executed.                                 |      |       |

|   |                                 |                                                                                                                             |                            | -                       | ty of the device whose ISR is being executed                                            |      |       |

|   |                                 |                                                                                                                             |                            | -                       | ices with same level or low level of priority                                           |      |       |

|   |                                 |                                                                                                                             |                            |                         |                                                                                         |      |       |

|   |                                 |                                                                                                                             | <ul> <li>Accept</li> </ul> | pt IR from devic        | es with higher priority.                                                                |      |       |

| 5 |                                 |                                                                                                                             |                            |                         |                                                                                         |      | 10M   |

| 5 |                                 |                                                                                                                             |                            |                         |                                                                                         |      | 10101 |

|   |                                 |                                                                                                                             |                            |                         | NTR1 INTR <i>p</i>                                                                      |      |       |

|   |                                 | Direstan                                                                                                                    |                            |                         | inelandasi bunani -anananinani -anan bu                                                 | 4M   |       |

|   |                                 |                                                                                                                             |                            | Device                  | $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                  |      |       |

|   |                                 | <u>م</u>                                                                                                                    |                            |                         | INTA I                                                                                  |      |       |

|   |                                 |                                                                                                                             |                            |                         |                                                                                         |      |       |

|   |                                 |                                                                                                                             |                            |                         |                                                                                         |      |       |

| 1 | Priority arbitration<br>circuit |                                                                                                                             |                            |                         |                                                                                         |      |       |

| 1 |                                 |                                                                                                                             |                            |                         |                                                                                         |      |       |

| 1 |                                 | Figure 4.7 Implementation of interrupt priority using individual interrupt-request and<br>acknowledge lines.                |                            |                         |                                                                                         |      |       |

|   |                                 |                                                                                                                             |                            |                         |                                                                                         |      |       |

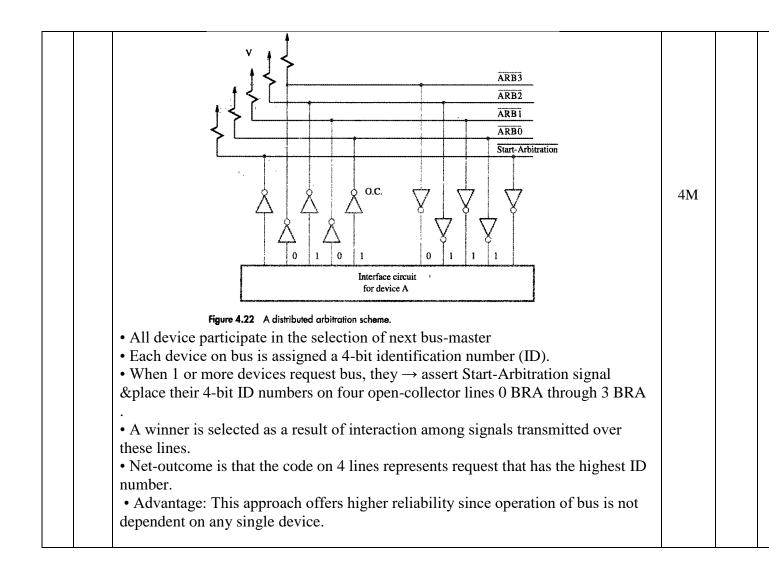

• There can be only one bus-master at any given time. • Bus Arbitration is the process by which next device to become the bus-master is selected &bus-mastership is transferred to that device. 2M **Centralized Method with figure** BBSY BR Processor DMA DMA controller controller BG1 BG2 1 2 Figure 4.20 A simple arrangement for bus arbitration using a daisy chain. 4MA single bus-arbiter performs the required arbitration. • Normally, processor is the bus-master. • Processor may grant bus-mastership to one of the DMA controllers. • A DMA controller indicates that it needs to become bus-master by activating BR line. • The signal on the BR line is the logical OR of bus-requests from all devices connected to it. • Then, processor activates BG1 signal indicating to DMA controllers to use bus when it becomes free. • BG1 signal is connected to all DMA controllers using a daisy-chain arrangement. • If DMA controller-1 is requesting the bus, Then, DMA controller-1 blocks propagation of grant-signal to other devices. Otherwise, DMA controller-1 passes the grant downstream by asserting BG2. • Current bus-master indicates to all devices that it is using bus by activating BBSY line. • The bus-arbiter is used to coordinate the activities of all devices requesting memory transfers. • Arbiter ensures that only 1 request is granted at any given time according to a priority scheme. (BR-Bus-Request, BG-Bus-Grant, BBSY-Bus Busy). **Distributed Method with figure**