| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

Internal Assessment Test 2 – January 2022

| Sub:  | Analog and D | Analog and Digital Electronics Sub Code: 18CS33 Bra |             |                    |              |                     |        |  |     |     |

|-------|--------------|-----------------------------------------------------|-------------|--------------------|--------------|---------------------|--------|--|-----|-----|

| Date: | 25/1/2022    | Duration:                                           | 90 min's    | Max Marks: 50      | Sem/Sec:     | 3 <sup>rd</sup> / A | A,B,C  |  | OB  | Е   |

|       |              |                                                     |             | E FULL Questions   |              |                     | MAR    |  |     | RBT |

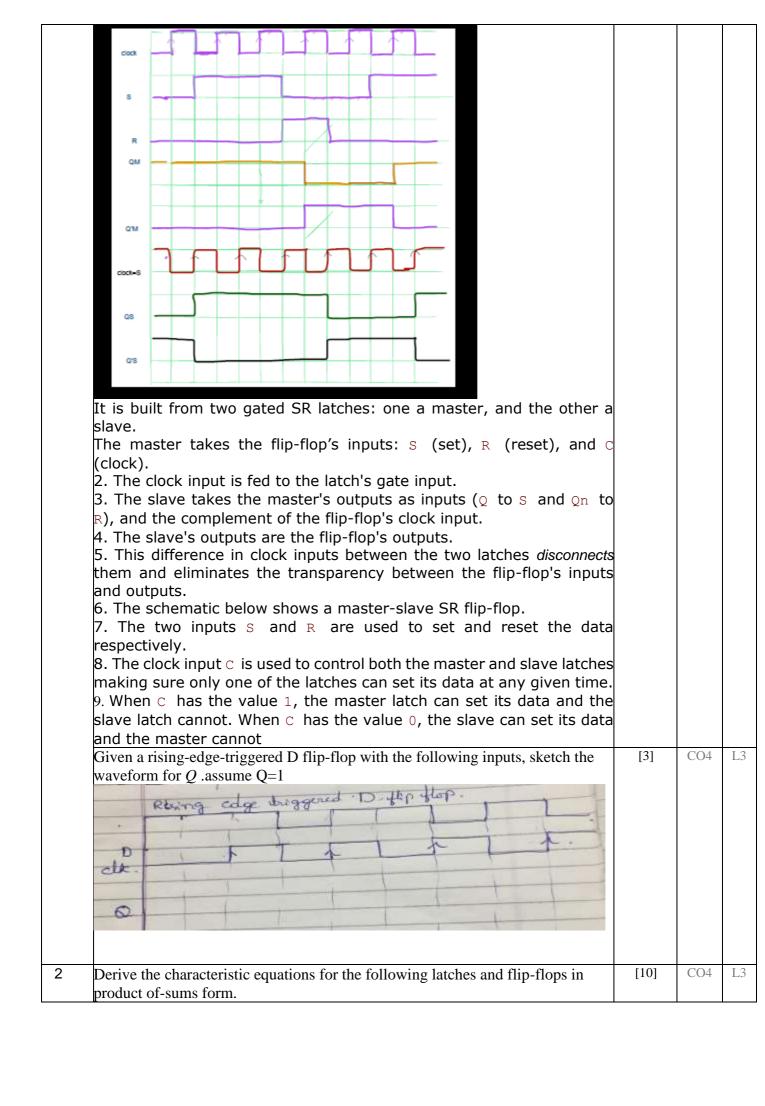

| 1 (a) |              | operation of                                        | master and  | slave JK flip flop | with truth t | able and timi       | ng [7] |  | CO4 | L4  |

|       | diagram      |                                                     |             |                    |              |                     |        |  |     |     |

|       | ANS:         | Acotor Clay                                         | o CD Flip f | lon                |              |                     |        |  |     |     |

|       | IV.          | laster Slav                                         | e SK Filp I | юр                 |              |                     |        |  |     |     |

|       | S            | R Q                                                 | Qnext       | $Q_{next}'$        |              |                     |        |  |     |     |

|       | 0            | 0 0                                                 |             | 1                  |              |                     |        |  |     |     |

| (b)   | 0            | 0 1                                                 | 1           | 0                  |              |                     |        |  |     |     |

|       | 0            | 1 0                                                 | 0           | 1                  |              |                     |        |  |     |     |

|       | 0            | 1 1                                                 | 0           | 1                  |              |                     |        |  |     |     |

|       | 1            | 0 0                                                 | 1           | 0                  |              |                     |        |  |     |     |

|       | 1            | 0 1                                                 | 1           | 0                  |              |                     |        |  |     |     |

|       | 1            | 1 0                                                 | ×           | ×                  |              |                     |        |  |     |     |

|       | 1            | 1 1                                                 | ×           | ×                  |              |                     |        |  |     |     |

|       |              | Tru                                                 | th Table    |                    |              |                     |        |  |     |     |

|       | S            |                                                     | a,          |                    | -1           |                     |        |  |     |     |

|       | 576 EG       | - s                                                 | a           | S                  | ۵            | -                   |        |  |     |     |

|       | CLOCK _      | CLK                                                 |             | CLK                |              |                     |        |  |     |     |

|       | R            | _ R                                                 | α           | R                  | <u>a</u>     |                     |        |  |     |     |

|       |              |                                                     | <b>-</b>    |                    |              |                     |        |  |     |     |

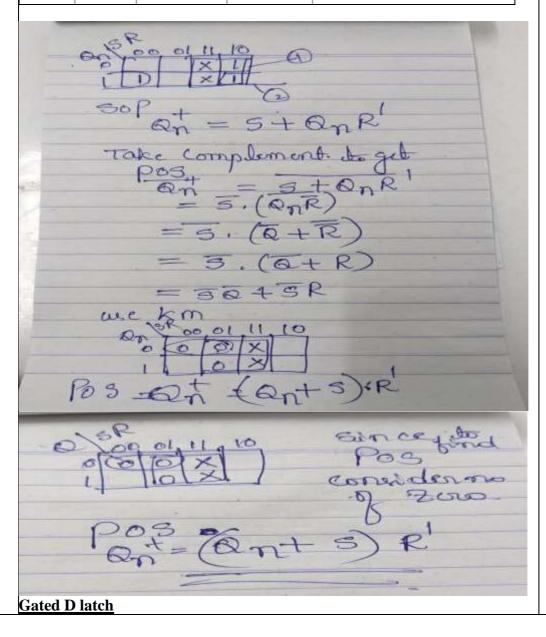

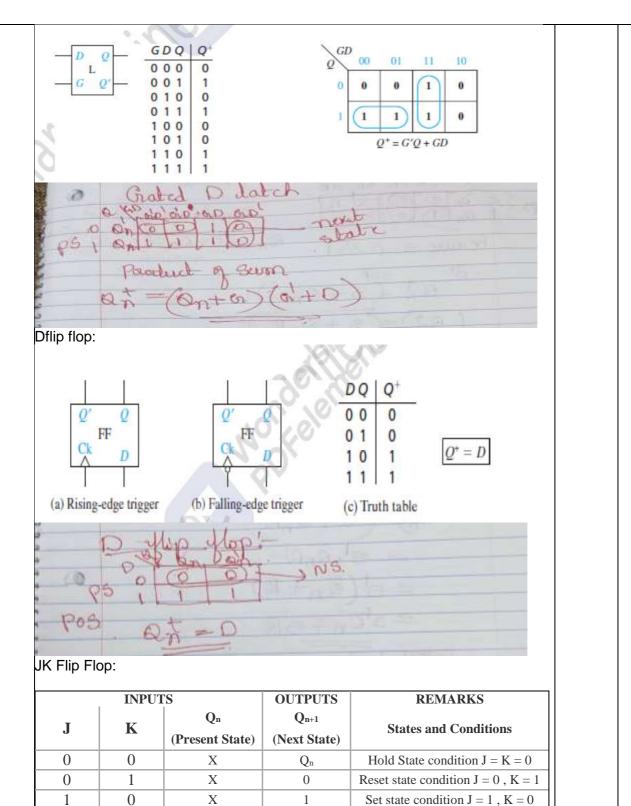

- (a) S-R latch or flip-flop

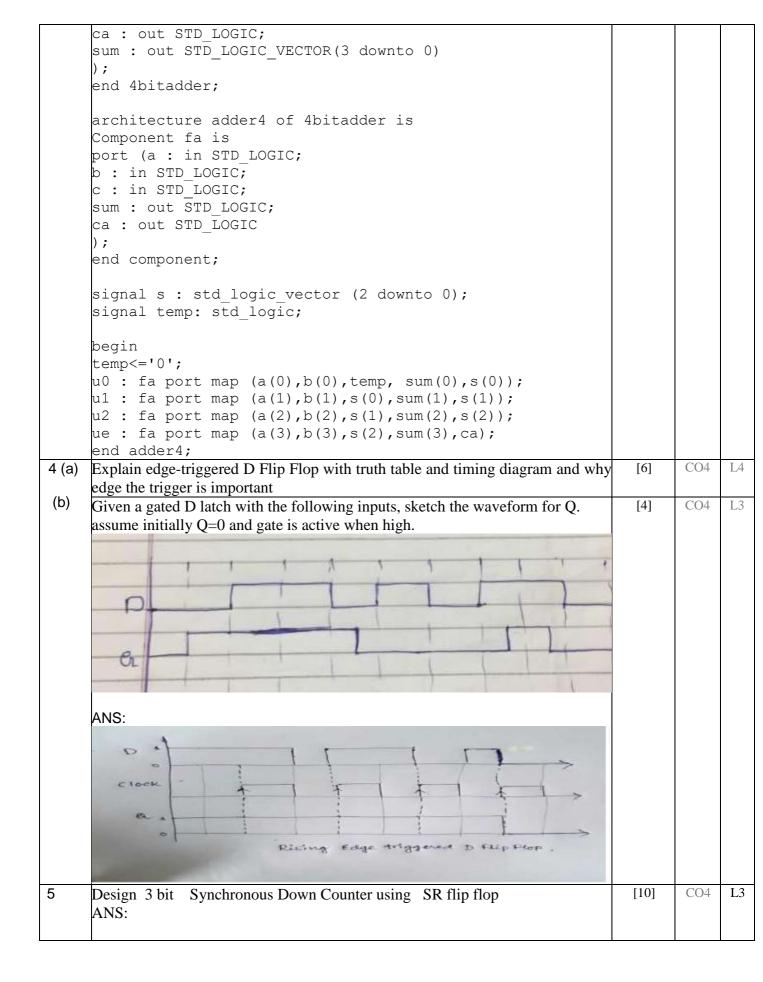

- (b) Gated D latch

- (c) D flip-flop

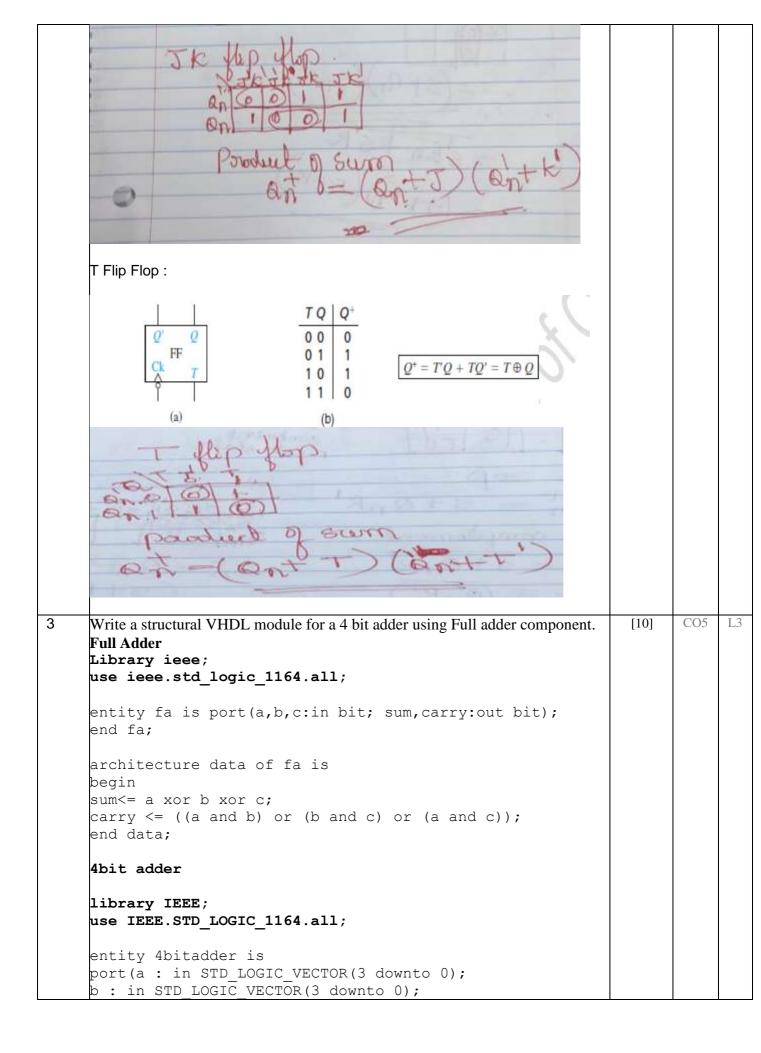

- (d) J-K flip-flop

- (e) T flip-flop

ANS:

|   | INPUT | TS .               | OUTPUTS           | REMARKS                                   |

|---|-------|--------------------|-------------------|-------------------------------------------|

|   |       | Qn                 | Q <sub>n+1</sub>  |                                           |

| S | R     | (Present<br>State) | (Next State)      | States and Conditions                     |

| 0 | 0     | X                  | Qn                | Hold State condition $S = R = 0$          |

| 0 | 1     | X                  | 0                 | Reset state condition $S = 0$ , $R = 1$   |

| 1 | 0     | X                  | 1                 | Set state condition $S = 1$ , $R = 0$     |

| 1 | 1     | X                  | Indeterminat<br>e | Indeterminate state condition $S = R = 1$ |

$Q'_n$

Toggle state condition J = K = 1

1

1

X

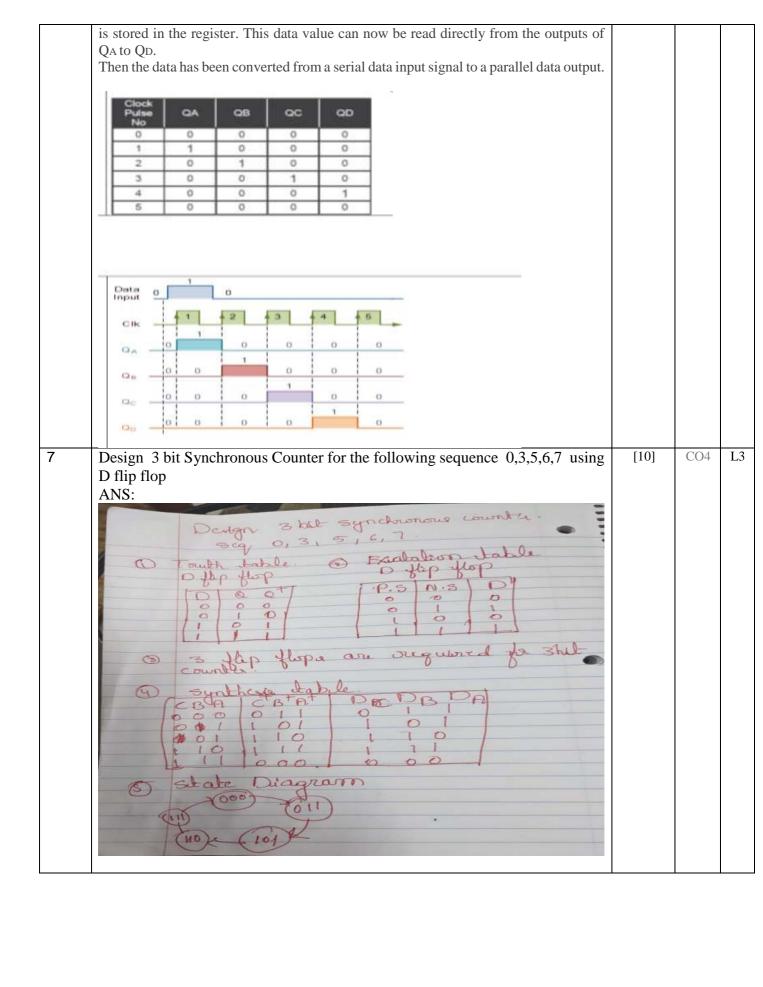

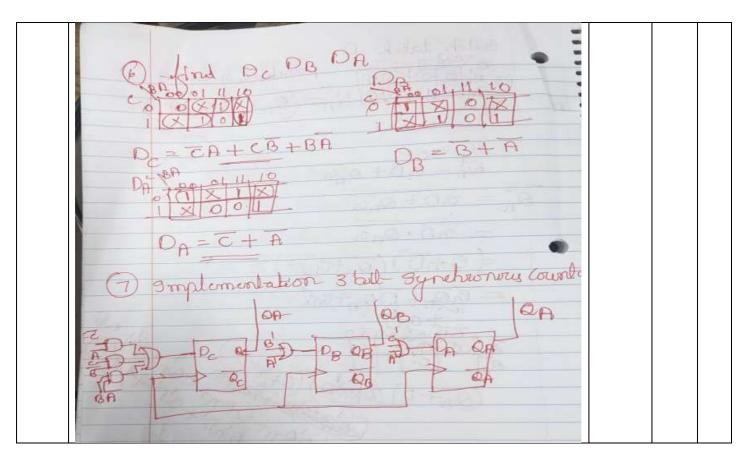

Write neat Sketch and Explain the working principle of Serial in parallel out(

SIPO with timing Diagram

## ANS:

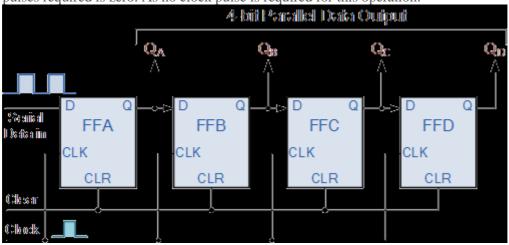

**Serial-in to Parallel-out (SIPO)** - the register is loaded with serial data, one bit at a time, with the stored data being available at the output in parallel form. For 'n' bit serial input data which need to be stored, the number of clock pulses required is equal to 'n'. and For 'n' bit parallel output data that need to be stored, the number of clock pulses required is zero. As no clock pulse is required for this operation.

The operation is as follows. Let's assume that all the flip-flops ( FFA to FFD ) have just been RESET ( CLEAR input ) and that all the outputs QA to QD are at logic level "0" ie, no parallel data output.

If a logic "1" is connected to the DATA input pin of FFA then on the first clock pulse the output of FFA and therefore the resulting QA will be set HIGH to logic "1" with all the other outputs still remaining LOW at logic "0". Assume now that the DATA input pin of FFA has returned LOW again to logic "0" giving us one data pulse or 0-1-0.

The second clock pulse will change the output of FFA to logic "0" and the output of FFB and QB HIGH to logic "1" as its input D has the logic "1" level on it from QA. The logic "1" has now moved or been "shifted" one place along the register to the right as it is now at QA.

When the third clock pulse arrives this logic "1" value moves to the output of FFC (QC) and so on until the arrival of the fifth clock pulse which sets all the outputs QA to QD back again to logic level "0" because the input to FFA has remained constant at logic level "0".

The effect of each clock pulse is to shift the data contents of each stage one place to the right, and this is shown in the following table until the complete data value of 0-0-0-1

[10]

CO4 L4,

| Course Outcomes |                                                                                                                                         | Modul<br>es<br>covere<br>d | P<br>O<br>1 | P<br>O<br>2 | P<br>O<br>3 | P<br>O<br>4 | P<br>O<br>5 |   |   | P<br>O<br>7 | P<br>O<br>8 | P<br>O<br>9 | P<br>O<br>1<br>0 | P<br>O<br>1 | P<br>O<br>1<br>2 | P<br>S<br>O<br>1 | P<br>S<br>O<br>2 | P<br>S<br>O<br>3 | P<br>S<br>O<br>4 |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------|-------------|-------------|-------------|-------------|---|---|-------------|-------------|-------------|------------------|-------------|------------------|------------------|------------------|------------------|------------------|

| CO1             | Design and analyze application of analog circuits using photo devices, timer IC, power supplyand regulator IC and op-amp.               | 1                          | 2           | 3           | 3           | 2           | 2           | 0 | 0 | 0           | 0           | 0           | 0                | 0           | 0                | 2                | 0                | 2                | 2                |

| CO2             | Explain the basic principles of A/D and D/A conversion circuits and develop the same                                                    | 1                          | 2           | 2           | 3           | 2           | 2           | 0 | 0 | 0           | 0           | 0           | 0                | 0           | 0                | 2                | 0                | 2                | 2                |

| CO3             | Simplify digital circuits using Karnaugh Map , and Quine-McClusky Methods                                                               | 2                          | 2           | 3           | 3           | 3           | 2           | 0 | 0 | 0           | 0           | 0           | 0                | 0           | 0                | 2                | 0                | 2                | 2                |

| CO4             | Explain Gates and flip flops and make us in designing different data processing circuits, registers and counters and compare the types. | 3, 4, 5                    | 2           | 3           | 3           | 3           | 3           | 0 | 0 | 0           | 0           | 0           | 0                | 0           | 0                | 2                | 0                | 2                | 2                |

| CO5             | Develop simple HDL programs                                                                                                             | 3, 4, 5                    | 1           | 1           | 1           | 1           | 3           | 0 | 0 | 0           | 0           | 0           | 0                | 0           | 0                | 2                | 0                | 2                | 1                |

| COGNITIVE<br>LEVEL | REVISED BLOOMS TAXONOMY KEYWORDS                                                                                                              |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| L1                 | List, define, tell, describe, identify, show, label, collect, examine, tabulate, quote, name, who, when, where, etc.                          |

| L2                 | summarize, describe, interpret, contrast, predict, associate, distinguish, estimate, differentiate, discuss, extend                           |

| L3                 | Apply, demonstrate, calculate, complete, illustrate, show, solve, examine, modify, relate, change, classify, experiment, discover.            |

| L4                 | Analyze, separate, order, explain, connect, classify, arrange, divide, compare, select, explain, infer.                                       |

| L5                 | Assess, decide, rank, grade, test, measure, recommend, convince, select, judge, explain, discriminate, support, conclude, compare, summarize. |

| Pl   |                                                                                          | CORRELATION<br>LEVELS                  |                                    |                      |                     |  |  |  |  |

|------|------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------|----------------------|---------------------|--|--|--|--|

| PO1  | Engineering knowledge                                                                    | PO7                                    | Environment and sustainability     | 0                    | No Correlation      |  |  |  |  |

| PO2  | Problem analysis                                                                         | PO8                                    | Ethics                             | 1                    | Slight/Low          |  |  |  |  |

| PO3  | Design/development of solutions                                                          | solutions PO9 Individual and team work |                                    |                      | Moderate/<br>Medium |  |  |  |  |

| PO4  | Conduct investigations of complex problems PO10 Communication                            |                                        | 3                                  | Substantial/<br>High |                     |  |  |  |  |

| PO5  | Modern tool usage                                                                        |                                        |                                    |                      |                     |  |  |  |  |

| PO6  | The Engineer and society                                                                 | PO12                                   | Life-long learning                 |                      |                     |  |  |  |  |

| PSO1 | Develop applications using differe                                                       | nt stacks                              | of web and programming technologic | es                   |                     |  |  |  |  |

| PSO2 | Design and develop secure, parallel, distributed, networked, and digital systems         |                                        |                                    |                      |                     |  |  |  |  |

| PSO3 | Apply software engineering methods to design, develop, test and manage software systems. |                                        |                                    |                      |                     |  |  |  |  |

| PSO4 | Develop intelligent applications for business and industry                               |                                        |                                    |                      |                     |  |  |  |  |