| USN   | N                                                                                                                        | * CMR INSTITUTE OF | *.  CM  TECHNOLOGY, E | RIT<br>ENGALURU.<br>BY NAAC |

|-------|--------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-----------------------------|

|       | Internal Assessment Test 2 – January 2022                                                                                |                    |                       |                             |

| Sub:  | Analog and Digital Electronics Sub Code: 18CS33 Bra                                                                      | nch: ISE           |                       |                             |

| Date: | 25/1/2022 Duration: 90 min's Max Marks: 50 Sem/Sec: III / A, B and C                                                     | •                  | OE                    | BE .                        |

|       | Answer any FIVE FULL Questions                                                                                           | MARKS              | CO                    | RBT                         |

| 1     | Explain the structure of VHDL Program. Write VHDL Code for 4-bit parallel adder.                                         | 10                 | CO5                   | L2                          |

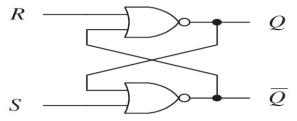

| 2     | Construct SR latch using NOR gate. Show how SR latch can be used for switch debouncing.                                  | 10                 | CO4                   | L3                          |

| 3     | a. With an example, explain the syntax of conditional signal assignment statement in VHDL.                               | 4                  | CO5                   | L2                          |

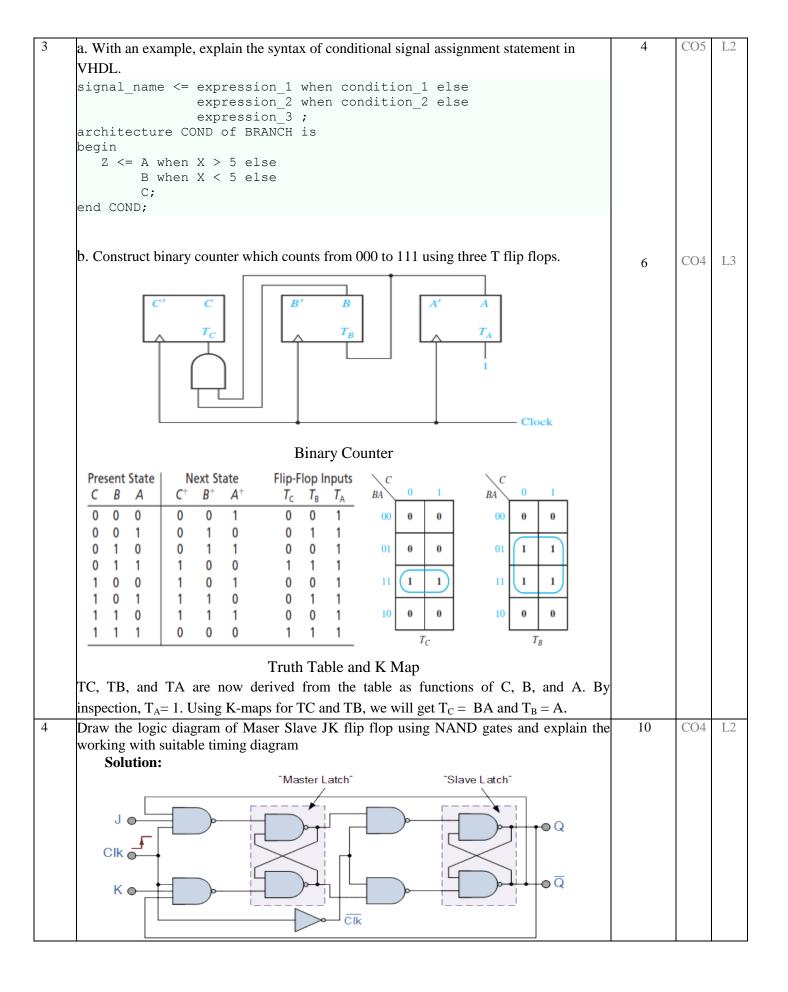

|       | b. Construct binary counter which counts from 000 to 111 using three T flip flops.                                       | 6                  | CO4                   | L3                          |

| 4     | Draw the logic diagram of Maser Slave JK flip flop using NAND gates and explain the working with suitable timing diagram | 10                 | CO4                   | L2                          |

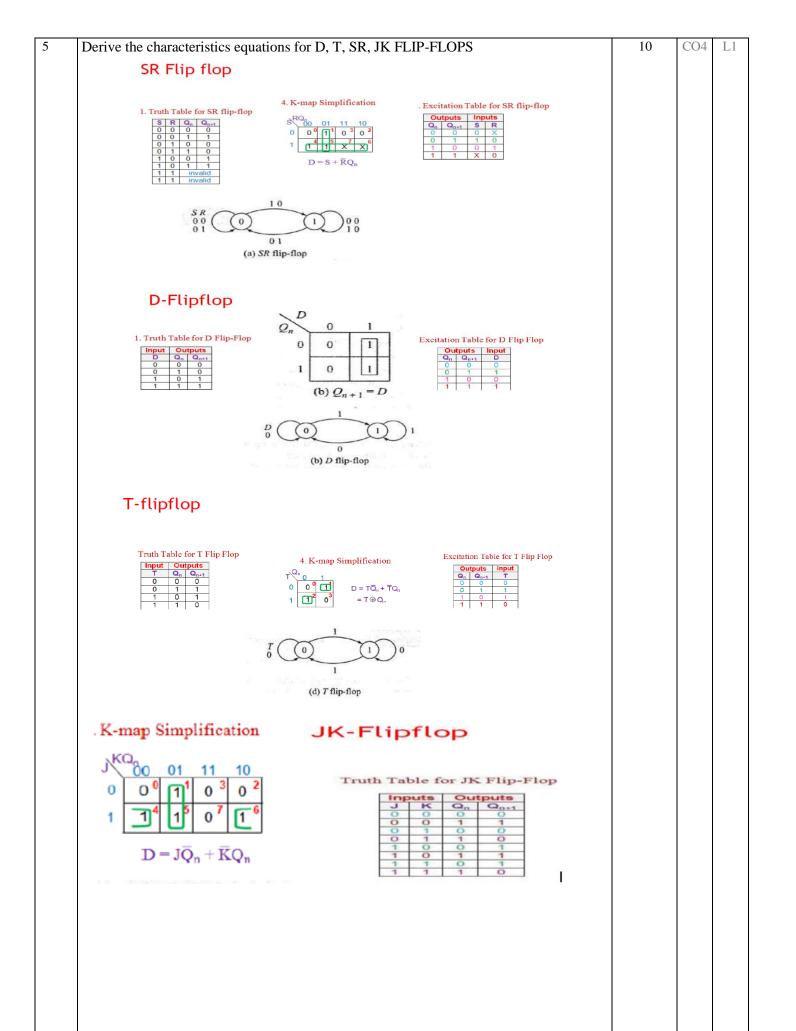

| 5     | Derive the characteristics equations for D, T, SR, JK FLIP-FLOPS                                                         | 10                 | CO4                   | L1                          |

| 6     | With neat sketch, explain the working principle of SISO & PIPO shift register.                                           | 10                 | CO4                   | L2                          |

Faculty Signature CCI Signature HOD Signature

| USN   | N                                                                                                                        |                |             |               |              |             |                |      | * CELEBRAIN  * CELEBRAIN  * CELEBRAIN | NSTITUTE OF | **:  CM  TECHNOLOGY, E  TH A+ GRADE | RIT<br>BENGALURU.<br>BY NAAC |

|-------|--------------------------------------------------------------------------------------------------------------------------|----------------|-------------|---------------|--------------|-------------|----------------|------|---------------------------------------|-------------|-------------------------------------|------------------------------|

|       |                                                                                                                          |                | Internal A  | Assessment Te | est 2        | – January 2 | 2022           |      |                                       |             |                                     |                              |

| Sub:  | Analog and Di                                                                                                            | gital Electron | ics         |               |              | Sub Code:   | 18CS33         | Brai | nch:                                  | ISE         |                                     |                              |

| Date: | 25/1/2022                                                                                                                | Duration:      | 90 min's    | Max Marks:    | 50           | Sem/Sec:    | III / A, B and | С    |                                       |             | OF                                  | BE                           |

|       |                                                                                                                          | <u>An</u>      | swer any FI | VE FULL Quest | <u>tions</u> |             |                |      | MAR                                   | RKS         | CO                                  | RBT                          |

| 1     | Explain the structure of VHDL Program. Write VHDL Code for 4-bit parallel adder.                                         |                |             |               |              |             |                |      | 10                                    | 0           | CO5                                 | L2                           |

| 2     | Construct SR latch using NOR gate. Show how SR latch can be used for switch debouncing.                                  |                |             |               |              |             |                |      | 0                                     | CO4         | L3                                  |                              |

| 3     | a. With an example, explain the syntax of conditional signal assignment statement in VHDL.                               |                |             |               |              |             |                | 4    | _                                     | CO5         | L2                                  |                              |

|       | b. Construct binary counter which counts from 000 to 111 using three T flip flops.                                       |                |             |               |              |             |                |      | 6                                     | )           | CO4                                 | L3                           |

| 4     | Draw the logic diagram of Maser Slave JK flip flop using NAND gates and explain the working with suitable timing diagram |                |             |               |              |             |                |      | 0                                     | CO4         | L2                                  |                              |

| 5     | Derive the characteristics equations for D, T, SR, JK FLIP-FLOPS                                                         |                |             |               |              |             |                |      | 10                                    | 0           | CO4                                 | L1                           |

| 6     | With neat sketch, explain the working principle of SISO & PIPO shift register.                                           |                |             |               |              |             |                |      | 10                                    | 0           | CO4                                 | L2                           |

Faculty Signature

CCI Signature

HOD Signature

USN

MARKS CO

| Internal   | Assessment       | Test 2 – | Ianuary | 7 2022 |

|------------|------------------|----------|---------|--------|

| militarian | 1 10000001110110 | 10502    | Juliuui | , 2022 |

| Sub:  | Analog and Di | gital Electron | Sub Code: | 18CS33     | Branch: | ISE      |                |   |  |     |

|-------|---------------|----------------|-----------|------------|---------|----------|----------------|---|--|-----|

| Date: | 25/1/2022     | Duration:      | 90 min's  | Max Marks: | 50      | Sem/Sec: | III / A, B and | С |  | OBE |

**Answer any FIVE FULL Questions** Explain the structure of VHDL Program. Write VHDL Code for 4-bit parallel adder...

## **Solution:**

When we describe a system in VHDL, we must specify an entity and an architecture at the top level, and also specify an entity and architecture for each of the component modules that are part of the system. Each entity declaration includes a list of interface signals that can be used to connect to other

modules or to the outside world. We will use entity declarations of the form:

entity entity-name is [port(interface-signal-declaration);] end [entity] [entity-name];

The items enclosed in square brackets are optional. The interfacesignal-declaration normally has the following form: list-of-interface-signals: mode type [: initial-value]

{; list-of-interface-signals: mode type [: \_ initial-value]};

# **Entity** Architecture

Entity Architecture

Module 1

Entity Architecture

Module 2

Entity Architecture

Module N

VHDL Program Structure

entity Adder4 is

port (A, B: in bit vector(3 downto 0); Ci: in bit; -- Inputs

S: out bit\_vector(3 downto 0); Co: out bit); -- Outputs

end Adder4:

architecture Structure of Adder4 is

component FullAdder

port (X, Y, Cin: in bit; - Inputs

Cout, Sum: out bit); -- Outputs

end component;

signal C: bit vector(3 downto 1);

begin -- instantiate four copies of the FullAdder

FAO: FullAdder port map (A(0), B(0), Ci, C(1), S(0));

FA1: FullAdder port map (A(1), B(1), C(1), C(2), S(1));

FA2: FullAdder port map (A(2), B(2), C(2), C(3), S(2));

FA3: FullAdder port map (A(3), B(3), C(3), Co, S(3));

end Structure:

**Solution:**

From this, the flip-flop has two inputs: R and S and two outputs: Q and Q and it is clear from the representation that the outputs are complementary to each other. Let us try to analyze the different possibilities of inputs and their corresponding outputs.

An important point to note here is that for a NOR gate, Logic '1' is a dominating input and if any one of its input is Logic '1' (HIGH), then the output is Logic '0' (LOW), irrespective of the other input. With this in mind, let us analyze the above circuit.

## Case 1: R = 0 and S = 0

In the first case, the inputs of both the NOR gates are Logic '0'. As neither of them are dominating inputs, they have no effect on the output. So, the output retains their previous states i.e., there is no change in the output. This condition is called as Hold Condition or No Change Condition.

## Case 2: R = 0 and S = 1

In this case, the 'S' input is 1, which means the output of the NOR Gate B will become 0. As a result, both the inputs of NOR Gate A become 0 and hence the output of the NOR Gate A and thus the value of Q is 1 (HIGH). As '1' at input S makes the output to switch to one of its stable states and sets it to '1', the S input is known as SET input.

### Case 3: R = 1 and S = 0

In this case, the 'R' input is 1, which means the output of the NOR Gate A will become 0 i.e., Q is 0 (LOW). As a result, both the inputs of NOR Gate B become 0 and hence the output of the NOR Gate B is 1 (HIGH). As '1' at input R makes the output to switch to one of its stable states and resets it to '0', the R input is known as RESET input.

#### Case 4: R = 1 and S = 1

This input condition is forbidden as it forces outputs of both NOR Gates to become 0, which is a violation of complementary outputs. Even if this input condition is applied, if the next inputs become R = 0 and S = 0 (hold condition), then it causes a 'race condition' between the NOR Gates, which causes an unstable or unpredictable state at the output. Hence, the input condition R = 1 and S = 1 is simply not used.

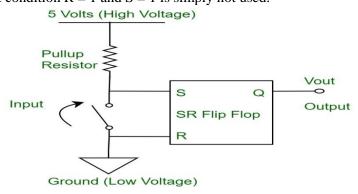

#### **Switch Debouncing**

Use of S-R Flip Flop Latch circuit. The circuit when introduced in the output part of the switch, it will retain the voltage level of the input as the output state. Thus, latching to the input, when change in state is introduced. This method is useful, but adds to the bulkiness of the simple circuit.

| Inp                      | uts           |                 | Out                                    | puts                                                                                            |                                                                                                                                                                                                                                                                                                                        |  |  |

|--------------------------|---------------|-----------------|----------------------------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| The second second second |               | K               | $Q_{n+1}$                              | $\bar{Q}_{n+1}$                                                                                 | Remark                                                                                                                                                                                                                                                                                                                 |  |  |

| ×                        | 0             | 0               | Qn                                     | $\bar{Q}_n$                                                                                     | No change                                                                                                                                                                                                                                                                                                              |  |  |

| (1)                      | 0             | 0               | Q <sub>n</sub>                         | Q,                                                                                              | No change                                                                                                                                                                                                                                                                                                              |  |  |

| (1)                      | 0             | 1               | 0                                      | 1                                                                                               | Reset                                                                                                                                                                                                                                                                                                                  |  |  |

| (1)                      | 1             | 0               | 1                                      | 0                                                                                               | Set                                                                                                                                                                                                                                                                                                                    |  |  |

| (I)                      | 1             | 1               | $\bar{Q}_n$                            | Qn                                                                                              | Toggle                                                                                                                                                                                                                                                                                                                 |  |  |

|                          | × (1) (1) (1) | × 0 (1) 0 (1) 1 | CLK J K  × 0 0 (1) 0 0 (1) 0 1 (1) 1 0 | CLK J K Q <sub>n+1</sub> × 0 0 Q <sub>n</sub> ——(1) 0 0 Q <sub>n</sub> ——(1) 1 0 1  ——(1) 1 1 - | CLK         J         K $Q_{n+1}$ $\overline{Q}_{n+1}$ ×         0         0 $Q_n$ $\overline{Q}_n$ \( \subseteq \text{(1)}\)         0         0 $Q_n$ $\overline{Q}_n$ \( \subseteq \text{(1)}\)         0         1         0         1           \( \subseteq \text{(1)}\)         1         0         1         0 |  |  |

Truth table of Master slave JK FF

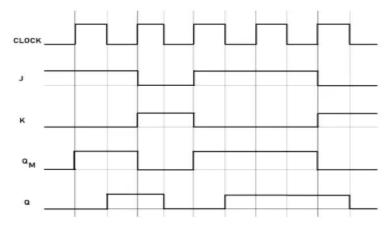

When the clock pulse is true, the slave flip flop will be in the isolated state, and the system's state may be affected by the J and K inputs. The "slave" remains isolated until the CP is 1. When the CP set to 0, the master flip-flop passes the information to the slave flip flop to obtain the output.

The master flip flop responds first from the slave because the master flip flop is the positive level trigger, and the slave flip flop is the negative level trigger.

The output Q'=1 of the master flip flop is passed to the slave flip flop as an input K when the input J set to 0 and K set to 1. The clock forces the slave flip flop to work as reset, and then the slave copies the master flip flop.

When J=1, and K=0, the output Q=1 is passed to the J input of the slave. The clock's negative transition sets the slave and copies the master.

The master flip flop toggles on the clock's positive transition when the inputs J and K set to 1. At that time, the slave flip flop toggles on the clock's negative transition.

The flip flop will be disabled, and Q remains unchanged when both the inputs of the JK flip flop set to 0

## **Solution:**

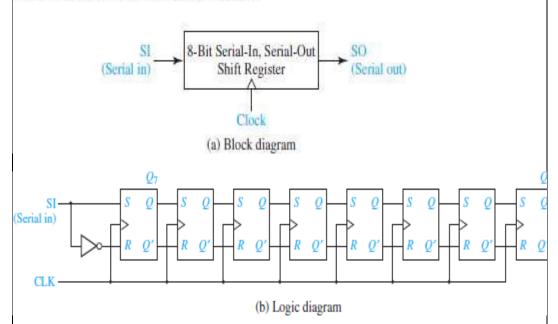

8-Bit Serial-in, Serial-out Shift Register

The following Figure

illustrates an 8-bit serial-in, serial-out shift register. Serial in means that data is shifted into the first flipflop

one bit at a time, and the flip-flops cannot be loaded in parallel. Serial out means that data can only

be read out of the last flip-flop and the outputs from the other flip-flops are not connected to terminals of

the integrated circuit.

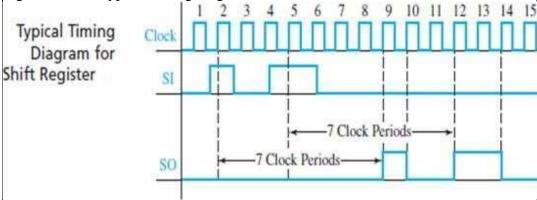

The inputs to the first flip-flop are S = SI and R = SI'. Thus, if SI = I, a 1 is shifted into the register when it is clocked, and if SI = 0, a 0 is shifted in. The following Figure shows a typical timing diagram.

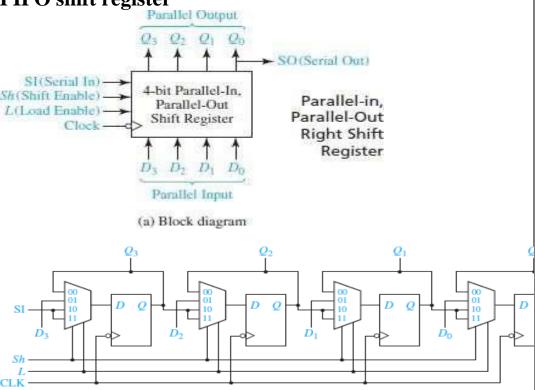

The following Figure (a) shows a 4-bit parallel-in, parallel-out shift register. Parallel-in implies that all

four bits can be loaded at the same time, and parallel-out implies that all bits can be read out at the same

time. The shift register has two control inputs, shift enable (Sh) and load enable (L). If Sh = 1 (and L = 1

or L = 0), clocking the register causes the serial input (SI) to be shifted into the first flip-flop, while the

data in flip-flops Q3,Q2, and Q1 are shifted right. If Sh = 0 and L = 1, clocking the shift register will cause the four data inputs (D3, D2, D1, D0) to be loaded in parallel into the flip-flops. If Sh = L = 0,

# PIPO shift register

(b) Implementation using flip-flops and MUXes

The following Table summarizes the operation of this shift register. All state changes occur immediately

following the falling edge of the clock.

# Shift Register Operation

|           | puts       | 1       | Next    | A.      |         |             |

|-----------|------------|---------|---------|---------|---------|-------------|

| Sh (Shift | ) L (Load) | $Q_3^+$ | $Q_2^+$ | $Q_1^+$ | $Q_0^+$ | Action      |

| 0         | 0          | $Q_3$   | $Q_2$   | $Q_1$   | $Q_0$   | No change   |

| 0         | 1          | $D_3$   | $D_2$   | $D_1$   | Do      | Load        |

| 1         | X          | SI      | $Q_3$   | $Q_2$   | $Q_1$   | Right shift |

The shift register can be implemented using MUXes and D flip-flops, as shown in the above Figure (b).

For the first flip-flop, when Sh = L = 0, the flip-flop Q3 output is selected by the MUX, so Q3<sub>+</sub> = Q3 and

no state change occurs. When Sh = 0 and L = 1, the data input D3 is selected and loaded into the flip-flop.

When Sh = 1 and L = 0 or 1, SI is selected and loaded into the flip-flop. The second MUX selects Q2,

D2, or Q3, etc. **The next-state equations for the** flip-flops are

$$Q_3^+ = Sh' \cdot L' \cdot Q_3 + Sh' \cdot L \cdot D_3 + Sh \cdot SI$$

$$Q_2^+ = Sh' \cdot L' \cdot Q_2 + Sh' \cdot L \cdot D_2 + Sh \cdot Q_3$$

$$Q_1^+ = Sh' \cdot L' \cdot Q_1 + Sh' \cdot L \cdot D_1 + Sh \cdot Q_2$$

$$Q_0^+ = Sh' \cdot L' \cdot Q_0 + Sh' \cdot L \cdot D_0 + Sh \cdot Q_1$$