| USN   |                                                                                                                   | 340 75 YEARS .    | •                   |

|-------|-------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|

|       |                                                                                                                   |                   | CHADIT              |

|       |                                                                                                                   | * CHRINSTITUTE OF |                     |

|       | Internal Assessment Test 2 – January 2022                                                                         | ACCHEDITED        | IN AF GRADE ET INAL |

| Sub:  | COMPUTER ORGANIZATION Sub Code: 18CS34 Bra                                                                        | anch: ISE         |                     |

| Date: | 25/1/2022         Duration:         90 min's         Max Marks:         50         Sem/Sec:         III / A,B & C | 1                 | OBE                 |

| 1.    | Answer any FIVE FULL Questions<br>a. Discuss in detail about the following bus types with timing diagram.         | MARKS             | CO RBT<br>CO2 L2    |

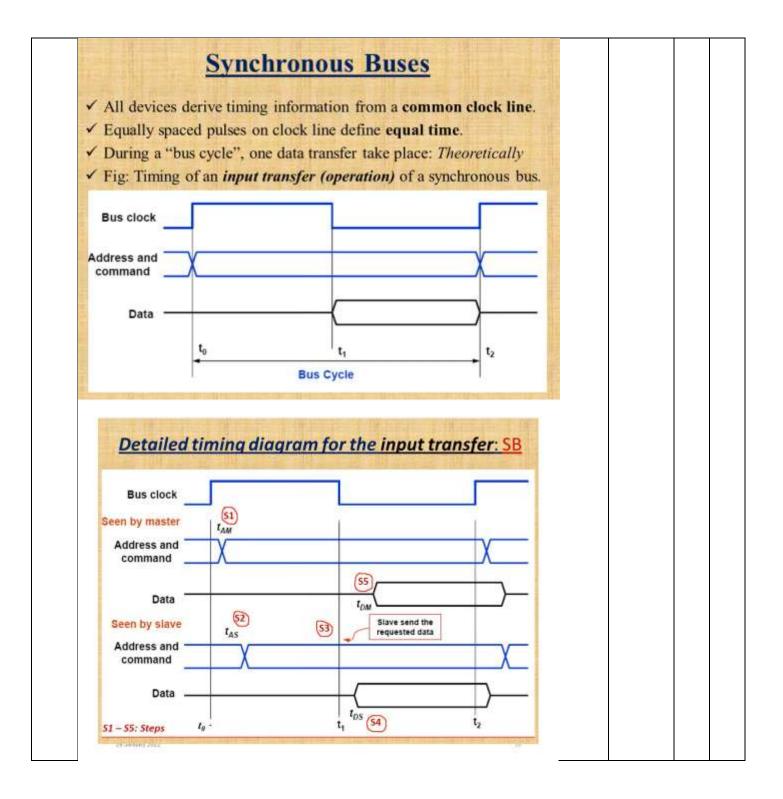

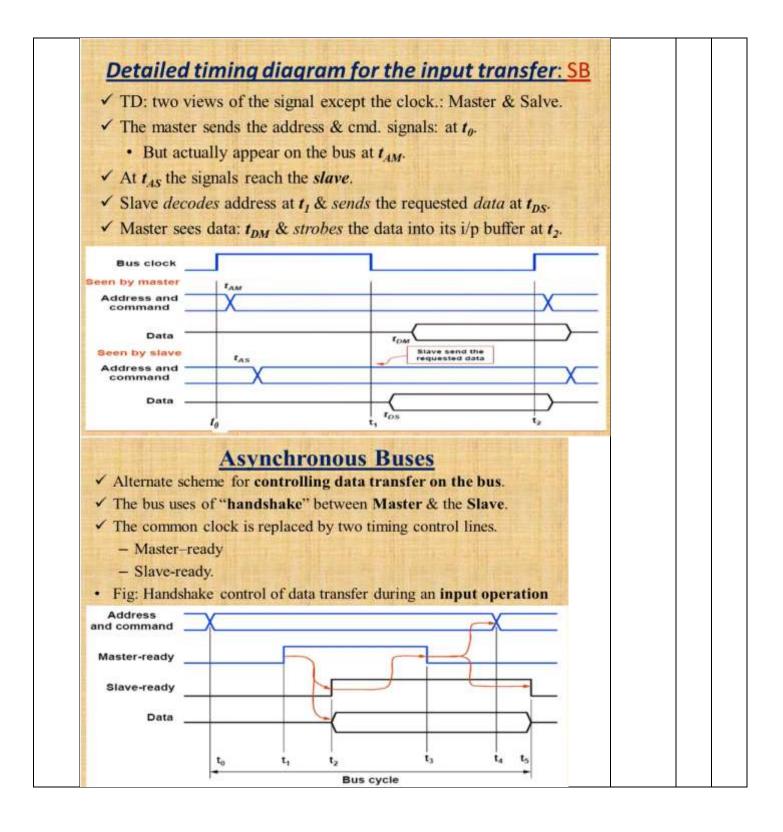

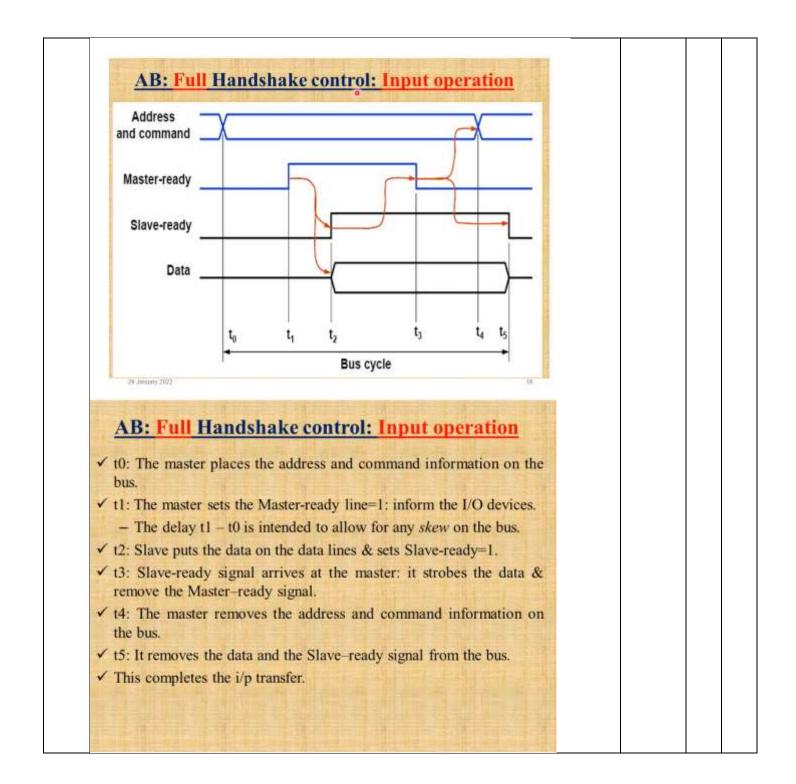

| 1.    | <ul><li>i) Synchronous Bus</li></ul>                                                                              | [10]              | CO2 L2              |

|       | ii) Asynchronous Bus                                                                                              |                   |                     |

|       |                                                                                                                   |                   |                     |

|       | • A bus protocol is the set of rules that govern the behavior of various devices                                  |                   |                     |

|       | connected to the bus as to when to place information on the bus, assert control                                   |                   |                     |

|       | signals, and so on.                                                                                               |                   |                     |

|       | <u>Buses</u>                                                                                                      |                   |                     |

|       |                                                                                                                   |                   |                     |

|       | ✓ The <b>bus</b> lines used for <b>transferring information</b> is grouped into 3                                 |                   |                     |

|       | types. They are,                                                                                                  |                   |                     |

|       | – Address line                                                                                                    |                   |                     |

|       | – Data line                                                                                                       |                   |                     |

|       | - Control line.                                                                                                   |                   |                     |

|       |                                                                                                                   |                   |                     |

|       | ✓ Control signals: Specifies read / write operation has to perform.                                               |                   |                     |

|       | ✓ Also carries <i>timing info.</i> : req. for <i>synchronization</i> .                                            |                   |                     |

|       | · Also carries umung injo req. for synchronization.                                                               |                   |                     |

|       | ✓ During data transfer: one device plays the role of a Master                                                     |                   |                     |

|       | <ul> <li>✓ Master device initiates the data transfer: Initiator.</li> </ul>                                       |                   |                     |

|       | and share the second   |                   |                     |

|       | ✓ The device addressed by the master is called as <i>Slave / Target</i> .                                         |                   |                     |

|       |                                                                                                                   |                   |                     |

|       | Rucoc                                                                                                             |                   |                     |

|       | Buses                                                                                                             |                   |                     |

|       |                                                                                                                   |                   |                     |

|       | A <i>bus protocol</i> : governs the <i>behavior</i> of various devices connected to the bus.                      |                   |                     |

|       |                                                                                                                   |                   |                     |

|       | 2 types of buses (also called as Bus Protocols).                                                                  |                   |                     |

|       | 1. Synchronous Bus                                                                                                |                   |                     |

|       | Tr Oynentonous Dus                                                                                                |                   |                     |

|       | 2. Asynchronous Bus.                                                                                              |                   |                     |

|       |                                                                                                                   |                   |                     |

|       | and the second  |                   |                     |

|       |                                                                                                                   |                   |                     |

|       |                                                                                                                   |                   |                     |

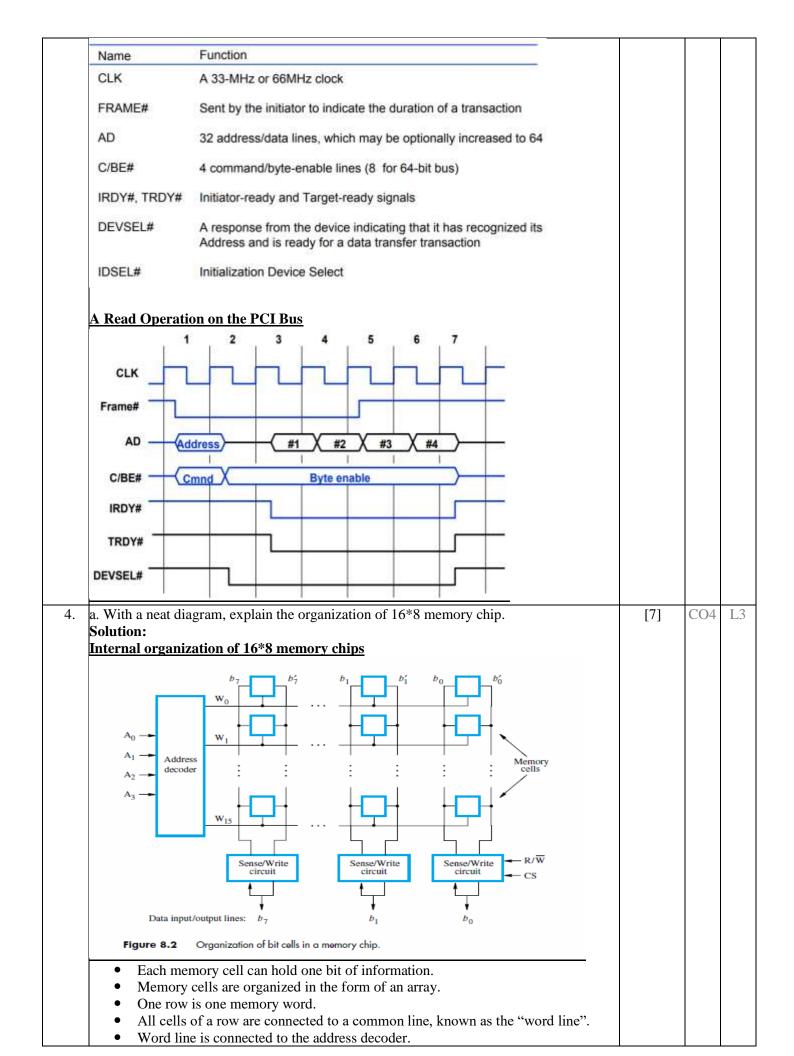

| chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

| b. Differentiate between SRAM and DRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | [3] | CO4 | L3 |

| Solution:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |    |

| • Static RAMs (SRAMs):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |     |    |

| <ul> <li>Consist of circuits that are capable of retaining their state as long as the<br/>power is applied.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |     |    |

| <ul> <li>Volatile memories, because their contents are lost when power is<br/>interrupted.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |     |    |

| • Access times of static RAMs are in the range of few nanoseconds.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |     |    |

| • However, the cost is usually high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |     |    |

| • Dynamic RAMs (DRAMs):                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |     |    |

| • Do not retain their state indefinitely.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |     |    |

| • Contents must be periodically refreshed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     |    |

| • Contents may be refreshed while accessing them for reading.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |     |    |

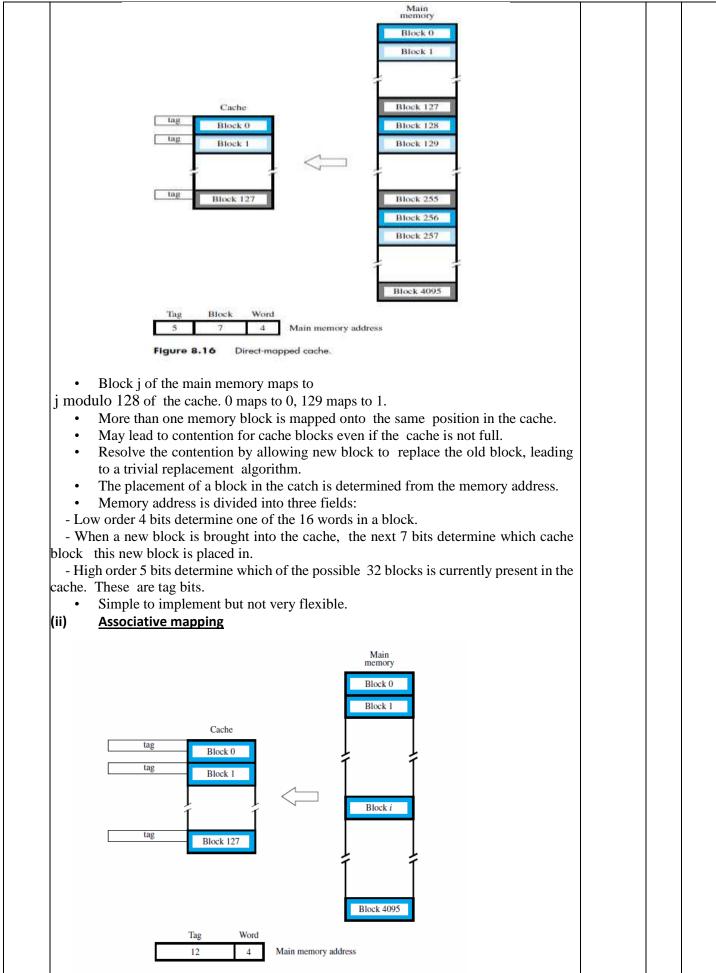

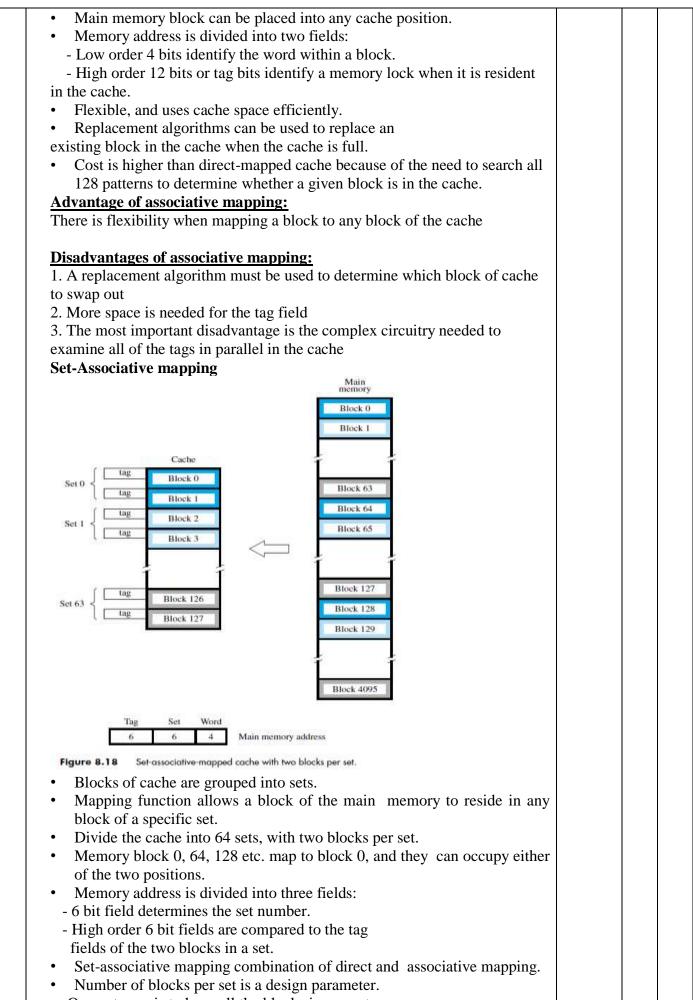

| address. Main memory is 64K which will be viewed as 4K blocks of 16 words each.<br>Explain different cache memory mapping functions with the help of diagrams.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |     |    |

| <ul> <li>Solution:</li> <li>Cache memory is an architectural arrangement which makes the main memory appear faster to the processor than it really is.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |    |

| <ul> <li>Cache memory is an architectural arrangement which makes the main memory appear faster to the processor than it really is.</li> <li>Image: At any given time, only some blocks in the main memory are held in the cache.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |     |    |

| <ul> <li>Cache memory is an architectural arrangement which makes the main memory appear faster to the processor than it really is.</li> <li>Image: Arrow of the processor of the process</li></ul> |     |     |    |

Figure 8.17 Associative-mapped cache.

.

- One extreme is to have all the blocks in one set,

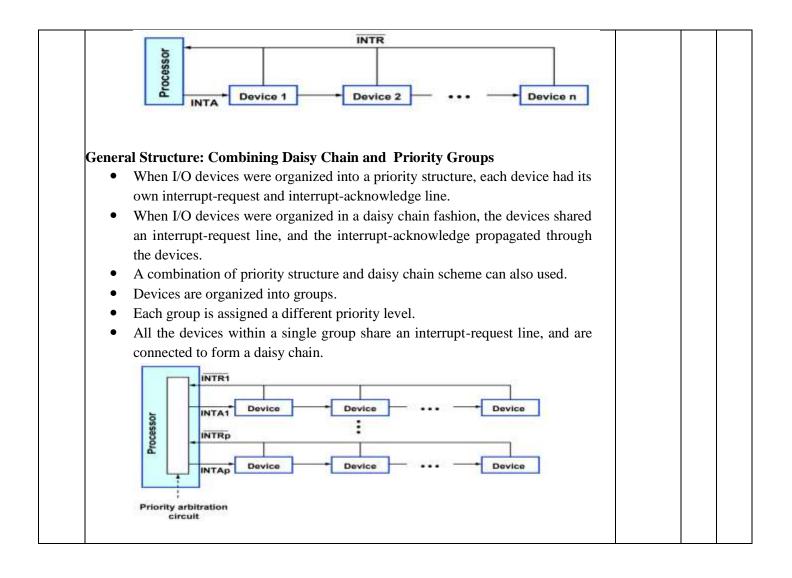

| <ul> <li>equiring no set bits (tully associative mapping).</li> <li>other extreme is to have one block per set, is the same as direct mapping.</li> <li>6. • Explain the following methods of handling interrupts from multiple devices. (10) Interrupt Nesting/Priority Structure ii)Daisy Chain Method</li> <li>Solution <ul> <li><b>Solution</b></li> <li><b>How</b> can the processor recognize the device requesting an interrupt?</li> <li>• Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine on the devices are likely to require different interrupt service?</li> <li>• Should a device be allowed to interrupt the processor while another interrupt is being service?</li> <li>• How should two or more simultaneous interrupt requests be handled?</li> </ul> </li> <li><b>Interrupt Nesting:</b> Hardware Priority: Multiple Requests over multiple interrupt request line is assigned a different priority level.</li> <li>• Hore these incervation existing address over multiple interrupt request line is assigned a different priority arbitration circuit in the processor.</li> <li>• If the interrupt request has a higher priority level than the priority of the processor.</li> <li>• If the interrupt request is accepted.</li> </ul> <li> <b>Priority robitration</b> <ul> <li>form Processor to Device</li> </ul> </li> <li> <b>Priority chinetion</b> <ul> <li>form Processor to Device</li> </ul> </li> <li> <b>Priority chinetion</b> <ul> <li>form Processor to Device</li> </ul> </li> <li> <b>Priority chinetion</b> <ul> <li>form a daisy chain.</li> <li>form form a daisy chain.</li> <li>form Processor to Device</li> </ul> </li> <li> <b>Distruction</b> <ul> <li>form a daisy chain.</li> <li>form brocessor in series, one after another. It is the computer equivalent of a series electrical circuit.</li> <li><b>Distruction</b> <ul> <li>interrupt request, the interrupt-request, the interrupt-acknowledge line is connected to form a daisy chain.</li> <li>for bevices are connected to form a</li></ul></li></ul></li>                                                                                                                                                               |    |                                                                                           |      |     |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------------------------------------------|------|-----|----|

| 6.       • Explain the following methods of handling interrupts from multiple devices.       [10]       CO2       L2         6.       • Explain the following methods of handling interrupts from multiple devices.       [10]       CO2       L2         6.       • Explain the following methods of handling interrupts from multiple devices.       [10]       CO2       L2         6.       • How can the processor recognize the device requesting an interrupt?       • Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in cach case?       • Should a device be allowed to interrupt the processor while another interrupt is being service?         • How should two or more simultaneous interrupt-acknowledge line.       • Each interrupt request ine assigned a different priority level.         • Interrupt requests ine is assigned a different priority level.       • Interrupt request has a higher priority level than the priority of the processor, then the request is accepted.         • Uptice 1       • Device 1       • Device 1       • Device P         • Priority arbitration circuit       • NTR: Interrupt Acknowledgement       • From Processor to Device         • From Processor to Device       • Device P       • Device oP       • INTAp         • A daity chain is an interconnection of computer devices, peripherals, or mervork nodes in series, one after another. It is the computer equivalent of a series electrical circuit.       •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | requiring no set bits (fully associative mapping).                                        |      |     |    |

| 6.       • Explain the following methods of handling interrupts from multiple devices.       [10]       CO2       L2         (i)       Interrupt Nesting/Priority Structure ii)Daisy Chain Method       Solution       [10]       CO2       L2         6.       • How can the processor recognize the device requesting an interrupt?       • Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in each case?       • Should a device be allowed to interrupt the processor while another interrupt is being serviced?       • How should two or more simultaneous interrupt requests be handled?         Interrupt Nesting:       Hardware Priority: - Multiple Requests over multiple interrupt request line is assigned a different priority level.       • Interrupt request line is assigned a different priority arbitration circuit in the processor, then the request is accepted.         • Interrupt request has a higher priority level than the priority of the processor, then the request is accepted.       • INTRP         • Priority arbitration errout       • INTR* Interrupt Acknowledgement From Device P       • INTR+         • Priority arbitration       • Received to from a daisy chain.       • Nevices are connected to form a daisy chain.         • Devices are computed to form a daisy chain.       • Devices raise an interrupt-request line.       • Devices line is activated.         • The processor in response activates interrupt-acknowledge.       • Devices raise an interrupt acknowledge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | -                                                                                         |      |     |    |

| <ul> <li>(i) Interrupt Nesting/Priority Structure ii)Daisy Chain Method</li> <li>Solution</li> <li>How can the processor recognize the device requesting an interrupt?</li> <li>Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in each case?</li> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?</li> <li>Interrupt Nesting: Hardware Priority: Multiple Requests over multiple interrupt request line</li> <li>Each interrupt request line is assigned a different priority level.</li> <li>Interrupt request in its assigned a different priority level.</li> <li>Interrupt request is is assigned a different priority of the processor, then the request is accepted.</li> <li>If the interrupt request from interrupt request from interrupt requests is accepted.</li> <li>Priority arbitration circuit</li> <li>INTR: Interrupt Request from Device 1 processor</li> <li>Priority arbitration circuit.</li> <li>Priority arbitration circuit.</li> <li>Processor to Device</li> <li>Davice Advice has a nigher priority edvices, peripherals, or network nodes in series, one after another. It is the computer equivalent of a series electrical circuit.</li> <li>Devices take the interrupt-request line, and interrupt-acknowledge line is connected to form a daisy chain.</li> <li>Wend edvices raises and interrupt-request line, and interrupt-acknowledge line is activated.</li> <li>The processor in response activates interrupt-request line is activated.</li> <li>The processor in response activates interrupt-request line is activated.</li> <li>The processor in response activates interrupt-request line is activated.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | the same as direct mapping.                                                               |      |     |    |

| <ul> <li>(i) Interrupt Nesting/Priority Structure ii)Daisy Chain Method</li> <li>Solution</li> <li>How can the processor recognize the device requesting an interrupt?</li> <li>How can the processor recognize the device requesting an interrupt?</li> <li>Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in each case?</li> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?</li> <li>Interrupt Nesting: Hardware Priority: Multiple Requests over multiple interrupt requests line is assigned a different priority level.</li> <li>Each interrupt request line is assigned a different priority level.</li> <li>Interrupt request in its assigned a different priority of the processor, then the request is accepted.</li> <li>Priority arbitration erceut</li> <li>If the interrupt Request from Bevice of Processor BAR Bevice Processor ID Bevice Processor Bar Bernonterle ID Bevice Processor Bevice Processor ID B</li></ul>                                                                                                                                                                                                                    |    |                                                                                           |      |     |    |

| <ul> <li>(i) Interrupt Nesting/Priority Structure ii)Daisy Chain Method</li> <li>Solution</li> <li>How can the processor recognize the device requesting an interrupt?</li> <li>Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in each case?</li> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How schuld two or more simultaneous interrupt requests be handled?</li> <li>Metrrupt Nesting: Hardware Priority: Multiple Requests over multiple interrupt requests line is assigned a different priority level.</li> <li>Interrupt request line is assigned a different priority level.</li> <li>Interrupt requests received over these lines are sent to a priority arbitration circuit in the processor.</li> <li>If the interrupt request is a sigher priority level than the priority of the processor, then the request is accepted.</li> <li>Priority arbitration errowt</li> <li>Priority arbitration</li> <li>Priority arbitra</li></ul>                                                                                                                                                                                                                    |    |                                                                                           |      |     |    |

| <ul> <li>Solution Handling Multiple Devices • How can the processor recognize the device requesting an interrupt? • Given that different views are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in each case? • Should a device be allowed to interrupt the processor while another interrupt is being service? • How should two or more simultaneous interrupt requests be handled? Interrupt Nesting: Hardware Priority: Multiple Requests over multiple interrupt request line • Each device has a separate interrupt-request and interrupt-acknowledge line. • Each interrupt-request line is assigned a different priority level. • Interrupt requests the is assigned a different priority of the processor, then the request is accepted. • If the interrupt requests has a higher priority level than the priority of the processor, then the request is accepted. • Priority arbitration effective • Priority arbitration • Priority a</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6. |                                                                                           | [10] | CO2 | L2 |

| <ul> <li>Handling Multiple Devices         <ul> <li>How can the processor recognize the device requesting an interrupt?</li> <li>Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in cach case?</li> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?</li> <li>Interrupt Nesting: Hardware Priority:- Multiple Requests over multiple interrupt request ine is assigned a different priority level.</li> <li>Each device has a separate interrupt-request and interrupt-acknowledge line.</li> <li>Each interrupt-request line is assigned a different priority arbitration circuit in the processor.</li> <li>If the interrupt request has a higher priority level than the priority of the processor, then the request is accepted.</li> </ul> </li> <li>Priority arbitration circuit in INTR* Interrupt Request from Device 1 Device 1 Device 1 Device P Device P Device P Device P Device P Device 1 NTA Device to Processor</li> </ul> <li>NTR: Interrupt Request from Device Device Dation of computer devices, peripherals, or network nodes in series, one after another. It is the computer equivalent of a series electrical circuit.</li> <li>Dative chain scheme:</li> <ul> <li>A daisy chain is an interconnection of computer devices, peripherals, or network nodes in series, one after another. It is the computer equivalent of a series electrical circuit.</li> <li>Devices share the interrupt-request line, and interrupt-acknowledge line is connected to form a daisy chain.</li> <li>Devices share the interrupt request line, and interrupt-acknowledge line is connected to form a daisy chain.</li> <li>When devices raise an interrupt reque</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                    |    | (i) Interrupt Nesting/Priority Structure ii)Daisy Chain Method                            |      |     |    |

| <ul> <li>Handling Multiple Devices</li> <li>How can the processor recognize the device requesting an interrupt?</li> <li>Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in each case?</li> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?</li> <li>Interrupt Nesting: Hardware Priority:- Multiple Requests over multiple interrupt request ince is assigned a different priority level.</li> <li>Each device has a separate interrupt-request and interrupt-acknowledge line.</li> <li>Each interrupt-request as a higher priority level than the priority arbitration circuit in the processor.</li> <li>If the interrupt request has a higher priority level than the priority of the processor, then the request is accepted.</li> </ul> Priority arbitration circuit INTR1 Interrupt Request from Device Device Device power of the processor of the processor the processor to Device District Chains and interrupt-acknowledge line is assess electical circuit. NTR: Interrupt Request from Device to Processor Device District Chains and interrupt advanded genent From Processor to Device District Chains the is an interconnection of computer devices, peripherals, or network nodes in series, one after another. It is the computer equivalent of a series electrical circuit. Divice share the interrupt request line, and interrupt-acknowledge line is connected to form a daisy chain. <ul> <li>When devices raise an interrupt request, the interrupt-acknowledge line is connected to form a daisy chain.</li> <li>When devices raise an interrupt request line, and interrupt-acknowledge.</li> <li>Received by device 1, if device 1 does not need service, it passes the signal to device 2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                   |    |                                                                                           |      |     |    |

| <ul> <li>How can the processor recognize the device requesting an interrupt?</li> <li>Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in each case?</li> <li>Should a device he allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?</li> <li>Interrupt Nesting: Hardware Priority: Multiple Requests over multiple interrupt request line is assigned a different priority level.</li> <li>Each device has a separate interrupt-request and interrupt-acknowledge line.</li> <li>Each device has a separate interrupt request and interrupt-acknowledge line.</li> <li>Each device has a separate interrupt request and interrupt-acknowledge line.</li> <li>Each device has a separate interrupt request and interrupt-acknowledge line.</li> <li>Each device has a separate interrupt request and interrupt a betweet on a priority arbitration circuit in the processor.</li> <li>If the interrupt requests is accepted.</li> </ul> Priority arbitration origination of the processor interrupt request is accepted. Interrupt Request from Device 1 Device 1 Device 1 UNTAP Priority arbitration origination of the processor to Device Divertion of the processor to Device Divece                                                                                                                                                                                                                                                |    |                                                                                           |      |     |    |

| <ul> <li>Given that different devices are likely to require different interrupt-service routines, how can the processor obtain the starting address of the appropriate routine in each case?</li> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?<br/>Interrupt Nesting: Hardware Priority:- Multiple Requests over multiple interrupt request line</li> <li>Each device has a separate interrupt-request and interrupt-acknowledge line.</li> <li>Each interrupt request line is assigned a different priority level.</li> <li>Interrupt requests the a higher priority level than the priority arbitration circuit in the processor.</li> <li>If the interrupt request has a higher priority level than the priority of the processor, then the request is accepted.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |                                                                                           |      |     |    |

| <ul> <li>routines, how can the processor obtain the starting address of the appropriate routine in each case?</li> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?<br/>Interrupt Nesting: Hardware Priority:- Multiple Requests over multiple interrupt request line</li> <li>Each device has a separate interrupt-request and interrupt-acknowledge line.</li> <li>Each divice has a separate interrupt request and interrupt-acknowledge line.</li> <li>Each divice has a separate interrupt request and interrupt-acknowledge line.</li> <li>Each divice has a separate interrupt request and priority arbitration circuit in the processor.</li> <li>If the interrupt requests received over these lines are sent to a priority arbitration circuit in the processor.</li> <li>If the interrupt request has a higher priority level than the priority of the processor, then the request is accepted.</li> </ul> Priority arbitration circuit INTR1 Device 1 Device 2 <ul> <li>Device p</li> <li>INTR2</li> </ul> Priority arbitration circuit INTR4 Device 1 Device p Device 1 Device p INTA1 Device p INTAp Priority arbitration circuit Rither the processor in the processor of computer devices, peripherals, or network nodes in series, one after another. It is the computer equivalent of a series electrical circuit. Davices share the interrupt request line, and interrupt-acknowledge line is connected to form a daisy chain. <ul> <li>Devices share the interrupt request, the interrupt-request line is activated.</li> <li>The processor in response activates interrupt-acknowledge.</li> <li>Received by device 1. if device 1 does not need service, it passes the signal to device 2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |                                                                                           |      |     |    |

| <ul> <li>routine in each case?</li> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?</li> <li>Interrupt Resting: Hardware Priority:- Multiple Requests over multiple interrupt request line</li> <li>Each device has a separate interrupt-request and interrupt-acknowledge line.</li> <li>Each interrupt request line is assigned a different priority level.</li> <li>Interrupt request sectived over these lines are sent to a priority arbitration circuit in the processor.</li> <li>If the interrupt request has a higher priority level than the priority of the processor, then the request is accepted.</li> <li><b>Priority arbitration</b></li> <li><b>Pri</b></li></ul> |    |                                                                                           |      |     |    |

| <ul> <li>Should a device be allowed to interrupt the processor while another interrupt is being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?</li> <li>Interrupt Nesting: Hardware Priority:- Multiple Requests over multiple interrupt request line</li> <li>Each device has a separate interrupt-request and interrupt-acknowledge line.</li> <li>Each chick chas a separate interrupt request and interrupt-acknowledge line.</li> <li>Each chick chas a separate interrupt request and interrupt-acknowledge line.</li> <li>Each device has a separate interrupt request and interrupt acknowledge line.</li> <li>Interrupt Request free event these lines are sent to a priority arbitration circuit in the processor.</li> <li>If the interrupt request has a higher priority level than the priority of the processor, then the request is accepted.</li> <li>Priority arbitration circuit</li> <li>NTR: Interrupt Request from Device 1 Device 2 Device p</li> <li>INTR: Interrupt Request from Device 1 NTR: Interrupt Acknowledgement From Processor to Device Daive Chain</li> <li>A daisy chain is an interconnection of computer devices, peripherals, or network nodes in series, one after another. It is the computer equivalent of a series electrical circuit.</li> <li>Daive Chain schemet</li> <li>Devices share the interrupt-request line, and interrupt-acknowledge line is connected to form a daisy chain.</li> <li>When devices raise an interrupt request, the interrupt-acknowledge.</li> <li>Received by device 1, if device 1 does not need service, it passes the signal to device 2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |                                                                                           |      |     |    |

| <ul> <li>being serviced?</li> <li>How should two or more simultaneous interrupt requests be handled?<br/>Interrupt Nesting: Hardware Priority: Multiple Requests over multiple interrupt request line</li> <li>Each interrupt request line is assigned a different priority level.</li> <li>Interrupt requests received over these lines are sent to a priority arbitration circuit in the processor.</li> <li>If the interrupt requests as a higher priority level than the priority of the processor, then the request is accepted.</li> <li>If the interrupt request has a higher priority level than the priority of the processor, then the request is accepted.</li> <li>Interrupt National Content of the processor of the proces of the proc</li></ul>                                                                                                                                                                                                                |    |                                                                                           |      |     |    |

| <ul> <li>How should two or more simultaneous interrupt requests be handled?<br/>Interrupt Nesting: Hardware Priority:- Multiple Requests over multiple interrupt request line is assigned a different priority level.</li> <li>Each device has a separate interrupt-request and interrupt-acknowledge line.</li> <li>Each interrupt requests received over these lines are sent to a priority arbitration circuit in the processor.</li> <li>If the interrupt request is a signer priority level than the priority of the processor, then the request is accepted.</li> <li>If the interrupt request is accepted.</li> <li>If the interrupt request is accepted.</li> <li>Interrupt request is accepted.</li> <li>Intraction interrupt request from Device 1 Device 1 INTAP</li> <li>Priority arbitration elevent</li> <li>INTR: Interrupt Request from Device to Processor</li> <li>INTA: Interrupt Request from Device to Processor</li> <li>INTA: Interrupt Request from Device to Processor</li> <li>A daisy chain is an interconnection of computer devices, peripherals, or network nodes in series, one after another. It is the computer equivalent of a series cleartical circuit.</li> <li>Divices share the interrupt request line, and interrupt-acknowledge line is connected to form a daisy chain.</li> <li>When devices rine repores activates interrupt request the interrupt-request line is activated.</li> <li>The processor in response activates interrupt-acknowledge.</li> <li>Received by device 1, if device 1 does not need service, it passes the signal to device 2.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                                                                           |      |     |    |

| Interrupt Nesting: Hardware Priority:- Multiple Requests over multiple<br>interrupt request line<br>• Each device has a separate interrupt-request and interrupt-acknowledge line.<br>• Each interrupt-request line is assigned a different priority level.<br>• Interrupt requests received over these lines are sent to a priority arbitration circuit<br>in the processor.<br>• If the interrupt request has a higher priority level than the priority of the<br>processor, then the request is accepted.<br>• <b>Priority arbitration</b><br>• <b>Circuit</b><br>• <b>INTR:</b> Interrupt Request from<br>Device 1 Device 2 •••• Device p<br>INTAP<br>• <b>Priority arbitration</b><br>• <b>Circuit</b><br>• <b>INTR:</b> Interrupt Request from<br>Device to Processor<br>INTA: Interrupt Acknowledgement<br>From Processor to Device<br><b>Disy Chain</b><br>• A daisy chain is an interconnection of computer devices, peripherals, or<br>network nodes in series, one after another. It is the computer equivalent of a<br>series electrical circuit.<br><b>Disv Chain</b><br>• Devices share the interrupt-request line, and interrupt-acknowledge line is<br>connected to form a daisy chain.<br>• Devices share the interrupt request, the interrupt-acknowledge line is<br>connected to form a daisy chain.<br>• When devices raise an interrupt request, the interrupt-acknowledge.<br>• Received by device 1, if device 1 does not need service, it passes the signal to<br>device 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | · ·                                                                                       |      |     |    |