| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

## Internal Assessment Test 3 – March 2022

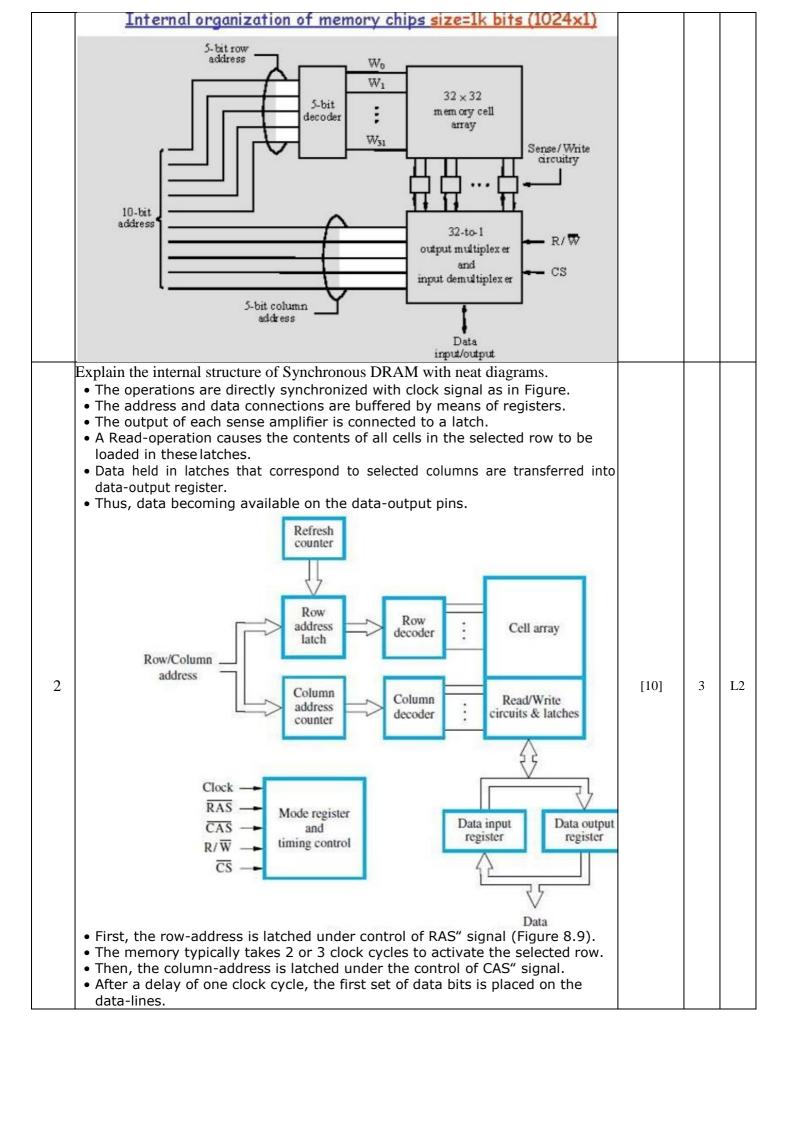

|       | <ul> <li>SDRAM automatically increments column-address to access next 3 sets of bits in the selected row.</li> <li>A good indication of performance is given by 2 parameters: 1) Latency 2) Bandwidth.</li> <li>Latency</li> </ul>                                                                                                                     |     |   |    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|----|

|       | <ul> <li>It refers to the amount of time it takes to transfer a word of data to or from the memory.</li> <li>For a transfer of single word, the latency provides the complete indication of memory performance.</li> <li>For a block transfer, the latency denotes the time it takes to transfer the first word of data.</li> <li>Bandwidth</li> </ul> |     |   |    |

|       | <ul> <li>It is defined as the number of bits or bytes that can be transferred in one second.</li> <li>Bandwidth mainly depends on <ol> <li>The speed of access to the stored data &amp;</li> <li>The number of bits that can be accessed in parallel.</li> </ol> </li> </ul>                                                                           |     |   |    |

| 3 (a) | Perform the following operations on the 5 bit signed numbers using 2's compliment representation system. Also indicate whether overflow has occurred. (i) $(-9) + (-7)$ overflow (ii) $(+7) - (-8)$ (iii) $(+13) + (+14)$ (overflow) $ \frac{110111}{110000}                        $                                                                  | [5] | 4 | L3 |

| 3 (b) | Explain 4bit carry-look ahead adder (5)                                                                                                                                                                                                                                                                                                                | [5] | 4 | L3 |

• The logic expression for s<sub>i</sub>(sum) and c<sub>i+1</sub>(carry-out) of stage i are ----(1) .(2)  $S_i = X_i + Y_i + C_i$  $C_{i+1}=X_iY_i+X_iC_i+Y_iC_i...$  Factoring (2) into  $C_{i\pm 1} = X_i y_i + (X_i + y_i) C_i$ we can write where  $G_i=x_iy_i$  and  $P_i=x_i+y_i$  $C_{i+1} = G_i + P_i C_i$ • The expressions G and P are called generate and propagate functions (Figure 9.4). • If  $G_i=1$ , then  $C_{i+1}=1$ , independent of the input carry  $C_i$ . This occurs when both  $x_i$  and  $y_i$  are 1. Propagate function means that an input-carry will produce an output-carry when either  $x_i=1$  or  $y_i=1$ . • All G and P functions can be formed independently and in parallel in one logic-gate delay. • Expanding citerms of i-1 subscripted variables and substituting into the ci+1 expression, we obtain  $C_{i+1} = G_i + P_i G_{i-1} + P_i P_{i-1} G_{i-2} \dots + P_1 G_0 + P_i P_{i-1}$ • Conclusion: Delay through the adder is 3 gate delays for all carry-bits & 4 gate delays for all sum-bits. • Consider the design of a 4-bit adder. The carries can be implemented as  $C_1=G_0+P_0C_0$  $C_2 = G_1 + P_1G_0 + P_1P_0C_0$  $C_3 = G_2 + P_2G_1 + P_2P_1G_0 + P_2P_1P_0C_0$  $C_4 = G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0 + P_3P_2P_1P_0C_0$ • The carries are implemented in the block labeled carry-lookahead logic. An adder implemented in this form is called a Carry-Lookahead Adder. • Limitation: If we try to extend the carry-lookahead adder for longer operands, we run into a problem of gate fan-in constraints. B cell (a) Bit-stage cell B cell B cell B cell B cell 51 53  $s_0$  $P_1$ Carry-lookahead logic  $G_0^I$ (b) 4-bit adder Figure 9.4 A 4-bit carry-lookahead adder. Perform signed multiplication of numbers (-12) and (-11) using Booth's Algorithm. 4 (a) [5] 4 L3

| $ \frac{10100(-12)}{\times 10101(-11)} \longrightarrow \frac{10100}{-11-11-1} (recoded multiplier) $ $ \frac{10100(-12)}{000001100} $ $ \frac{10100}{00001100} $ $ \frac{110100}{00001100} $ $ \frac{110100}{01100} $ $ \frac{11000}{01100} $ |     |   |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|----|

| Perform multiplication of (+13) and (-6) using Bit Pair recoding technique.  Sign extension                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | [5] | 4 | L3 |

|       | <ul> <li>Procedure: Do the follo</li> <li>1) Shift A</li> <li>2) Subtract</li> <li>3) If the si</li> <li>add</li> <li>sign</li> </ul> | owing n times<br>and Q left one binary    | e A).If the           |     |   |    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|-----|---|----|

|       | Initially                                                                                                                             | 0 0 0 0 0 0 (A)<br>0 0 0 1 0 0 (M)        | 10101(Q)              |     |   |    |

|       | Shift<br>Subtract                                                                                                                     | 000001<br>111100                          | 0101                  |     |   |    |

|       | Set qû<br>Restore                                                                                                                     | ①11101<br>100                             |                       |     |   |    |

| 5 (0) | Shift<br>Subtract                                                                                                                     | 000001<br>000010<br>111100                | 01010                 | [5] | 4 | L3 |

| 5 (a) | Set q0<br>Restore                                                                                                                     | 1)1 1 1 1 0<br>1 0 0                      |                       | [5] | 4 | L3 |

|       | Shift<br>Subtract                                                                                                                     | 0 0 0 0 1 0<br>0 0 0 1 0 1<br>1 1 1 1 0 0 |                       |     |   |    |

|       | Set q0<br>No restore                                                                                                                  | 000001                                    |                       |     |   |    |

|       |                                                                                                                                       | 000001                                    | 10100                 |     |   |    |

|       | Shift<br>Subtract                                                                                                                     | $000001 \\ 111100$                        | 01001                 |     |   |    |

|       | Set q0<br>Restore                                                                                                                     | 100                                       |                       |     |   |    |

|       | Shift<br>Subtract                                                                                                                     | 000010<br>000101<br>111100                | 10010                 |     |   |    |

|       | Set q0<br>No restore                                                                                                                  | 000001                                    |                       |     |   |    |

|       |                                                                                                                                       | 0 0 0 0 0 1<br>remainder                  |                       |     |   |    |

|       |                                                                                                                                       |                                           | -                     |     |   |    |

|       | No restore                                                                                                                            |                                           | 0 0 1 0 1<br>quotient |     |   |    |

| ŀ      | Perform 8/3 using Non Restoring Division method.                                                                                                                        |      |   |     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---|-----|

|        | NON-RESTORING DIVISION                                                                                                                                                  |      |   |     |

|        | Procedure:     Step 1: Do the following n times                                                                                                                         |      |   |     |

| 5 (b)  | i) If the sign of A is 0, shift A and Q left one bit position and subtract M from A;                                                                                    |      |   |     |

|        | otherwise, shift A and Q left and add M to A (Figure 9.23).<br>ii) Now, if the sign of A is 0, set $q_0$ to 1; otherwise set $q_0$ to 0.                                |      |   |     |

|        | Step 2: If the sign of A is 1, add M to A (restore).                                                                                                                    |      |   |     |

|        | Initially 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                         |      |   |     |

|        | Shift 0 0 0 0 1 0 0 0 First cycle                                                                                                                                       |      |   |     |

|        | Subtract 1 1 1 0 1<br>Set q <sub>0</sub> 1 1 1 1 0 0 0 0 0                                                                                                              |      |   |     |

|        |                                                                                                                                                                         |      |   |     |

| 5 (l-) | Shift 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                             | [6]  | 4 | 1.2 |

| 5 (b)  | Set q <sub>0</sub> 1 1 1 1 1 0 0 0 0 0                                                                                                                                  | [5]  | 4 | L3  |

|        | Shift 1 1 1 1 0 0 0 0 0 0                                                                                                                                               |      |   |     |

|        | Add 0 0 0 1 1<br>Set q <sub>0</sub> 0 0 0 0 1 0 0 0 1                                                                                                                   |      |   |     |

|        |                                                                                                                                                                         |      |   |     |

|        | Shift 0 0 0 1 0 0 0 1   Fourth cycle                                                                                                                                    |      |   |     |

|        | Set q <sub>0</sub> 1 1 1 1 1 0010                                                                                                                                       |      |   |     |

|        | Quotient                                                                                                                                                                |      |   |     |

|        | Add 1 1 1 1 1                                                                                                                                                           |      |   |     |

|        | 0 0 0 1 1<br>0 0 0 1 0                                                                                                                                                  |      |   |     |

|        |                                                                                                                                                                         |      |   |     |

|        | Remainder  Figure 9.25 A non-restoring division example.                                                                                                                |      |   |     |

|        |                                                                                                                                                                         |      |   |     |

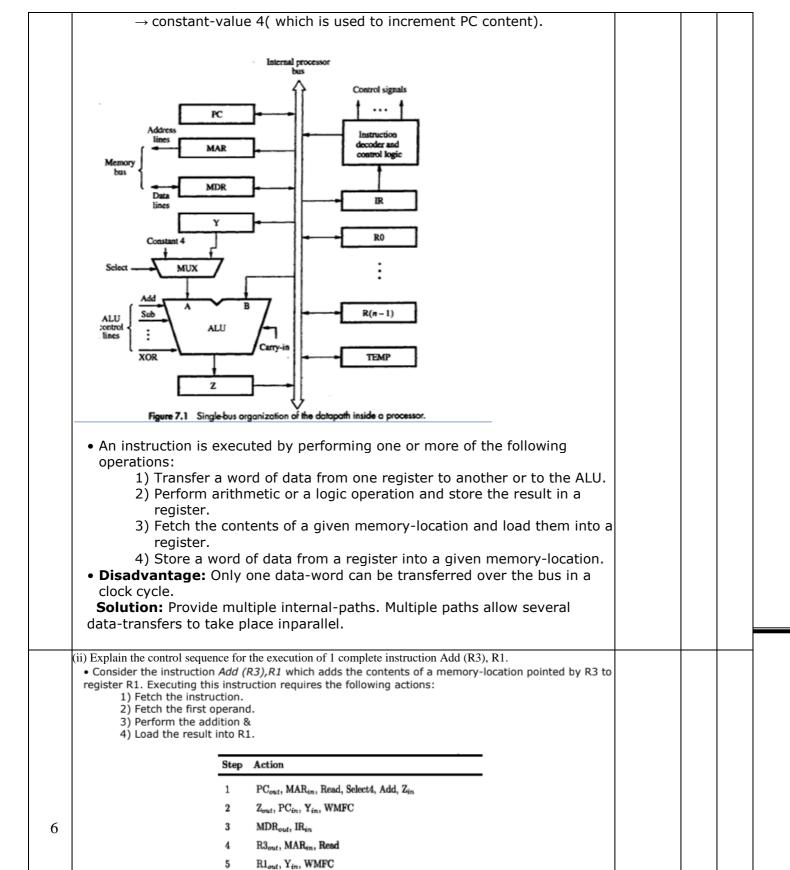

|        | Discuss with neat diagram, single bus organization of data path inside a processor.                                                                                     |      |   |     |

|        | • ALU and all the registers are interconnected via a <b>Single Common Bus</b>                                                                                           |      |   |     |

|        | (Figure 7.1).                                                                                                                                                           |      |   |     |

|        | <ul> <li>Data &amp; address lines of the external memory-bus is connected to the<br/>internal processor-bus via MDR&amp; MAR respectively. (MDR→ Memory Data</li> </ul> |      |   |     |

|        | Register, MAR → Memory Address Register).                                                                                                                               |      |   |     |

|        | • MDR has 2 inputs and 2 outputs. Data may be loaded                                                                                                                    |      |   |     |

|        | ightarrow into MDR either from memory-bus (external) or                                                                                                                 |      |   |     |

|        | → from processor-bus (internal).                                                                                                                                        |      |   |     |

|        | <ul> <li>MAR"s input is connected to internal-bus;</li> <li>MAR"s output is connected to external-bus.</li> </ul>                                                       |      |   |     |

|        | • Instruction Decoder & Control Unit is responsible for                                                                                                                 |      |   |     |

|        | $\rightarrow$ issuing the control-signals to all the units inside the processor.                                                                                        | F103 | _ |     |

| 6      | → implementing the actions specified by the instruction (loaded in the                                                                                                  | [10] | 5 |     |

|        | IR).                                                                                                                                                                    |      |   |     |

|        | <ul> <li>Register R0 through R(n-1) are the <b>Processor Registers</b>.</li> <li>The programmer can access these registers for general-purpose use.</li> </ul>          |      |   |     |

|        | • Only processor can access 3 registers <b>Y</b> , <b>Z</b> & <b>Temp</b> for temporary                                                                                 |      |   |     |

|        | storage during program-execution. The programmer cannot access                                                                                                          |      |   |     |

|        | these 3 registers.                                                                                                                                                      |      |   |     |

|        | <ul> <li>In ALU, 1) "A" input gets the operand from the output of the<br/>multiplexer (MUX).</li> </ul>                                                                 |      |   |     |

|        | 2) "B" input gets the operand directly from the processor-bus.                                                                                                          |      |   |     |

|        | <ul> <li>There are 2 options provided for "A" input of the ALU.</li> </ul>                                                                                              |      |   |     |

|        | MUX is used to select one of the 2 inputs.                                                                                                                              |      |   |     |

|        | MUX selects either                                                                                                                                                      |      |   |     |

|        | → output of Y or                                                                                                                                                        |      |   | ]   |

MDRout, SelectY, Add, Zin

Step1--> The instruction-fetch operation is initiated by

Figure 7.6 Control sequence for execution of the instruction Add (R3),R1

→ loading contents of PC into MAR &

Zout, R1in, End

• Instruction execution proceeds as follows:

→ sending a Read request to memory. The Select signal is set to Select4, which causes the Mux to select constant 4. This value s added to operand at input B (PC"s content), and the result is stored in Z. Step2--> Updated value in Z is moved to PC. This completes the PC increment operation and PC will now point to next instruction. Step3--> Fetched instruction is moved into MDR and then to IR.The step 1 through 3 constitutes the **Fetch Phase**. At the beginning of step 4, the instruction decoder interprets the contents of the IR. Thisenables the control circuitry to activate the control-signals for steps 4 through 7. The step 4 through 7 constitutes the **Execution Phase**. Step4--> Contents of R3 are loaded into MAR & a memory read signal is issued. Step 5--> Contents of R1 are transferred to Y to prepare for addition. Step6--> When Read operation is completed, memory-operand is available in MDR, and theaddition is performed.

Step7--> Sum is stored in Z, then transferred to R1.The End

returning to step1.

signal causes a new instructionfetch cycle to begin by