| CMR          |

|--------------|

| INSTITUTE OF |

| TECHNOLOGY   |

3.

iii) Body Effect

ii) Y = (A + BC)D

## Internal Assesment Test - I

| Sub:                                                                                                                           | Sub: VLSI Design Cod                                                                                                                |  |  |  |  |      |      | e:   | 18EC72 |    |     |

|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|------|------|------|--------|----|-----|

| Date                                                                                                                           | Date:         11 / 11/ 2021         Duration:         90 mins         Max Marks:         50         Sem:         VII         Branch |  |  |  |  |      |      | nch: | ECE    |    |     |

|                                                                                                                                | Answer all the Questions                                                                                                            |  |  |  |  |      |      |      |        |    |     |

|                                                                                                                                |                                                                                                                                     |  |  |  |  |      |      | M1   | OBE    |    |     |

|                                                                                                                                |                                                                                                                                     |  |  |  |  |      |      |      | Marks  | СО | RBT |

| 1. Explain the working of an nMOS enhancement mode transistor in different modes of                                            |                                                                                                                                     |  |  |  |  |      |      |      |        |    |     |

| operations with neat diagrams.                                                                                                 |                                                                                                                                     |  |  |  |  | [10] | CO1  | L1   |        |    |     |

| 2. An nMOS transistor is operated with the following parameters for 90nm technology: V <sub>GS</sub>                           |                                                                                                                                     |  |  |  |  |      |      |      |        |    |     |

| =0.9V, $V_{th}$ =0.5V, W=100nm, $\mu_n C_{ox} = 90 \mu A/V^2$ . Find $I_{DS}$ for i) $V_{DS} = 0.75 V$ ii) $V_{DS} = 1 V$ [10] |                                                                                                                                     |  |  |  |  |      | [10] | CO1  | L2     |    |     |

Explain any two of the following: i) Mobility Degradation ii) Channel length Modulation

| 5. | Explain the DC transfer characteristics of a CMOS inverter. |

|----|-------------------------------------------------------------|

|    |                                                             |

4. Implement the following expression using CMOS logic: i)  $Y = (\overline{A+B})(C+D)$

|     |  |  |  |  |  | A 100 Miles |

|-----|--|--|--|--|--|-------------|

| USN |  |  |  |  |  | CMRI        |

[5+5]

[5+5]

[10]

CO1

CO1

CO1

L1

L2

L1

CMR INSTITUTE OF TECHNOLOGY

## Internal Assesment Test - I

| Sub:                                                                                                                           | Sub: VLSI Design Code     |                |           |                    |         |          |       | e:    | 18EC72 |     |     |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------|-----------|--------------------|---------|----------|-------|-------|--------|-----|-----|--|

| Dat                                                                                                                            | e: 11 / 11/ 2021          | Duration:      | 90 mins   | Max Marks:         | 50      | Sem:     | VII   | Brar  | nch:   | EC  | ECE |  |

|                                                                                                                                |                           |                | Answe     | r all the Question | ons     |          |       |       |        |     |     |  |

|                                                                                                                                |                           |                |           |                    |         |          |       |       | N      |     | BE  |  |

| Marks                                                                                                                          |                           |                |           |                    |         | CO       | RBT   |       |        |     |     |  |

| 1.                                                                                                                             | Explain the working of    |                | enhanceme | ent mode transi    | stor in | differen | t mod | es of |        |     |     |  |

|                                                                                                                                | operations with neat dia  | grams.         |           |                    |         |          |       |       | [10]   | CO1 | L1  |  |

| 2.                                                                                                                             | An nMOS transistor is of  |                |           |                    |         |          |       |       | 54.07  |     |     |  |

| =0.9V, $V_{th}$ =0.5V, W=100nm, $\mu_n C_{ox} = 90 \mu A/V^2$ . Find $I_{DS}$ for i) $V_{DS} = 0.75 V$ ii) $V_{DS} = 1 V$ [10] |                           |                |           |                    |         |          | CO1   | L2    |        |     |     |  |

| 3. Explain any two of the following: i) Mobility Degradation ii) Channel length Modulation                                     |                           |                |           |                    |         |          |       |       |        |     |     |  |

| iii) Body Effect [5+5]                                                                                                         |                           |                |           |                    |         |          | CO1   | L1    |        |     |     |  |

| 4. Implement the following expression using CMOS logic: i) $Y = (\overline{A+B})(C+D)$                                         |                           |                |           |                    |         |          |       |       |        |     |     |  |

| ii) $Y = \overline{(A + BC)D}$ [5+5]                                                                                           |                           |                |           |                    |         |          |       | CO1   | L2     |     |     |  |

| 5. E                                                                                                                           | Explain the DC transfer c | haracteristics | of a CMC  | S inverter.        |         |          |       |       | [10]   | CO1 | L1  |  |

- The Mos to is a majority carrier device in which the et in a conducting channel beth the source & draw is controlled by the gate volty. In nMos, E's are the majority carriers I in pmos holes are the majority carriers.

- Fig. shows MOS structure. The top layer is a good conductor called the gate. The uniddle layer is a very thin insulating film of 5:02 called gate oxide (about 1000%). The bottom layer 'u doped Si body (phype for n-Mos & ntype for PMOS)

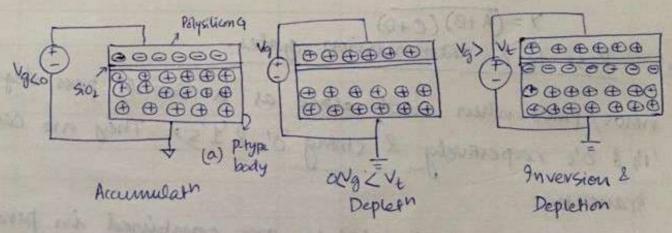

- Of let us consider the nous type.

In (a), a -ve volty is applied to the gate, so there is -ve charge on the gate. The mobile tuely charged holes are attracted to the region breneath the gate. This is called accumulate mode. In (b) a small the volty is applied to the gate, resulting

in some the charge on the gate. The holes in the body are repelled from the region directly beneath the gate, resulting in some the charge a deplet region below the gate.

9n(c), a higher the volty exceeding a critical threshold volty of is applied, attracting more the charge to the gate. The holes are repelled further and some is in the body are attracted to the region beneath the gate. This conductive layer of is in the p-type body is called the inversion layer. It depends on the popular in the body and thickness tox

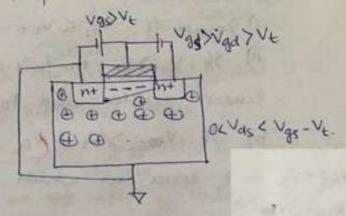

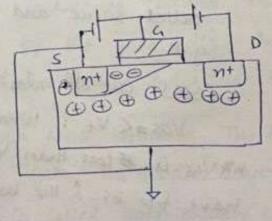

## nMos opr

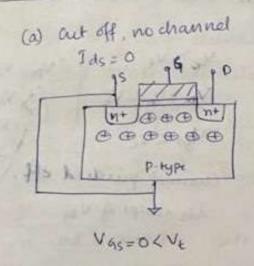

In nmos, there are 2 n-type regions called source and drain near the gate.

case 1 Cut off: Jas=0, Vas=0

VGS = < Vt : When the gate to source why vas in # less than Vt, the source & drain have free es I the body has free hores. I have free source is grounded, the body source &/ body drain just are o' mased or reverse biased, so little or no ct flows or reverse biased, so little or no ct flows

and the tx is off. This mode of op' is called cutoff.

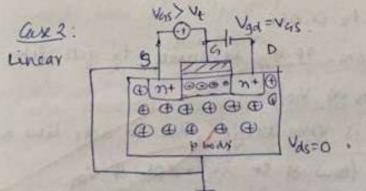

In this region, Vas > V4. At a result an inversion region of e's is formed which connects the source & drain meeting a conductive path & turning the tx on. Vos = Vas - Vab.

Now, if Vos=0, Vas= Vao .. there is no ef to push ct

from drain to source when a small the volty Vds is applied to the drain, ct Ids flows through the channel from to drain to source ( & flow from source > drain) This mode of op' is called linear, resistive, triode,

non-saturated or uneaturated. The ct I bs 1 with both 'Vbs & Vas.

Case 3: & Sahwam.

But if vos is sufficiently large such mat Vao < Vt, the channel is no longer inverted near the drain & becomes punched off. However Ix still flows. Hender Above the value of VDs when pinch off occurs, Ids is comballed only by the Vas 2 is no longer influenced by the D'. This mode is called saturation.

, 457 VE

Vos) Vas-Vt

Vgd < Vt.

Channel purched off. Ids undpt of Vos

· Vos = V45- V40 > Vaios > V45 - Vt Given

VG8 = 0.9V L= 90nm.

14h = 0.5 V

W= 100nm.

4n Cox = 90 H.

V 2F.0 = 20 V ()

(i) Vas = IV.

B = Cox + W = 90H \* 100 x v 90×n

B= 100 H

Ndr > 1+ => 0.0> 0.2

(8) Vgs - Vt = 0.9-0.5 = 0.4 = Vgt

Vos > 198-44 - Datwation Region.

4.0 × 2F.0

naitaventale @ sebI

Ide = B. Vot = 1004 \* (0.4)2

Tids = 8pA -

- caitalant grant yell latery

e the testablisty to is at high Vols.

- the mebility H is Replaced by Hepp, which is given by

Heff-n =

$$\frac{540 \frac{\text{cm}^2}{\text{V.8}}}{1 + \left(\frac{\text{Vgs+Vt}}{\text{o.54} \frac{\text{V}}{\text{pm}}}\right)^{1.85}} - \text{Heff q nmos decide}$$

At the field strongton, the theoreasis than I do also decreted the series that the series than I do also decreted the series than I do also decrete the series than I do also decreted the series that I do also decreted the series that I do also decreted the seri

What

$$v = \begin{cases} \frac{\text{Hepp.E}}{\text{Fc}} \\ \frac{\text{Fc}}{\text{Ec}} \end{cases}$$

,  $E < Ec$

Then the current I do is green by using IV characterestic

Nosat COX. W ( Vgs - Volsat ) Volsat , Vast < Vols.

Onset of saturalm mode of op in Mosfet is signified by pinch-off effect of channel. In satural, ideally by pinch-off effect of channel. In satural, ideally by pinch-off effect of channel. In the drain & body I was in since ased beyond forms a depleter region and if Vos is since ased beyond forms a depleter region and if Vos is since ased beyond Vosat, an even larger region form of the channel is purched off. The effective channel length then reduces purched off. The effective channel length then reduces to, Leff = L-Ld where, Ld is the length of the depleter region formed been body & drain where charge Q=0

funch off pt with increasing Vos, pinch off pt moves from Drain to source. & travelling from S -> D traverse the inverted channel length Leff & then they are injected into the deplet region of length La that seperales the pinch off to from Drain

the know Taking Left into account, social can be written as-

I Deat = # 16x W (Vas-Vt) -> (2

i l'eff (L, eq. 13) gives more et that the ideal et qu' in sam region under same brias condus.

Rewriting @ we get

Jogat = HOXW (VGT) (1+ Vds )

where 1+ Vas/va accounts for channel length modn.

VA & channel length & in called early vally channel length modn reduces gain of amplifiors.

Under ideal cend's, the threshold volty, Vt is considered const. But in reality, with increasing source volty, decreases with the body volty &, decreases with drain volty & increases with channel length.

when a voltage VSB is applied bett the source & body it increases the ainst of charge regd to invert the channel, thereby increasing line threshold vorty, Vt. This effect is called body effect. The threshold vorty is given as -

where, Vto is the threshold volty when source is at body pot.

Ps is the surface pot at threshold = 2 2 ln NA, -> 0

$N_A$  = doping levels  $n_i$  = intrinsic level of charges  $v_T$  = thermal volty =  $\frac{kT}{9}$  = 26 mV

8 = body effect coefficient 2 0.4 to

Answer 4

(i)

$$y = (B+B)(C+B)$$

A  $\frac{1}{2}$

B  $\frac{1}{2}$

A  $\frac{1}{2}$

A  $\frac{1}{2}$

A  $\frac{1}{2}$

B  $\frac{1}{2}$

A  $\frac{1}{2}$

B  $\frac{1}{2}$

A  $\frac{1}{2}$

B  $\frac{1}{2}$

A  $\frac{1}{2}$

B  $\frac{1}{2}$

B  $\frac{1}{2}$

A  $\frac{1}{2}$

B  $\frac{1}{2}$

B  $\frac{1}{2}$

B  $\frac{1}{2}$

B  $\frac{1}{2}$

A  $\frac{1}{2}$

B  $\frac{1}{2}$

B  $\frac{1}{2}$

A  $\frac{1}{2}$

B  $\frac{1}{2}$

9) 411)

$$Y = \overline{A + BC}D = (\overline{A + BC})(\overline{D})$$

$$= \overline{A + BC + \overline{D}} [De Morgan's law]$$

$$= \overline{A + BC}D$$

$$= \overline{A + BC$$

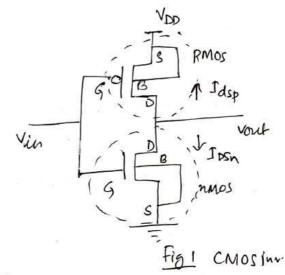

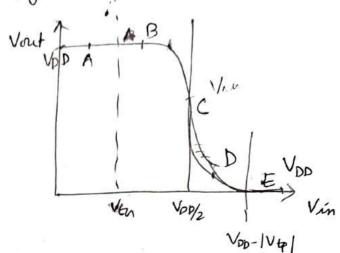

5 DE Transfer characteristics: De transfer chi of a ext relate the

of prorty to the I/P volty askuning that the I/P changes slowly enough that capacitances have plenty of time to change/discharge. A cmos inverter's DC transfer characteristics can

be obtained as follows -For the cmos inv. in fig(1)

let, Vasp = gak vortage for nmos

Vasp = "" " pmos

Vt,n = threshold " "nmos

Vt,p = "" " pmos.

Vtn = + Ve volty, Vtp = - ve volty

: Source of NMOS is grounded, Vasn = Vin & VDSn = Vout

". " pMos" " fied to VDD, Vasp= Vin-VDD, VDSp=Vout-VDD

The various regions of opr for the n&p Mos of cMos are shown in table (1).

|          | nmos             | PMOS                  |

|----------|------------------|-----------------------|

| Cut off: | Vasn < Van       | $V_{4}$ , $p > V_{t}$ |

|          | : Vin Wtn        | Vin> Vtp+VDD          |

| incar    | Vasn > Vtn       | Vas,P < Vxp           |

|          | : Vin > Vtn -    | Vin < Vtp + VDD       |

|          | Vosin Lygsn-Vtn  | VOSP) VGSP-VA         |

|          | Vout < Vin-V*n   | Vout> Vin - Vap       |

| Sahiram  | Vasn > Van       | Vasp < Vxp            |

| Santau"  | Vin>Vm           | Vin < Vep+Vop         |

|          | VDsn > Vasn - Vm | Vosp < Vasp - Vtp     |

|          | Vout > Vin - Von | Vout < Vin-Vtp        |

Assuming, Vtp=-Vtm & Bn=Bn, Idsn=[TDSP]

the opr of cmos inv. can be classified into 5 reprinsas shown in table(2). & fig (2)

- OFF so pros pull OP to Voo.

- 2) In refion B, MOS Starts to turn ON, Pulling the Op down to'O'.

- 3) In region C both p & n MOS are in Sat. (This region fresent in ideal transistors. for vin = VoD/2 & slope is -00 corresponding to infinite gain. Real txs. have finite of channel length mode of thus have finite slopes over a broader region)

- 4). In region D, pMOS is partially ON D in E it is completely off, leaving nMOS to pull off to GND.

|          |                |                   |                | γ, ο.              |

|----------|----------------|-------------------|----------------|--------------------|

| Region 1 | Cenda          | pmos              | nMos           | o) p               |

| Α        | 0 = Vin ( Vm   | linear            | cut-off        | Vout = VDD         |

| B        | Vtn < Nin < Vi | )y <sub>2</sub> " | Saturated      | Vorce > VDD/2      |

| و        | Vin = VDD/2    | sat.              | $\overline{D}$ | Vout drops sharply |

| D        | Vool2 < Vin <  | VDD- Vtp          | " linear       | Vous < Voo/2       |

| E .      | Vin > VDD -    | Vtp  a            | itog "         | Vact = 0           |

|          |                |                   |                |                    |