| USN |  |  |  |  |  |  |  |  |  |  |  |

|-----|--|--|--|--|--|--|--|--|--|--|--|

|-----|--|--|--|--|--|--|--|--|--|--|--|

Internal Assessment Test – I

| Sub:  | Microcontrolle                         | Code:        | 18EE52           |                                           |           |              |                 |         |      |     |

|-------|----------------------------------------|--------------|------------------|-------------------------------------------|-----------|--------------|-----------------|---------|------|-----|

| Date: | 11/11/2021                             | Duration:    | 90 mins          | Max Marks:                                | 50        | Sem:         | 5 <sup>th</sup> | Branch: | EEI  | Ξ   |

|       |                                        | Ar           | nswer <b>Any</b> | y FIVE FULL                               | Question  | ıs           |                 |         |      |     |

|       |                                        | Montra       | OB               | Е                                         |           |              |                 |         |      |     |

|       |                                        |              |                  |                                           |           |              |                 | Marks   | CO   | RBT |

|       | Draw the pin diagram                   | m of 8051 w  | ith a neat       | diagram and                               | brief ab  | out its      |                 | 10      | CO4  | L1  |

|       | features.                              | _            |                  |                                           |           |              |                 |         |      |     |

|       | Pin diagram- 4 man                     |              |                  |                                           |           |              |                 |         |      |     |

| 2     | Brief description- 6                   |              |                  | 4h auitabla ava                           |           | مله مناه است |                 | 10      | CO2  | 1.0 |

| 2     | a) Define assen commonly u             |              |                  |                                           | impie ex  | kpiain tr    | ie              | 10      | CO3  | L2  |

|       | Assembler Directiv                     |              | er unecuv        | ves. (3)                                  |           |              |                 |         |      |     |

|       | Org directive- 1 ma                    |              |                  |                                           |           |              |                 |         |      |     |

|       | End directive-1 ma                     |              |                  |                                           |           |              |                 |         |      |     |

|       | Count directive-1 n                    | narks        |                  |                                           |           |              |                 |         |      |     |

|       | <b>Examples- 1marks</b>                |              |                  |                                           |           |              |                 |         |      |     |

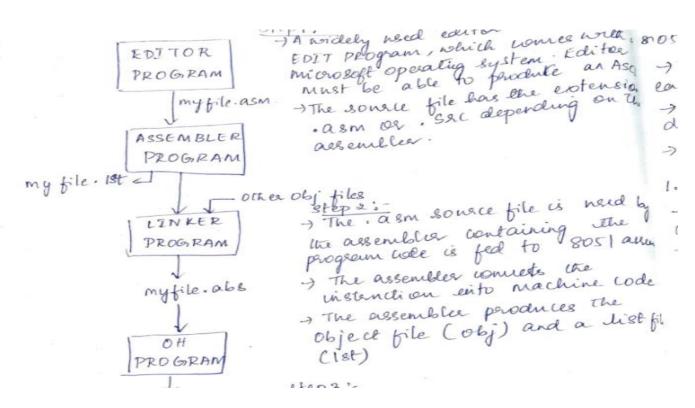

|       | b) Write briefly                       | about the st | eps invol        | ved in creating                           | g, assem  | ıbling aı    | nd              |         |      |     |

|       | running the p                          |              | 051. (5)         |                                           |           |              |                 |         |      |     |

|       | Flow chart- 2 mark                     |              |                  |                                           |           |              |                 |         |      |     |

| 2     | Steps explanation-                     |              |                  | 20074                                     |           |              |                 | 10      | G0.2 | 7.1 |

| 3     | Explain the internal                   |              |                  |                                           | itable di | agrams.      |                 | 10      | CO2  | L1  |

|       | Internal RAM Org<br>Working register b |              |                  | 3 marks                                   |           |              |                 |         |      |     |

|       | Bit Addressable -2                     |              | 79               |                                           |           |              |                 |         |      |     |

|       | Scratch pad-3 Mar                      |              |                  |                                           |           |              |                 |         |      |     |

| 4     | Explain with suitable                  |              | he differe       | ent types of ad                           | dressing  | modes        | used            | 10      | CO1  | L1  |

|       | in 8051.                               | r .,         |                  | J. T. |           | ,            |                 |         |      |     |

|       | Five Addressing me                     | odes along v | vith exan        | nples                                     |           |              |                 |         |      |     |

|       | 1. Immediate Addr                      | essing mode  | e-2 mark         | S                                         |           |              |                 |         |      |     |

|       | 2.Register addressi                    | ng mode-2 1  | marks            |                                           |           |              |                 |         |      |     |

|       | 3.Indirect Addressi                    | _            |                  |                                           |           |              |                 |         |      |     |

|       | 4. Register Indirect                   |              | _                | 2 marks                                   |           |              |                 |         |      |     |

|       | 5. Indexed Address                     | sing mode- 2 | Marks            |                                           |           |              |                 |         |      |     |

| 5     | With a neat block di                   | agram of 805 | 51, brief        | about its salier                          | nt featur | es.          |                 | 10      | CO2  | L1  |

|       | Block Diagram- 4 N                     | •            | ,                |                                           |           |              |                 |         |      |     |

|       | Salient Features-6                     |              |                  |                                           |           |              |                 |         |      |     |

| 6     | Explain in brief for t                 | _            | _                |                                           |           |              |                 | 10      | CO1  | L4  |

|       | <ol> <li>Program Cou</li> </ol>        |              |                  |                                           | er 4.R    | Register     | Bank            |         |      |     |

|       | Each Brief e                           | explanation  | – 2.5 ma         | rks                                       |           |              |                 |         |      |     |

| 7 | Explain the program ROM space allocation for the following:  1.EA=0 for 8751 chip - block diagram and explanation- 5 marks  2. EA= Vcc with both on-chip and off-chip ROM for 8751 block diagram and explanation- 5 marks                           | 10 | CO1 | L3 |  |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|----|--|

| 8 | Explain the arithmetic instruction used for 8051  Explanation Addition with examples- 2.5marks  Explanation Subtraction with examples -2.5marks  Explanation Multiplication with examples - 2.5 marks  Explanation Division with examples-2.5 marks | 10 | CO2 | L4 |  |

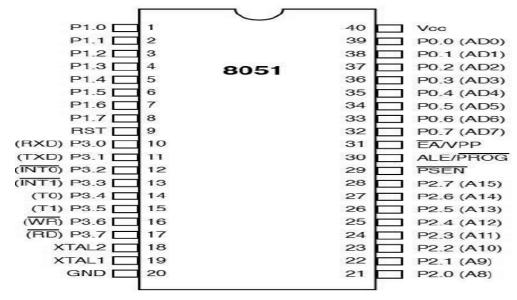

#### 1. Pin diagram of 8051

- To access the pins of port O as input & output ports, each pin must be connected externally to a  $10K\Omega$  pull-up resistor.

- Port 0 is designated as AD0-AD7, allowing it to be used for both address & data.

- When Port 0 is connected to an external memory, port 0 provides address and data.

#### Port-1

- Total of 8 pins.

- Can be used as an input or output.

- Does not require any pull up resistors

- If port 1 has been configured as an output port, to make it an input port again, it can programmed by writing 1 to all its bits.

#### Port-2

- Total of 8 pins.

- Do not require pull up resistor.

- On reset, port 2 is configured as an input port.

#### Port-3

- Total of 8 pins.

- Do not require pull up resistor

- Port 3 has the additional function of providing extremely important signal such as interrupts.

#### 2. Data Byte Directive:

• The DB directive is the most widely used data directive in the assembler.

- It is used to define the 8-bit data.

- When DB is used to define data, the numbers can be in decimal, binary, hex, or ASCII formats. For decimal, the "D" after the decimal number is optional, but using "B" (binary) and "H" (hexadecimal) for the others is required

- ORG

- The ORG directive is used to indicate the beginning of the address.

- The number that comes after ORG can be either in hex or in decimal.0000 or 0000D MOV A,30

- If the number is not followed by H, it is decimal and the assembler will convert it to hex.

- Some assemblers use ". ORG" (notice the dot) instead of "ORG" for the origin directive. Check your assembler.

- EOU

- This is used to define a constant without occupying a memory location.

- The EQU directive does not set aside storage for a data item but associates a constant value with a data label so that when the label appears in the program, it constant value will be substituted for the label.

- The following uses EQU for the counter constant and then the constant is used to load the R3 register.

Eg: COUNT EQU 25

......

Mov r3, #COUNT

2.b.

The link program takes one one more object files & produces an absolute object file (.abe)

The "abs" file is fed into a program Called OH (Object fi hex connector) which creates the file with extension" he ready to burn into Rom.

3.

|            |      | Working<br>Registers |                  | Bit Addressable |    |    | General Purpose |

|------------|------|----------------------|------------------|-----------------|----|----|-----------------|

|            | 00   | RO                   | 20               | 07              | 00 | 30 | <u> </u>        |

|            | 01   | R1                   | 21               | OF              | 08 |    | I               |

| 10         | 02   | R2                   | 22               | 17              | 10 |    |                 |

| gank o     | 03   | R3                   | 23               | 1F              | 18 |    | 1               |

| 2          | 04   | R4                   | 24               | 27              | 20 |    |                 |

|            | 05   | R5                   | 25               | 2F              | 28 |    |                 |

|            | 06   | R6                   | 26               | 37              | 30 |    | 1               |

|            | 08   | R7                   | 27               | 3F              | 38 |    |                 |

|            |      | RO                   | 28               | 47              | 40 |    |                 |

|            | 09   | R1                   | 29               | 4F              | 48 |    |                 |

| 2          | OA - | R2                   | 2A               | 57              | 50 |    | _               |

| Sank L     | ов   | R3                   | 2B               | 5F              | 58 |    |                 |

|            | 00   | R4                   | 2C               | 67              | 60 |    |                 |

|            | 00   | R5                   | 2D               | 6F              | 68 |    |                 |

|            | OE - | R6                   | 2F               | 77              | 70 |    | ì               |

|            | OF   | RO<br>R7             | 8051 micro<br>2F | 7F              | 78 |    | ı               |

|            | 10   |                      | -                |                 |    |    | 1               |

|            | 11   | R2<br>R1             |                  |                 |    |    | J               |

| 80         | 13   | R3                   | <b>⊣</b>         |                 |    |    | 1               |

| 2 yueg     | 14   | R4                   | -                |                 |    |    | 1               |

| ~1         | 15   | R5                   |                  |                 |    |    | 1               |

|            | 16   | R6                   | →                |                 |    |    | 1               |

|            | 17   | R7                   |                  |                 |    |    | 1               |

|            | 18   | RO                   | <b>⊣</b>         |                 |    |    | 1               |

|            | 19   | R1                   |                  |                 |    |    | l               |

|            | 1A   | R2                   | <b>—</b>         |                 |    |    | I               |

| Pag<br>Bar | 18   | R3                   |                  |                 |    |    | l               |

| Bank 3     | 10   | R4                   | _                |                 |    |    | I               |

| 1.650      | 1D   | R5                   | _                |                 |    |    | 1               |

|            | 1E   | R6                   | _                |                 |    |    | 1               |

|            | 1F   | R7                   | _                |                 |    |    |                 |

|            |      |                      | -                |                 |    | 7F |                 |

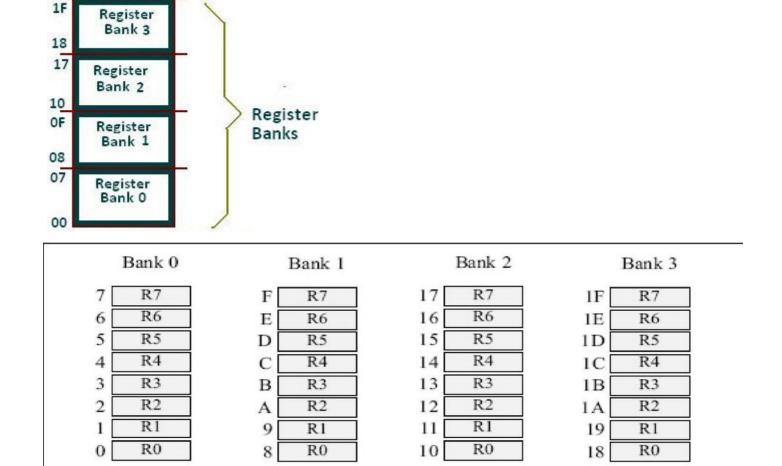

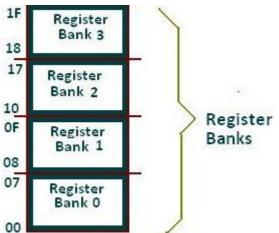

- Four register banks.

- Each bank containing 8 registers labeled from R0-R7.

- Total of 32 working registers labeled from 00-1FH.

- By default bank 0 will be selected on reset

#### Bit Addressable RAM

16 bytes of RAM from address 20h to 2fh are bit addressable.

Each bit of has an address and can be accessed individually

Total of 128 bits address is given in the register bank.

General purpose RAM-registers above bit addressable registers are called Scratch pad registers. Used for temporary

| RAM                        |    |                  |      |       |      |      |    |     |   |       |

|----------------------------|----|------------------|------|-------|------|------|----|-----|---|-------|

| Byte<br>address            |    |                  | ı    | 3it a | ıddr | ess  |    |     |   |       |

| 27                         | 3F | 3E               | 3D   | 3C    | 3B   | 3A   | 39 | 38  | 7 | 38    |

| 26                         | 37 | 36               | 35   | 34    | 33   | 32   | 31 | 30  | - |       |

| 25                         | 2F | 2E               | 2D   | 2C    | 2B   | 2A   | 29 | 28  |   | 33    |

| 24                         | 27 | 26               | 25   | 24    | 23   | 22   | 21 | 20  |   |       |

| 23                         | 1F | 1E               | ID   | 1C    | 1B   | 1A   | 19 | 18  | ſ | 20000 |

| 22                         | 17 | 16               | 15   | 14    | 13   | 12   | 11 | 10  |   |       |

| 21                         | 0F | 0E               | 0D   | 0C    | ов   | 0A   | 09 | 08  |   |       |

|                            | 07 | 06               | 05   | 04    | 03   | 02   | 01 | 00  |   | F     |

| 20<br>1F<br>18<br>17<br>10 |    |                  |      |       |      | No A |    | 0.0 |   |       |

| 18                         |    |                  |      | Bar   | ık 3 |      |    |     |   |       |

| 17                         |    |                  |      | D.    | ık 2 |      |    |     |   |       |

| 10                         |    |                  |      | Bai   | IK Z |      |    |     |   |       |

| 0F                         |    |                  |      | D.u.  | J 1  |      |    |     |   |       |

| 08                         |    | Bank I           |      |       |      |      |    |     |   |       |

| 07                         |    | Default register |      |       |      |      |    |     |   |       |

| 00                         |    | 1                | bank | c for | RO   | -R   | 7  |     |   |       |

Addressing Modes. The CPU can acces data in narions nears. The dollar could be in a register, be in nearony or be promided as an immediate make. The various ways of accessing a data are called addressing Modes. are called addressing modes. There are fine different types of Addressing Mode

1. Immediate

2. Register

3. pirect

4. Register Endreel

5. Indexed.

1. Immediate · Addressing Mode: -) In this addressing mede, the some we operand is a constant i e innediate data. I The immediate data must be preceded by the pround

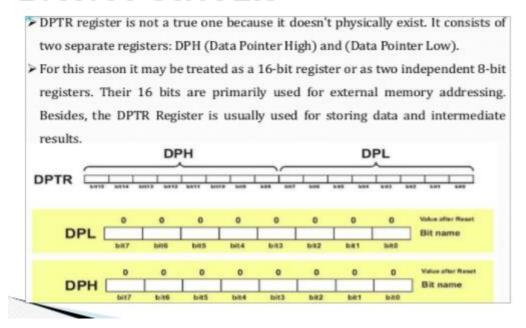

-) This oddersong made can be used to load information the DPTR legister.

-) The immediate data must ) This addressing made can be used to load information aits any of the segisters withdring the DPTR segister. ; load 56H vito Accumulate Eg: 10 MOUA, #56H ; load the decimal habit box MOU R3, \$162 Uto R3 MOU B, #404 ; load 404 wito B MOU DATE, \$145214; DATE = 45124. MOU DPTR, #2550H. MOU DPL, #150H MOU .DPH, #254 2. Register Addressing Mode: If in notices the use of segisters to hold the data to be compliances Maniepulated. ; copy the contents of Ro into A MOU A, RO : agry the contents of A citols MOU Re, A : Add the contents of A to The ADD A, R5 Contents of R5 ADD A, R7 add the contents of 27 to : Save the Sacenambator in 26 MOV R6, A

- The size of the source of distination should be matched.

Eg: O MOU DPTR, #25F5H -> valid.

- Sonrie is A > & bit Register

Destination is > 16 bit Register

- The data can be moved between the accumulator of Rn (for n=0 to 7), but the movement of data between 2n is not allowed.

Eg:- MOU A, RO Malid.

MOU RO, R7 Minalid.

3) Direct Addressing Mode!—

The data is in a RAM memory location whose addressing is known of this coldress is given as past of a restriction.

Although the entire 128 bytes of RAM can be addressing mode.

Issing direct addressing Mode.

If is must often used to access RAM locations 30-7FH.

Eq: MOU RO, 40H; cop Save the contents of RAM holation 40H to RD holation 40H to RD RAM Contents of A vito RAM Coation FFH.

In the register indirect addressing mode, a significant is used as a positive to the data, only register to & & & | and send for internal RAM indirect data transfer. 4. Indirect Addressing Mode: when they hold the address of ROM locations strey must be preceded by the @ symbol. ; more the contents of RAM Eg: MOVA, @RO location of 20 into A. : More the bontents of B into MOU QRI, B the kan location whose address 5. Indeped Addressing Modes held at RI. accessing data elements of look-up table entries located in the program ROM space of the 8051.

### 6.Register Bank

- Four register banks.

- Each bank containing 8 registers labeled from R0-R7.

- Total of 32 working registers labeled from 00-1FH.

- By default bank 0 will be selected on reset

| Bank 0 | Bank I | Bank 2 | Bank 3 |

|--------|--------|--------|--------|

| 7 R7   | F R7   | 17 R7  | 1F R7  |

| 6 R6   | E R6   | 16 R6  | 1E R6  |

| 5 R5   | D R5   | 15 R5  | 1D R5  |

| 4 R4   | C R4   | 14 R4  | 1C R4  |

| 3 R3   | B R3   | 13 R3  | 1B R3  |

| 2 R2   | A R2   | 12 R2  | 1A R2  |

| 1 R1   | 9 R1   | 11 R1  | 19 R1  |

| 0 R0   | 8 R0   | 10 R0  | 18 R0  |

**Data Pointer**

PSW. Program Status word

The 8051 Mc has a flag rigister to indicate authoretic conditions but as the Carry bits. The flag register en the 8051 is Called the program status word (PSW) register.

The Program Status wood (PSW) register is an 8-6it register. Hence it is refused to as the flag register. It have used by the 8051. The two named bits one user-olefinable flags. I form of the flags are called conditional flags, that they indicate home conditions that the result after an instantion is executed. The fore flags are CY (Carry), Ac (Anxi havy Carry), P (Parity) & OV (Onerflow).

|     |       |     |        | 1       |          |        |       |         |      |          |                       |

|-----|-------|-----|--------|---------|----------|--------|-------|---------|------|----------|-----------------------|

| СЧ  | AC    | F0  | RSI    | RSO     | OV       |        | P     |         |      | 19<br>19 |                       |

| СЧ  | PSW.7 | -   | Carr   | y flag  | <i>)</i> |        |       |         |      |          |                       |

| AC  | PSW.6 |     |        | 1       | Mag      | 1      |       | 0 . 001 | wal  | purp     | 100                   |

| Fo  | PSW.  | 5   | Avai   | able    | to 2     | he no  | ex fo | B+ 1    |      | 1 1      |                       |

| RSI | PSW.  | 4   | Kegns  | Ter Bu  | nun      | 12000  |       |         |      |          |                       |

| RSZ | PSW.  |     | Regre  | ter E   | Haa.     | ,      |       |         |      |          |                       |

| OV  | PSW.  |     | oner   | -0 0    | - 0 0    | - 1-1  | -     |         |      |          |                       |

| P   | PSW   | · [ | Parili | : Alara | . Sel    | of cle | ared  | by      | hard | ware     | each<br>111           |

| į.  | 1-310 |     | instru | ction   | c        | y cle  | to so | idio    | icum | ulati    | each<br>Heren<br>100. |

|     |       |     | nn     | oer o   | 16       | 113    |       |         |      |          |                       |

# Stack in the 805!

The stack is a section of RAM need by the CPU to store enformation tempor arily. This enformation could be data as an address.

of The register used to access the stack is called the Stack pointer register. The stack pointer in the 8051 is only 8 bits wide, which means that it can take values of oo to FFH.

The storing of a CPU register in the stack is called PUSH of pulling the contents off the stack back wito a CPU register in the stack is called PUSH of pulling the contents off the stack back wito a CPU register is called PUSH of pulling the contents off the stack back wito a CPU register is called a POP.

Pushing onto the Stack.

In the 8051, the stack pointer (SP) points to the last used location of the stack.

I when the data is forehed onto the stack, the stack printer (SP) is incremented by one.

Popping the contents of the stack hack into a given register is the opposite process of pushing. Register is the opposite process of pushing.

I with every prop, the top byte of the stack is copied to the register specified by the instanction of the stack pointer is decremented once.

## DATA POINTER

7.

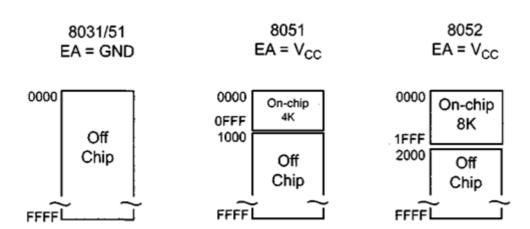

- 1. When EA = 0, the EA pin is strapped to GND, and all program fetches are directed to external memory regardless of whether or not the 8751 has some on-chip ROM for program code. This external ROM can be as high as 64K bytes with address space of 0000 FFFFH. In this case an 8751 (89C51) is the same as the 8031 system.

- 2. With the 8751 system where EA =  $V_{cc}$ , the microcontroller fetches the program code of addresses 0000 OFFFH from on-chip ROM since it has 4K bytes of on-chip program ROM and any fetches from addresses 1000H FFFFH are directed to external ROM.

- 3. With the 8752 system where  $EA = V_{cc}$ , the microcontroller fetches the program code of addresses 0000 1FFFH from on-chip ROM since it has 8K bytes of on-chip program ROM and any fetches from addresses 2000H FFFFH are directed to external ROM.

## ADD & ADDC instruction

## The ADD and ADDC Instructions

- ◆ADD A, source ; A = A + source

- ◆ADDC A, source ; A = A + source + C

- · A register must be involved in additions

- The C flag is set to 1 if there is a carry out of bit 7

- The AC flag is set to 1 if there is a carry out of bit 3

- ADD is used for ordinary addition

- ADDC is used to add a carry after the LSB addition in a multi-byte process

## Subtraction

- In many microprocessors there are two different instructions for subtraction:

- · SUB and SUBB (subtract with borrow).

- In the 8051 we have only SUBB. To make SUB out of SUBB, we have to make CY = 0 prior to the execution of the instruction.

- Therefore, there are two cases for the SUBB instruction:

- (1) with CY = 0,

- (2) with CY = 1

## SUBB with CY=0

- Three steps are performed for every SUBB instruction by the internal hardware of the 8051 CPU, regardless of the source of the operands, provided that the addressing mode is supported.

- Take the <u>2's</u> complement of the subtrahend (source operand).

- Add it to the minuend (A).

- Invert the carry.

## Unsigned multiplication

- The two registers A & B are required for multiplication & Division.

- MUL AB; AxB, place 16 bit result in B & A

```

• A-13, B-06 MOV A, #25H ;load 25H to reg. A

• A-FA, B-12 MOV B, #65H ;load 65H in reg. B

MUL AB ;25H * 65H = E99 where

;B = OEH and A = 99H

```

# **Unsigned Division**

- In the division of unsigned numbers, the 8051 supports byte over byte only. 10/02

- The syntax is as follows.

DIV AB; Divide A by B

After the DIV instruction is performed, the quotient is in A and the remainder is in B

```

MOV A,#95 ;load 95 into A

MOV B,#10 ;load 10 into B

DIV AB .;now A = 09 (quotient) and

;B = 05 (remainder)

```