# Internal Assesment Test - IV

| Sub:  | DIGITAL SYSTE                                                                                                                                                 | EM DSESIO                                                       | SN                      |                 |           |           |                 | Cod    | e:   | 18EE | 35  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------|-----------------|-----------|-----------|-----------------|--------|------|------|-----|

| Date: | 21/03/2022                                                                                                                                                    | Duration:                                                       | 3 HRS                   | Max<br>Marks:   | 100       | Sem:      | 3 <sup>rd</sup> | Brai   | nch: | EEI  | (T) |

|       |                                                                                                                                                               |                                                                 | Answei                  | Any 10 Ques     | stions    |           |                 |        | _    |      |     |

|       |                                                                                                                                                               |                                                                 |                         |                 |           |           |                 |        | Mark | OI   |     |

| 4 50  |                                                                                                                                                               | 1                                                               | 0 : 14                  | G1 1 .1         | •         |           |                 |        |      | CO   | RBT |

|       | ind a minimum SOP so $(a,b,c,d)=\sum m(2,3,4,5,1)$                                                                                                            | _                                                               | -                       | Cluskey metho   | d         |           |                 |        | 10   | CO1  | L3  |

| 2 St  | taircase light is control<br>other at the bottom of<br>(a) Make a truth table<br>(b) Write the logic eq<br>(c) Realize the circuit<br>(d) Realize the circuit | the stair:<br>for this syste<br>uations in the<br>using basic g | m.<br>POS form<br>ates. | 1.              |           | and the   |                 |        | 10   | CO1  | L2  |

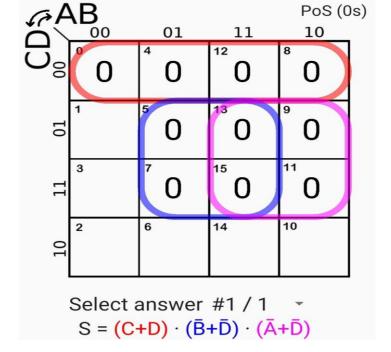

| 3 Si  | implify the following $v = f(a,b,c,d) = \pi M$                                                                                                                | •                                                               |                         |                 | logic:    |           |                 |        | 10   | CO1  | L3  |

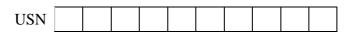

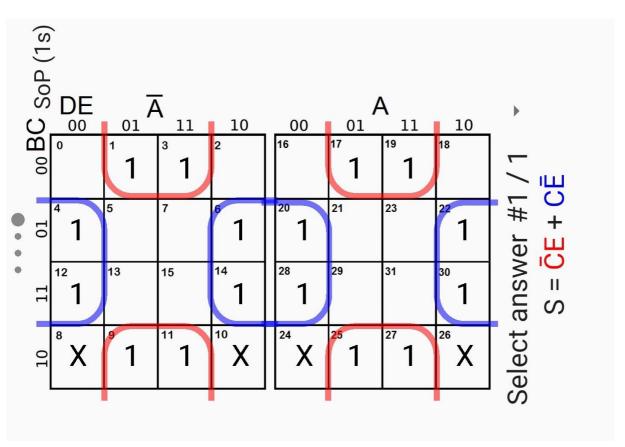

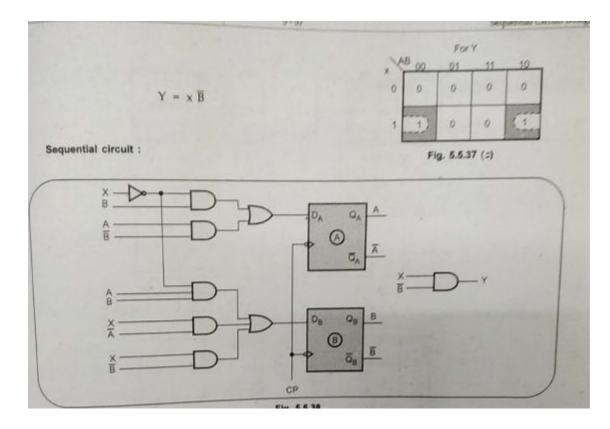

| 4 Si  | implify using K-Map $Y=f(a,b,c,d,e)=\sum m(1,$                                                                                                                | 3,4,6,9,11,12                                                   | ,14,17,192              | 20,22,25,27,28, | 30)+ ∑d   | (8,10,24  | 26)             |        | 10   | CO1  | L3  |

|       | ifferentiate synchrono<br>peration shift registers.                                                                                                           |                                                                 | hronous co              | ounter. Mention | n the fou | r differe | ent mo          | des of | f 10 | CO3  | L3  |

| 6 D   | esign a Mod 6 ripple c                                                                                                                                        | ounter using                                                    | T flip-flop             |                 |           |           |                 |        | 10   | CO3  | L3  |

| 7 D   | esign a synchronous co                                                                                                                                        | ounter with co                                                  | ounting sec             | quence 3,2,5,1, | 0,3usii   | ng D-flip | oflops          |        | 10   | CO3  | L3  |

|       | /ith a neat logic diag                                                                                                                                        | ram explain                                                     | the differ              | rent modes of   | operatio  | n of un   | iversa          | l shif | t 10 | CO3  | L3  |

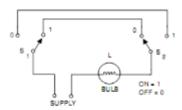

| ex    | nalyse the following scitation and output eq ate diagram.                                                                                                     | uation, transit                                                 |                         |                 |           |           | v.Obta          | in the | 10   | CO4  | L3  |

CCI HOD\

on: Step 1: List all minterms in bina, form.

| Minterms         | Bina | ary repre | esentatio | n |

|------------------|------|-----------|-----------|---|

| m <sub>2</sub>   | 0    | 0         | 1         | 0 |

| m <sub>3</sub>   | 0    | 0         | 1         | 1 |

| m <sub>4</sub>   | 0    | 1         | 0         | 0 |

| m <sub>5</sub>   | 0    | 1         | 0         | 1 |

| m <sub>13</sub>  | 1    | 1         | 0         | 1 |

| m <sub>15</sub>  | 1    | 1         | 1         | 1 |

| dm <sub>8</sub>  | 1    | 0         | 0         | 0 |

| dm <sub>9</sub>  | 1    | 0         | 0         | 1 |

| dm <sub>10</sub> | 1    | 0         | 1         | 0 |

| dm <sub>11</sub> | 1    | 0         | 1         | 1 |

Step 2: Arrange the minterms according to number of 1's.

| Minterms        | Binary | у гер | resent | tation |

|-----------------|--------|-------|--------|--------|

| m <sub>2</sub>  | 0      | 0     | 1      | 0      |

| m <sub>d</sub>  | 0      | 1     | 0      | 0      |

| mg              | 1      | 0     | 0      | 0      |

| m <sub>3</sub>  | 0      | 0     | 1      | 1      |

| m <sub>5</sub>  | .0     | 1     | 0      | 1      |

| mg              | 1      | 0     | 0      | 1      |

| m <sub>10</sub> | 1      | 0     | 1      | 0      |

| m <sub>11</sub> | 1      | 0     | 1      | 1      |

| m <sub>13</sub> | 1      | 1     | 0      | 1      |

| m <sub>15</sub> | 1      | 1     | 1      | 1      |

Step 3:

| Mi  | nten | m | Bina | гу гер | resent | tation |  |

|-----|------|---|------|--------|--------|--------|--|

| 2.  | 3    | 1 | 0    | 0      | 1      | -      |  |

| 2,  | 10   | 1 | -    | 0      | 1      | 0      |  |

| 4,  | 5    |   | 0    | 1      | 0      | -      |  |

| 8,  | 10   | 1 | 1    | 0      | -      | 0      |  |

| 8,  | 9    | 1 | 1    | 0      | 0      | 12     |  |

| 3,  | 11   | 1 | 71   | 0      | 1      | 1      |  |

| 5,  | 13   |   | -    | 1      | 0      | 1      |  |

| 9,  | 13   | 1 | 1    | -      | 0      | 1      |  |

| 9,  | 11   | 1 | 1    | 0      | -      | 1      |  |

| 10, | 11   | 1 | 1    | 0      | 1      | -      |  |

| 13. | 15   | 1 | 1    | 1      | 2      | 1      |  |

| 11. | 15   | 1 | 1    | 4      | 1      | -1     |  |

#### Step 4:

| ition | esenta | y repr | Minterm |    |     |     |    |  |  |

|-------|--------|--------|---------|----|-----|-----|----|--|--|

| -     | 1      | 0      | -       | 11 | 10, | 3,  | 2, |  |  |

| -     | -      | 0      | 1       | 11 | 10, | 9,  | 8, |  |  |

| 1     | -      | -      | 1       | 15 | 13, | 11, | 9, |  |  |

#### Step 5:

|   | P | rime imp | olicants      | Binary representation |   |   |   |  |  |

|---|---|----------|---------------|-----------------------|---|---|---|--|--|

| ā | ь | 5        | 4, 5          | 0                     | 1 | 0 | - |  |  |

| b | ē | d        | 5, 13         |                       | 1 | 0 | 1 |  |  |

| Б | c |          | 2, 3, 10, 11  | 0 mg                  | 0 | 1 | - |  |  |

| a | Б |          | 8, 9, 10, 11  | 1                     | 0 | - | - |  |  |

| a | d |          | 9, 11, 13, 15 | 1                     | - | - | 1 |  |  |

Step 6:

|   | Pri | me i | mplicants     | m <sub>2</sub> | m <sub>3</sub> | m <sub>4</sub> | m <sub>5</sub> | m <sub>13</sub> | m <sub>5</sub> | dm <sub>8</sub> | dm <sub>9</sub> | dm <sub>10</sub> | dm <sub>11</sub> |

|---|-----|------|---------------|----------------|----------------|----------------|----------------|-----------------|----------------|-----------------|-----------------|------------------|------------------|

| ā | b   | ē    | 4.5           |                |                | 0              | 0              |                 |                |                 |                 |                  |                  |

| b | ē   | d    | 5, 13         |                |                |                |                | 0.0             |                |                 |                 |                  |                  |

| Б | 0   |      | 2, 3, 10, 13  | 0              | 0              |                |                | 0               |                |                 |                 | 0                | 10.63            |

| a | Б   |      | 8, 9, 10, 11  |                |                |                |                |                 |                |                 | •               | •                |                  |

| a | d   |      | 9, 11, 13, 15 |                |                |                |                | 0               | 0              |                 | 0               |                  | 0                |

$Y = \bar{b} c + \bar{a} b \bar{c} + a d$

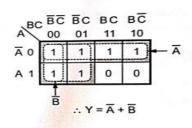

#### 2.

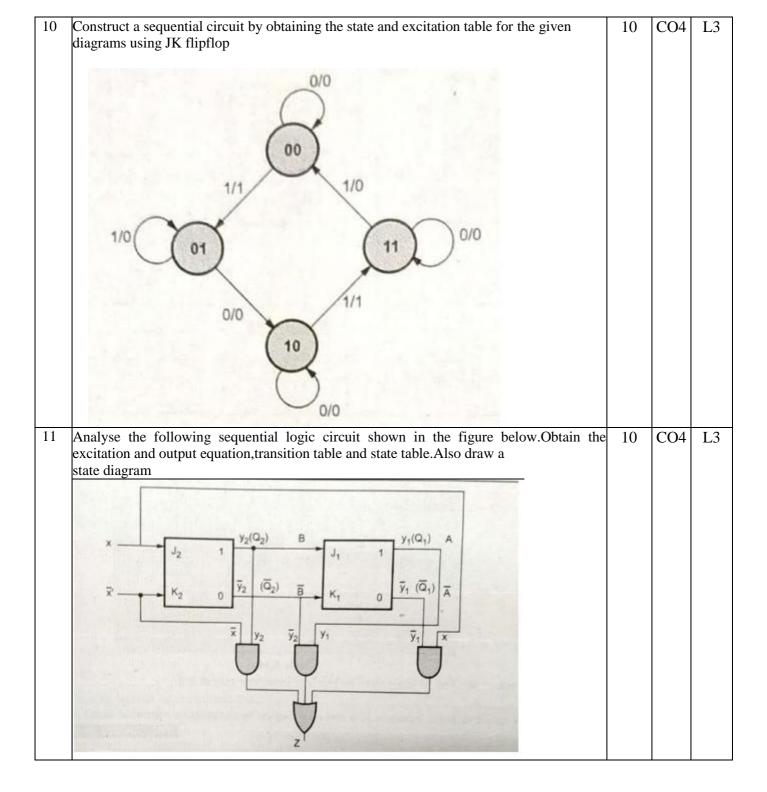

Fig.(a) Circuit diagram

a. The truth table for the system is illustrated in given truth table

| S1 | S2 | L |

|----|----|---|

| 0  | 0  | 0 |

| 0  | 1  | 1 |

| 1  | 0  | 1 |

| 1  | 1  | 0 |

- b. The logic equation for given system is specified by L =  $S_1^-S_2 + S_1^-S_2^-$

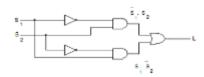

- c. Realization of given case, the circuit using AND-OR gates is demonstrated in fig (b)

Fig.(b) Logic Diagram for the system

4.

# Difference between Synchronous and Asynchronous Counter

| S.No. | Synchronous Counter                                                                                             | Asynchronous Counter                                                                   |

|-------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 1.    | In the synchronous counter there are continuous clock input signals with flip-flops used to produce the output. | In Asynchronous counters there are different clock signals used to produce the output. |

| 2.    | In the synchronous counter, the operation is faster.                                                            | In Asynchronous counter the operation is slower.                                       |

| 3.    | Synchronous counter is also known as Parallel counter.                                                          | Asynchronous counter is also known as Serial counter.                                  |

| 4.    | Synchronous counter produces less error than asynchronous counter.                                              | Asynchronous counter produces more errors than a synchronous counter.                  |

| 5.    | Design of the Synchronous counter is complex.                                                                   | Design of the Asynchronous counter is simple.                                          |

| 6.    | Synchronous counters can work with a flexible number of count sequences.                                        | Asynchronous counters can work with a fixed number of count sequences.                 |

# There are four basic modes of operation based on the movement of data in the Registers and they are:

- Serial In Serial Out (SISO) Mode.

- Serial In Parallel Out (SIPO) Mode.

- Parallel In Serial Out (PISO) Mode.

- Parallel In Parallel Out (PIPO) Mode.

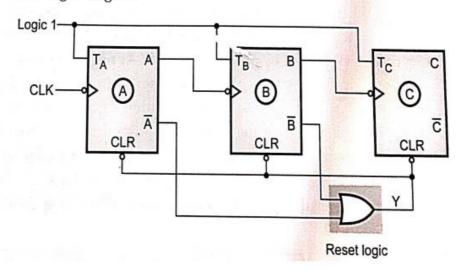

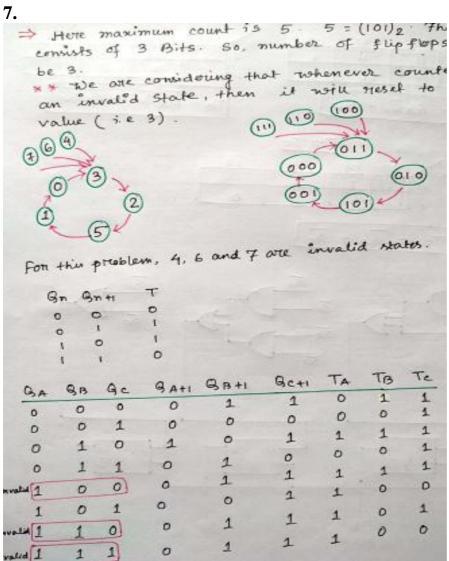

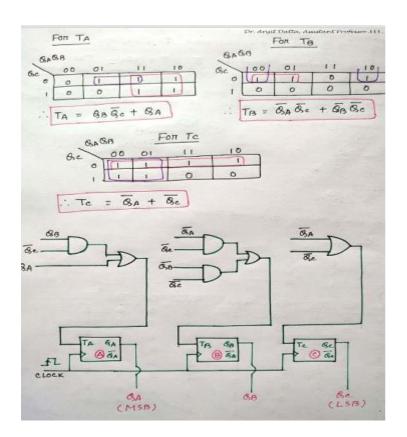

### **6.**

### Solution :

Step 1: Determine the number of flip-flop required. Here, counter goes through 0 - 5 states, i.e., total 6 states. Thus N = 6 and for  $2^n \ge N$  we need n = 3, i.e. 3 flip-flops.

Step 2: Type of flip-flops to be used: T

Step 3: Write the truth table for counter

**Output of** CLK A B C reset logic Y 0 0 0 0 1 0 1 1 0 0 Valid 3 states 0 1 1 1 4 1 0 1 5 1 1 1 1 0 0 Invalid states 0 1

Step 4: Derive reset logic

Step 5: Draw logic diagram

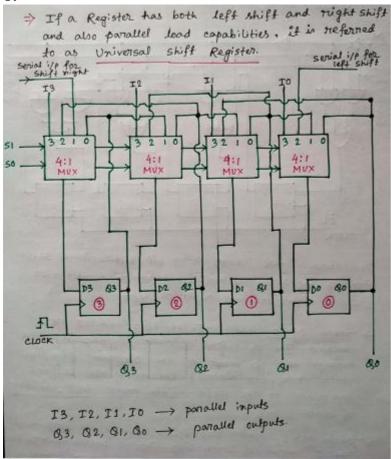

→ 94 consists of 4 flipflops and 4 Multiplezers. The Marie four Multiplezers have two common select inputs s1 and s0. and they select appropriate input for D flip-flop. The below table shows the negister operation depending on the select lines of multiplezer.

| Mode | Control | Register      |  |  |  |

|------|---------|---------------|--|--|--|

| 91   | So      | Operation     |  |  |  |

| 0    | 0       | No change     |  |  |  |

| 0    | 1       | shift Right   |  |  |  |

| 1    | D       | Shift Left    |  |  |  |

| 1    | 1       | parallel Load |  |  |  |

- > When \$150 = 00, input 0 is selected and the present value of the negister is applied to the D inputs of the flip-flops. This results no change in Register value.

- → when 5,50 = 01, input 1 is selected and eizewift connections are such that it operates as a right shift Register.

- Twhen S150 = 10, input 2 is selected and elecult connections are such that it operates as a left shift Register.

- Trinally when 5,50 = 11, the binary information on the parallel input lines is transferred into the negister simultaneously and it is a parallel load operation.

9.

Sol.: Step 1: Excitation and output equations.

$$Z = \underline{xQ_1}$$

$$T_1 = \underline{xQ_2} + \overline{x}Q_2 = \underline{x \oplus Q_2}$$

$$T_2 = \underline{xQ_1}$$

Step 2: Transition equations

The transition equation for T flip-flop is,

$$Q^+ = T \oplus Q$$

$Q_1^+ = x \oplus Q_2 \oplus Q_1$

$Q_2^+ = xQ_1 \oplus Q_2$

Step 3: Next state map for each flip-flop

|        | Q2 | For |       | Q;* |   |       |

|--------|----|-----|-------|-----|---|-------|

|        | 1  | 0   | 0,0,× | 1   | 0 | 0,0,0 |

| K-M    | 0  | 0   | 00    | 1   | 0 | 00    |

| Region | 1  | 0   | 01    | 0   | 1 | 01    |

| -      | 1  | 1   | 10    | 0   | 1 | 10    |

|        | 0  | 1   | 11    | 1   | 0 | 11    |

Step 4: Excitation table

| Present state  |                | 7335 | Next   | Next state Ou |     |       |   |  |

|----------------|----------------|------|--------|---------------|-----|-------|---|--|

| Q <sub>2</sub> | Q <sub>1</sub> | ×    | -0 x-1 |               | x-0 | x - 1 |   |  |

|                |                | Qį   | Qi     | Qž            | Qi  |       |   |  |

| 0              | 0              | 0    | 0      | 0             | 1   | 0     | 1 |  |

| 0              | 1              | 0    | 1      | 1             | 0   | 0     | 0 |  |

| 1              | 0              | 1    | 1      | 1             | 0   | 0     | 1 |  |

| 1              | 1              | 1    | 0      | 0             | 1   | 0     | 0 |  |

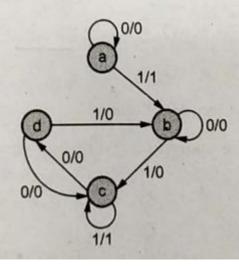

Step 5 : State table

Assuming a = 00, b = 01, c = 10 and d = 11 we have

| Present state | Next  | state | Output Z |       |  |

|---------------|-------|-------|----------|-------|--|

| riesent state | x = 0 | x = 1 | x = 0    | x = 1 |  |

| a             | a     | b     | 0        | 1     |  |

| ъ             | ъ     | c     | 0        | 0     |  |

| · c           | d     | c     | 0        | 1     |  |

| d             | , c   | ь     | 0        | 0     |  |

Step 6 : State diagram

11.

Sol.: The flip-flop input equations and output equations are,

$$\begin{split} J_2 = x & J_1 = y_2 & \text{and } z = \overline{x} \, y_2 + \overline{y_2} \, y_1 + \overline{y_1} \, x \\ K_2 = \overline{x} & K_1 = \overline{y_2} \end{split}$$

For JK flip-flop,

$$Q^+ = J\overline{Q} + \overline{K}Q$$

$$\begin{split} J_2^+ = Q_2^+ &= J_2 \overline{Q}_2 + \overline{K}_2 Q_2 \\ &= \times \overline{Q}_2 + \times Q_2 = \times \overline{y}_2 + \times y_2 \end{split}$$

$$= xQ_2 + xQ_2 = xy_2 + xy_2$$

$$J_1^+ = Q_1^+ = J_1 Q_1 + \overline{K}_1 Q_1$$

$$= y_2 \overline{Q}_1 + \overline{y_2} Q_1$$

$$= y_2 \overline{y}_1 + y_2 y_1$$

$$= y_2 (\overline{y}_1 + y_1) = y_2$$

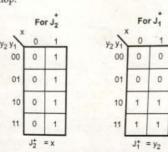

Next-state maps of each flip-flop.

Fig. 5.3.13 (a)

| Present state                 |                             | Next state |                  |    |       | Output z |   |

|-------------------------------|-----------------------------|------------|------------------|----|-------|----------|---|

| y <sub>2</sub> y <sub>1</sub> | x = 0                       |            | x=1              |    | x = 0 | x=1      |   |

|                               | y <sub>2</sub> <sup>+</sup> | УŤ         | y <sub>2</sub> + | y; |       |          |   |

| 0                             | 0                           | 0          | 0                | 1  | 0     | 0        | 1 |

| 0                             | 1                           | 0          | 0                | 1  | 0     | 1        | 1 |

| 1                             | 0                           | 0          | 1                | 1  | 1     | 1        | 1 |

| 1                             | 1                           | 0          | 1                | 1  | 1     | 1        | 0 |