CMR INSTITUTE OF TECHNOLOGY

| TICAL |  |  |  |  |  |

|-------|--|--|--|--|--|

|       |  |  |  |  |  |

| CDI   |  |  |  |  |  |

|       |  |  |  |  |  |

### **Internal Assesment Test - V**

| Sub:  | Power Electron                            | nics              |              |               |                    |            |       | Code:   |     | 18EE | 53  |

|-------|-------------------------------------------|-------------------|--------------|---------------|--------------------|------------|-------|---------|-----|------|-----|

| Date: | 07.02.2022                                | Duration:         | 90 mins      | Max<br>Marks: | 50                 | Sem:       | V     | Branch: |     | EEI  | Ξ   |

|       |                                           | A                 | nswer An     | y FIVE FU     | ULL Qu             | estions    |       |         |     |      |     |

|       |                                           |                   |              |               |                    |            |       |         | Mar |      | DBE |

|       |                                           |                   |              |               |                    |            |       |         | ks  | CO   | RBT |

|       | Explain working or<br>circuit diagram, in | • •               |              |               | c conve            | rters witl | h the | help of | 6   | CO1  | L2  |

|       | The power electr                          |                   |              |               | ix types           | :          |       |         |     |      |     |

|       | 1. Diode recti                            |                   |              |               | • <b>, , , ,</b> • |            |       |         |     |      |     |

|       | 2. Ac–dc con                              |                   |              | rs)           |                    |            |       |         |     |      |     |

|       | 3. Dc-dc conv                             |                   |              |               |                    |            |       |         |     |      |     |

|       | 4. Dc–ac conv<br>5. Ac–ac conv            |                   |              | lers)         |                    |            |       |         |     |      |     |

|       | 6. Static switch                          |                   | ige control  | 1015)         |                    |            |       |         |     |      |     |

|       |                                           | 4 5               |              |               |                    |            |       |         |     |      |     |

|       |                                           | 1. Dio            | de rec       | tifiers       |                    |            |       |         |     |      |     |

|       | • It con                                  | verts AC Vo       | Itage in     | to a FIXE     | D DC               |            |       |         |     |      |     |

|       | Voltag                                    |                   |              |               |                    |            |       |         |     |      |     |

|       |                                           | ,                 |              |               |                    |            |       |         |     |      |     |

|       |                                           |                   |              |               |                    |            |       |         |     |      |     |

|       |                                           |                   |              |               |                    |            |       |         |     |      |     |

|       |                                           |                   |              |               |                    |            |       |         |     |      |     |

|       |                                           |                   |              |               |                    |            |       |         |     |      |     |

|       |                                           |                   |              |               |                    |            |       |         |     |      |     |

|       | <ul> <li>Converts</li> </ul>              | fixed ac voltag   | e into fixed | l de voltage  | 2                  |            |       |         |     |      |     |

|       |                                           | uld be either sir |              | _             | •                  |            |       |         |     |      |     |

|       | · ·                                       | circuit for singl | _            | -             | r is show          | wn         |       |         |     |      |     |

|       | LAMITIPIC                                 | Dr.K.Chitr        | •            | ent of EEE    | 15 5110            |            |       |         |     |      |     |

|       |                                           | Di.N.Ciliti       | CMRIT        | CIT OF EEE    |                    | 4          | 1     |         |     |      |     |

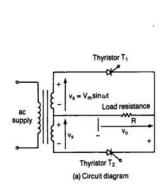

# Ac-dc converters (controlled rectifiers)

- A single-phase converter with two natural commutated thyristor is shown

- Average value of the output voltage can be controlled by varying the conduction time of thyristors

- This converters are also known as controlled rectifiers

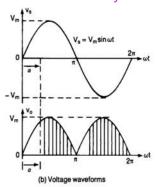

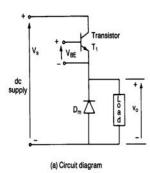

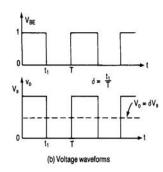

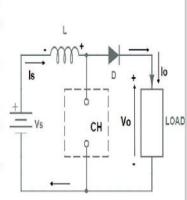

# Dc-dc converters (dc choppers)

- Is also known as Chopper or Switching Regulator

- The average output voltage is controlled by varying the conduction of transistor, t1.

- If T is the chopping period, then  $t1=\delta T$

- $\delta$  is called as the duty cycle of chopper

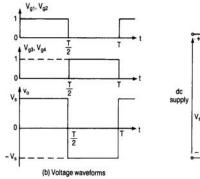

# **DC-AC Converters**

- Is also known as Inverter

- If transistor Q1 and Q2 conduct for one-half period and Q3 and Q4 conduct the other half, the output voltage is of alternating form

- Fixed dc voltage to variable ac voltage

- Voltage control is obtained by controlling duty cycle

- Also known as inverter

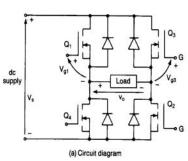

## **AC-AC Converters**

- AC Voltage Controller / Cyclo Converter

- Fixed AC source into variable AC output voltage

- a single-phase converter with a TRIAC is shown below

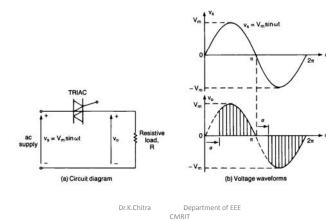

## **Static Switches**

- Power devices can be operated as static switches or contactors

- Supply to these switches could be either AC or DC

- The switches are called as AC static switches or DC switches

- Power electronic devices used as static switches in an UPS shown

- Mains 1 and 2 are connected to same supply

- Mains 1 supplies the load thro static bypass switch

- The rectifier charges the battery from Mains 2.

- The inverter supplies the emergency power to the load

1b Explain the peripheral effects of power electronic equipments.

CO<sub>1</sub>

L2

# **Harmonics**

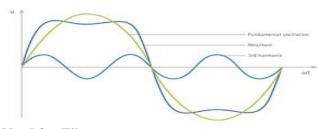

- **Harmonics** are unwanted higher frequencies which superimposed on the fundamental waveform (50 Hz) creating a distorted wave pattern.

- Harmonic is a

- voltage or current waveforms at a multiple of the fundamental frequency of the system,

- produced by the action of non-linear loads such as rectifiers, discharge lighting, or saturated magnetic devices.

- "harmonics" are multiples of the fundamental frequency f and can therefore be expressed as: 2f, 3f, 4f, etc.

12

**Need for Filter**

# Effects of Harmonics The operations of the power converters are based mainly on the switching of power semiconductor devices • As a result the converters introduce current and voltage

- As a result the converters introduce current and voltage harmonics into the supply system and on the output of the converters. These can cause

- > Problems of distortion of the output voltage and current

- > harmonic generation into the supply system

- Interference with the communication and signalling circuits.

- Harmonic frequencies in the power grid are a frequent cause of <u>power quality</u> problems.

- Increased heating in the equipment and conductors

- > Misfiring in variable speed drives

- > Torque pulsations in motors.

13

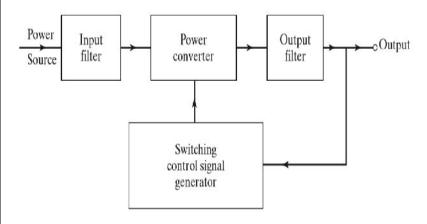

### **Need for filter**

• It is normally necessary to introduce filters on the input and output of a converter system to reduce the harmonic level to an acceptable magnitude.

# **Generalized Power Converter System**

2 Explain the function of a freewheeling diode in a switched RL load with the help of circuit diagram and waveforms.

10 CO1

L2

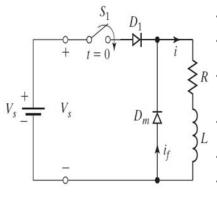

# Freewheeling diodes with RL Load

(a) Circuit diagram

D1 – Normal Diode Dm – Freewheeling Diode

- If switch S1 is closed for time t1, a current is established through the load;

- If the switch is opened, a path must be provided for the current in the inductive load.

- Otherwise, the inductive energy induces a very high voltage and this energy is dissipated as heat across the switch as sparks.

- This is normally done by connecting a diode Dm as shown in Figure, and this diode is usually called a freewheeling diode.

- Diode Dm is needed to prove a path for the inductive load current.

- Diode D1 is connected in series with the switch and it will prevent any negative current flow through the switch if there is an ac input supply voltage.

- But for dc supply, there is no need for D1.

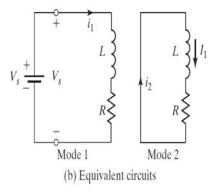

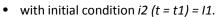

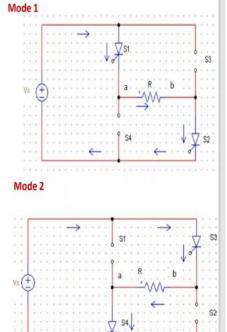

- The circuit operation can be divided into Two modes.

- Mode 1 begins when the switch is closed at t = 0

- Mode 2 begins when the switch is opened.

- The equivalent circuits for the modes are shown in Figure.

- Variables i1 and i2 are defined as the instantaneous currents for mode 1 and mode 2, respectively;

- t1 and t2 are the corresponding durations of these modes.

# Mode 1

• Diode current i1

$$i_1(t) = \frac{V_s}{R} \left( 1 - e^{-tR/L} \right)$$

• When the switch is opened at t = t1 (at the end of this mode),

$$I_1 = i_1(t = t_1) = \frac{V_s}{R} (1 - e^{-tR/L})$$

• If the time *t*1 is sufficiently long, the current practically reaches a steady-state current of Is = Vs/R flows through the load.

- This mode begins when the switch is opened and the load current starts to flow through the freewheeling diode Dm.

- Redefining the time origin at the beginning of this mode, th freewheeling diode mode, the is found f  $0 = L \frac{di_2}{dt} + Ri_2$

• With initial condition 12 (

$$t = t1$$

) = 11.

• the free  $i_2(t) = I_1 e^{-tR/L}$  i2 is given by

at t = t2 this current decays exponentially to practically zero provided that t2 > L/R.

Mode 1

### **Waveforms of Currents**

Explain steady state and switching characteristics of Power MOSFET. 10 CO<sub>2</sub> L2

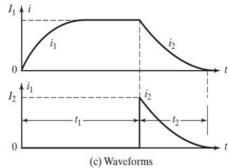

# **Steady-State Characteristics**

- The MOSFETs are voltage-controlled devices and have a very high input impedance.

- The gate draws a very small leakage current, on the order of nano amperes.

- The current gain, which is the ratio of drain current ID to input gate current IG, is typically on the order of 109.

- The transconductance, which is the ratio of drain current to gate voltage, defines the transfer characteristics and is a very important parameter. gm =  $\Delta I_D / \Delta V_{GS}$ , when VDS is constant.

- Drain current is calculated as

$$i_D = K_n (v_{GS} - V_T)^2$$

for  $v_{GS} > V_T$  and  $v_{DS} \ge (v_{GS} - V_T)$

where  $K_n$  is the MOS constant, A/V<sup>2</sup>  $v_{GS}$  is the gate-to-source voltage, V  $V_T$  is the threshold voltage, V

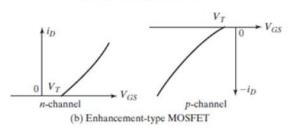

# Transfer characteristics of MOSFETs

(a) Depletion-type MOSFET

### Output characteristics - Enhancement-type MOSFET

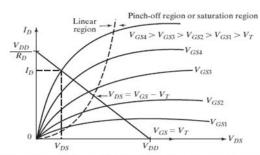

There are three regions of operation: (1) cutoff region, where  $V_{GS} \leq V_T$ ; (2) pinch-off or saturation region, where  $V_{DS} \ge V_{GS} - V_T$ ; and (3) linear region, where  $V_{DS} \leq V_{GS} - V_T$ . The pinch-off occurs at  $V_{DS} = V_{GS} - V_T$ .

The load line of a MOSFET with a load resistance  $R_D$  can be described by

$$i_D = \frac{V_{DD} - v_{DS}}{R_D}$$

where  $i_D=V_{DD}/R_D$  at  $v_{DS}=0$  and  $v_{DS}=V_{DD}$  at  $i_D=0$ In order to keep the value of  $V_{DS}$  low, the gate–source voltage  $V_{GS}$  must be higher so that the transistor operates in the linear region.

### Output characteristics - Enhancement-type MOSFET

There are three regions of operation: (1) cutoff region, where  $V_{GS} \leq V_T$ ; (2) pinch-off or saturation region, where  $V_{DS} \ge V_{GS} - V_T$ ; and (3) linear region, where  $V_{DS} \leq V_{GS} - V_T$ . The pinch-off occurs at  $V_{DS} = V_{GS} - V_T$ .

The load line of a MOSFET with a load resistance  $R_D$  can be described by

$$i_D = \frac{V_{DD} - v_{DS}}{R_D}$$

where  $i_D=V_{DD}/R_D$  at  $v_{DS}=0$  and  $v_{DS}=V_{DD}$  at  $i_D=0$ In order to keep the value of  $V_{DS}$  low, the gate–source voltage  $V_{GS}$  must be higher so that the transistor operates in the linear region.

# Switching Characteristics of MOSFETs Parasitic model of enhancement of MOSFETs

- Without any gate signal, the enhancement-type MOSFET may be considered as two diodes connected back to back (np and pn diodes) or as an NPN-transistor.

- The gate structure has parasitic capacitances to the source, Cgs, and to the drain, Cgd.

- The NPN-transistor has a reverse-bias junction from the drain to the source and offers a capacitance, Cds.

- Hence, a MOSFET may be considered as having an internal diode and the parasitic capacitances are dependent on their respective voltages.

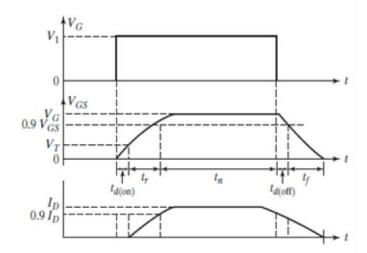

# Switching waveforms and times

| Definitions                                                                                                                                                                                   |                                                                                     |     |   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-----|---|

| Delay time t <sub>d(on)</sub> / Turn on Delay time is the the input capacitance to threshold voltage.                                                                                         | time that is required to charge                                                     |     |   |

| <ul> <li>It is time taken by the VGS increases from 0</li> </ul>                                                                                                                              |                                                                                     |     |   |

| <ul> <li>Rise time tr is the gate-charging time fron<br/>gate voltage V<sub>GSP</sub>, which is required to dri<br/>region.</li> </ul>                                                        | n the threshold level to the full-                                                  |     |   |

| <ul> <li>It is time taken by ID to increase from 0 to<br/>VGSp (Full gate voltage)</li> </ul>                                                                                                 | 90% & VGS increase from VT to                                                       |     |   |

| <ul> <li>Turn-off delay time t<sub>d(off)</sub> / storage time is<br/>capacitance to discharge from the overdriv<br/>off region.</li> </ul>                                                   | the time required for the input<br>ve gate voltage V1 to the pinch-                 |     |   |

| It is time taken by ID to decrease from 100 VGS to VGSp (Full gate voltage)  • It is time taken by ID to decrease from 100 vGS to VGSp (Full gate voltage)                                    | % to 90% & VGS decrease from                                                        |     |   |

| Fall time tf is the time that is required discharge from the pinch-off region to thre                                                                                                         |                                                                                     |     |   |

| It is time taken by ID to decrease from 9 VGSp to 0.  (6)                                                                                                                                     | 0% to 0 & VGS decrease from                                                         |     |   |

| <ul> <li>If VGS ≤ VT, transistor turns off.</li> </ul>                                                                                                                                        |                                                                                     |     |   |

| Explain the two-transistor analogy, and de of thyristor.                                                                                                                                      | rive an expression for the anode current 10                                         | CO3 | I |

|                                                                                                                                                                                               |                                                                                     | CO3 | I |

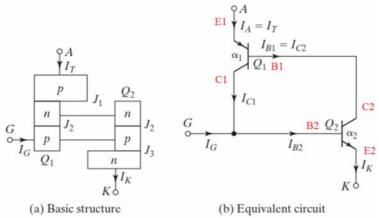

| of thyristor.  Two-transistor Model of Th                                                                                                                                                     | nyristor                                                                            | CO3 | I |

| of thyristor.                                                                                                                                                                                 | nyristor  on due to a positive feedback                                             | CO3 | I |

| of thyristor.  Two-transistor Model of The  The regenerative or latching action be demonstrated by using a                                                                                    | on due to a positive feedback two-transistor model of                               | CO3 | I |

| <ul> <li>of thyristor.</li> <li>Two-transistor Model of The The regenerative or latching action can be demonstrated by using a thyristor.</li> <li>A thyristor can be considered a</li> </ul> | on due to a positive feedback two-transistor model of two complementary transistors | CO3 | I |

| <ul> <li>of thyristor.</li> <li>Two-transistor Model of The The regenerative or latching action can be demonstrated by using a thyristor.</li> </ul>                                          | on due to a positive feedback two-transistor model of two complementary transistors | CO3 | I |

| <ul> <li>of thyristor.</li> <li>Two-transistor Model of The The regenerative or latching action can be demonstrated by using a thyristor.</li> <li>A thyristor can be considered a</li> </ul> | on due to a positive feedback two-transistor model of two complementary transistors | CO3 | I |

| <ul> <li>of thyristor.</li> <li>Two-transistor Model of The The regenerative or latching action can be demonstrated by using a thyristor.</li> <li>A thyristor can be considered a</li> </ul> | on due to a positive feedback two-transistor model of two complementary transistors | CO3 | I |

| <ul> <li>of thyristor.</li> <li>Two-transistor Model of The The regenerative or latching action can be demonstrated by using a thyristor.</li> <li>A thyristor can be considered a</li> </ul> | on due to a positive feedback two-transistor model of two complementary transistors | CO3 | I |

| <ul> <li>of thyristor.</li> <li>Two-transistor Model of The The regenerative or latching action can be demonstrated by using a thyristor.</li> <li>A thyristor can be considered a</li> </ul> | on due to a positive feedback two-transistor model of two complementary transistors | CO3 | I |

| <ul> <li>of thyristor.</li> <li>Two-transistor Model of The The regenerative or latching action can be demonstrated by using a thyristor.</li> <li>A thyristor can be considered a</li> </ul> | on due to a positive feedback two-transistor model of two complementary transistors | CO3 | I |

## Two-transistor Model of Thyristor

Two-transistor model of thyristor.

Dr.K.Chitra

Department of EEE

l

The collector current  $I_C$  of a thyristor is related, in general, to the emitter current  $I_E$  and the leakage current of the collector–base junction,  $I_{CBO}$ , as

$$I_C = \alpha I_E + I_{CBO} \tag{9.1}$$

and the *common-base current* gain is defined as  $\alpha \simeq I_C/I_E$ . For transistor  $Q_1$ , the emitter current is the anode current  $I_A$ , and the collector current  $I_{C1}$  can be found from Eq. (9.1):

# Derivation from Eq. (9.1): of Anode Current where $\alpha_1$ is the

$$I_{C1} = \alpha_1 I_A + I_{CBO1} \tag{9.2}$$

where  $\alpha_1$  is the current gain and  $I_{CBO1}$  is the leakage current for  $Q_1$ . Similarly, for transistor  $Q_2$ , the collector current  $I_{C2}$  is

$$I_{C2} = \alpha_2 I_K + I_{CBO2} \tag{9.3}$$

where  $\alpha_2$  is the current gain and  $I_{CBO2}$  is the leakage current for  $Q_2$ . By combining  $I_{C1}$  and  $I_{C2}$ , we get

$$I_A = I_{C1} + I_{C2} = \alpha_1 I_A + I_{CBO1} + \alpha_2 I_K + I_{CBO2}$$

(9.4)

For a gating current of  $I_G$ ,  $I_K = I_A + I_G$  and solving Eq. (9.4) for  $I_A$  gives

$$I_A = \frac{\alpha_2 I_G + I_{CBO1} + I_{CBO2}}{1 - (\alpha_1 + \alpha_2)} \tag{9.5}$$

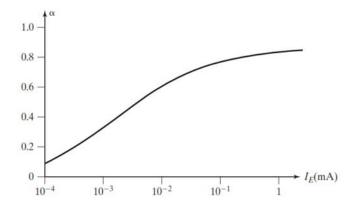

### Variation of Current Gain with Emitter Current

Typical variation of current gain with emitter current.

Dr.K.Chitra

Department of EEE

CMRIT

16

| The current gain $\alpha_1$ varies with the emitter current $I_A = I_E$ ; and $\alpha_2$ varies with $I_K = I_A + I_G$ .  If the gate current $I_G$ is suddenly increased, say from 0 to 1 mA, this immediately increases anode current $I_A$ , which would further increase $\alpha_1$ and $\alpha_2$ . Current gain $\alpha_2$ depends on $I_A$ and $I_G$ .  The increase in the values of $\alpha_1$ and $\alpha_2$ further increases $I_A$ .  Therefore, there is a regenerative or positive feedback effect. If $(\alpha_1 + \alpha_2)$ tends to be unity, the denominator of Eq. $I_A = \frac{\alpha_2 I_G + I_{CBO1} + I_{CBO2}}{1 - (\alpha_1 + \alpha_2)}$ approaches zero, resulting in a large value of anode current $I_A$ , and the thyristor turns on with a small gate current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| If the gate current $I_G$ is suddenly increased, say from 0 to 1 mA, this immediately increases anode current $I_A$ , which would further increase $\alpha_1$ and $\alpha_2$ . Current gain $\alpha_2$ depends on $I_A$ and $I_G$ .  The increase in the values of $\alpha_1$ and $\alpha_2$ further increases $I_A$ .  Therefore, there is a regenerative or positive feedback effect. If $(\alpha_1 + \alpha_2)$ tends to be unity, the denominator of Eq. $I_A = \frac{\alpha_2 I_G + I_{CBO1} + I_{CBO2}}{1 - (\alpha_1 + \alpha_2)}$ approaches zero, resulting in a large value of anode current $I_A$ , and the thyristor turns on with a small gate current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Therefore, there is a regenerative or positive feedback effect. If $(\alpha_1 + \alpha_2)$ tends to be unity, the denominator of Eq. $I_A = \frac{\alpha_2 I_G + I_{CBO1} + I_{CBO2}}{1 - (\alpha_1 + \alpha_2)}$ approaches zero, resulting in a large value of anode current $I_A$ , and the thyristor turns on with a small gate current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| If $(\alpha_1 + \alpha_2)$ tends to be unity, the denominator of Eq. $I_A = \frac{\alpha_2 I_G + I_{CBO1} + I_{CBO2}}{1 - (\alpha_1 + \alpha_2)}$ approaches zero, resulting in a large value of anode current $I_A$ , and the thyristor turns on with a small gate current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| resulting in a large value of anode current $I_A$ , and the thyristor turns on with a small gate current.  Dr.K.Chitra Department of EEE CMRIT 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| and the thyristor turns on with a small gate current.  Dr.K.Chitra Department of EEE CMRIT 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| Dr.K.Chitra Department of EEE CMRIT 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ļ    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| 5 Explain single phase fully controlled converter with RLE load with neat diagram and waveform and derive the expression for average and RMS voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4 L2 |

| $ \begin{array}{c} \downarrow \\ \downarrow \\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| Volume $V_{\text{ba}}$ |      |

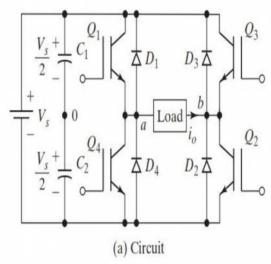

| <ul> <li>During the positive half-cycle</li> <li>The fully controlled bridge converter consists of four thyristors T1, T2, T3</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| and T4 connected in the form of full wave bridge configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| Each thyristor is controlled and turned on by its gating signal and naturally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

turns off when a reverse voltage appears across it (Line commutation or Natural commutation).

- Thyristors T1 and T2 are forward biased (0 to );

- when these two thyristors are turned on simultaneously at t = 0, the load is connected to the input supply through T1 and T2.

- Due to the inductive load, thyristors T1 and T2 continue to conduct beyond t =, even though the input voltage is already negative.

- T1 and T2 conduct from t = to +

- The output voltage across the load follows the input voltage vo = vm sin t

### During the negative half-cycle of the input voltage

- Thyristors T3 and T4 are forward biased ( to 2 );

- Turning on of thyristors T3 and T4 applies the supply voltage across thyristors T1 and T2 as reverse blocking voltage.

- T3 & T4 are triggered at t = +

- T1 and T2 are turned off due to line or natural commutation.

- The output voltage across the load follows the input voltage  $vo = -vm \sin t$

- Load current is transferred from T1 and T2 toT3 and T4.

- T3 and T4 conduct from t = + to 2 +

- During next half cycle T3 and T4 are turned off

### During Period from to - Rectification mode

- The input voltage vs and input current is are positive,

- Power flows from the supply to the load.

- The converter is said to be operated in *rectification* mode.

### During Period from to + - Inversion mode

- The input voltage vs is negative and the input current is is positive,

- Reverse power flows from the load to the supply.

- The converter is said to be operated in inversion mode.

- This converter is extensively used in industrial applications up to 15 kW.

- Depending on the value of , the average output voltage could be either positive or negative and it provides two-quadrant operation.

### **Average Output Voltage Vdc**

| $V_{O(dc)} = V_{dc} = \frac{2}{2\pi} \left[ \int_{\alpha}^{\pi+\alpha} V_m \sin \omega t . d(\omega t) \right]$ $V_{O(dc)} = V_{dc} = \frac{1}{\pi} \left[ \int_{\alpha}^{\pi+\alpha} V_m \sin \omega t . d(\omega t) \right]$ $V_{O(dc)} = V_{dc} = \frac{V_m}{\pi} \left[ \int_{\alpha}^{\pi+\alpha} \sin \omega t . d(\omega t) \right]$ $V_{O(dc)} = V_{dc} = \frac{V_m}{\pi} \left[ \int_{\alpha}^{\pi+\alpha} \sin \omega t . d(\omega t) \right]$ Therefore $V_{O(dc)} = V_{dc} = \frac{V_m}{\pi} \left[ -\cos \omega t \right]_{\alpha}^{\pi+\alpha}$ RMS Output Voltage Vrms |    |     |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|----|

| The rms value of the output voltage is given by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |     |    |

| $V_{\rm rms} = \left[\frac{2}{2\pi} \int_{\alpha}^{\pi+\alpha} V_m^2 \sin^2 \omega t  d(\omega t)\right]^{1/2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |     |    |

| $= \left[\frac{V_m^2}{2\pi} \int_{\alpha}^{\pi + \alpha} (1 - \cos 2\omega t) \ d(\omega t)\right]^{1/2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |     |    |

| $=\frac{V_m}{\sqrt{2}}=V_s$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |     |    |

| With a purely resistive load, thyristors $T_1$ and $T_2$ can conduct from $\alpha$ to $\pi$ , and thyristors $T_3$ and $T_4$ can conduct from $\alpha + \pi$ to $2\pi$ .                                                                                                                                                                                                                                                                                                                                                                                                              |    |     |    |

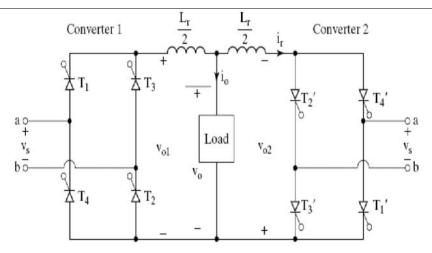

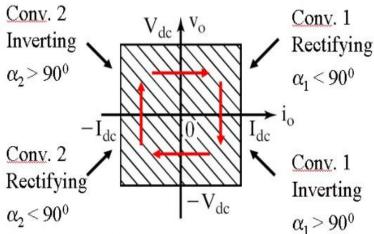

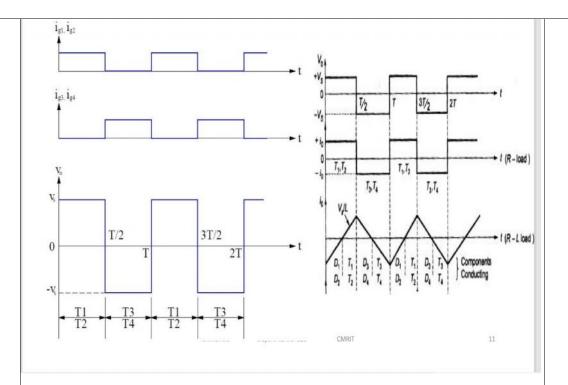

| 6 Illustrate the single-phase dual converter with neat diagram and waveform and also explain the significance of circulating current in dual converter.                                                                                                                                                                                                                                                                                                                                                                                                                               | 10 | CO4 | L2 |

| Dual converter- the name itself indicates that it has two converters in it.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |     |    |

| The dual converter system will provide four quadrant operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |     |    |

| Normally used in high power industrial variable speed drives.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |     |    |

| • In the case of a single phase full converter with inductive loads, the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |     |    |

| converter can operate in two different quadrants in the <i>Vdc</i> versus <i>Idc</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |     |    |

| <ul><li>operating diagram.</li><li>If two single phase full converters are connected in parallel and in opposite</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |     |    |

| direction (connected in back to back) across a common load four quadrant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |     |    |

| operation is possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |     |    |

| Such a converter is called as a dual converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |     |    |

• Two single phase full converters are connected in parallel and in opposite direction (connected in back to back) across a common load

### Converter 1

- The converter number 1 provides a positive dc output voltage and a positive dc load current, when operated in the rectification mode.

- The converter number 1 provides a negative dc output voltage and a positive dc load current, when operated in the inverter mode.

#### Converter 2

- The converter number 2 provides a negative dc output voltage and a negative dc load current when operated in the rectification mode.

- The converter number 2 provides a positive dc output voltage and a negative dc load current when operated in the inverter mode.

- We can have bi- directional load current and bi-directional dc output voltage.

- The magnitude of output dc load voltage and the dc load current can be controlled by varying the trigger angles 1 & 2 of the converters 1 and 2 respectively.

- 1 Firing angle for converter 1

- 2 Firing angle for converter 2

Fig.: Four quadrant operation of a dual converter

### CIRCULATING CURRENT

- In this mode of operation both the converters 1 and 2 are switched on and operated simultaneously and both the converters are in a state of conduction.

- If converter 1 is operated as a controlled rectifier by adjusting the trigger angle  $_1$  between 0 to 90° (0<  $_1$ < 90°)

- The second converter 2 is operated as a line commutated inverter by increasing its trigger angle <sub>2</sub> above 90 (90°< <sub>2</sub><180°).

| • The trigger angles 1 and 2 are adjusted such that they produce the same       |   |     |   |

|---------------------------------------------------------------------------------|---|-----|---|

| average dc output voltage across the load terminals.                            |   |     |   |

| • Instantaneous output voltages of two converters are out of phase , this       |   |     |   |

| voltage difference causes circulating current between two converters.           |   |     |   |

| This cannot flow through the load, and it is limited by limiting reactor.       |   |     |   |

| • In the circulating current mode a current builds up between the two           |   |     |   |

| converters even when the load current falls to zero.                            |   |     |   |

| • In order to limit the circulating current flowing between the two converters, |   |     |   |

| we have to include current limiting reactors in series between the output       |   |     |   |

| terminals of the two converters.                                                |   |     |   |

| Significance of circulating current                                             |   |     |   |

| • We can have faster reversal of load current as the two converters are in a    |   |     |   |

| state of conduction simultaneously.                                             |   |     |   |

| • This greatly improves the dynamic response of the output giving a faster      |   |     |   |

| dynamic response.                                                               |   |     |   |

| • The output voltage and the load current can be linearly varied by adjusting   |   |     |   |

| the trigger angles 1 and 2 to obtain a smooth and linear output control.        |   |     |   |

| The control circuit becomes relatively simple.                                  |   |     |   |

| <ul> <li>Output response is very fast.</li> </ul>                               |   |     |   |

| • The load current is free to flow in either direction at any time.             |   |     |   |

| The reversal of the load current can be done in a faster and smoother way.      |   |     |   |

|                                                                                 |   |     |   |

| Explain working of step-down chopper. Draw the relevant waveform. Derive an     | 5 | CO5 | L |

| expression for average and output rms voltage.                                  |   |     |   |

|                                                                                 |   |     |   |

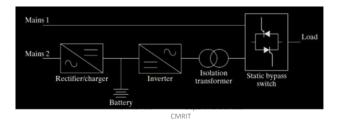

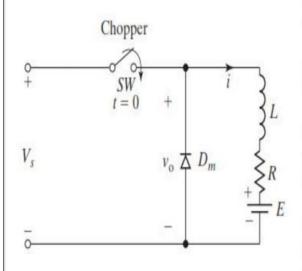

# Step-down Chopper with RL Load

A dc-dc converter with an *RL* load is shown in Figure.

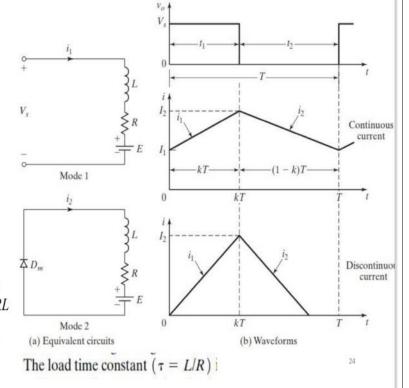

The operation of the converter can be divided into two modes.

During mode 1, the converter is switched on and the current flows from the supply to the load.

$\triangleright$  During mode 2, the converter is switched off and the load current continues to flow through freewheeling diode D

# Modes of Operation

Current may be

- Continuous

- Discontinuous

### Assumption

load current rises linearly.

However, the current flowing through an *RL* load rises or falls exponentially with a time constant.

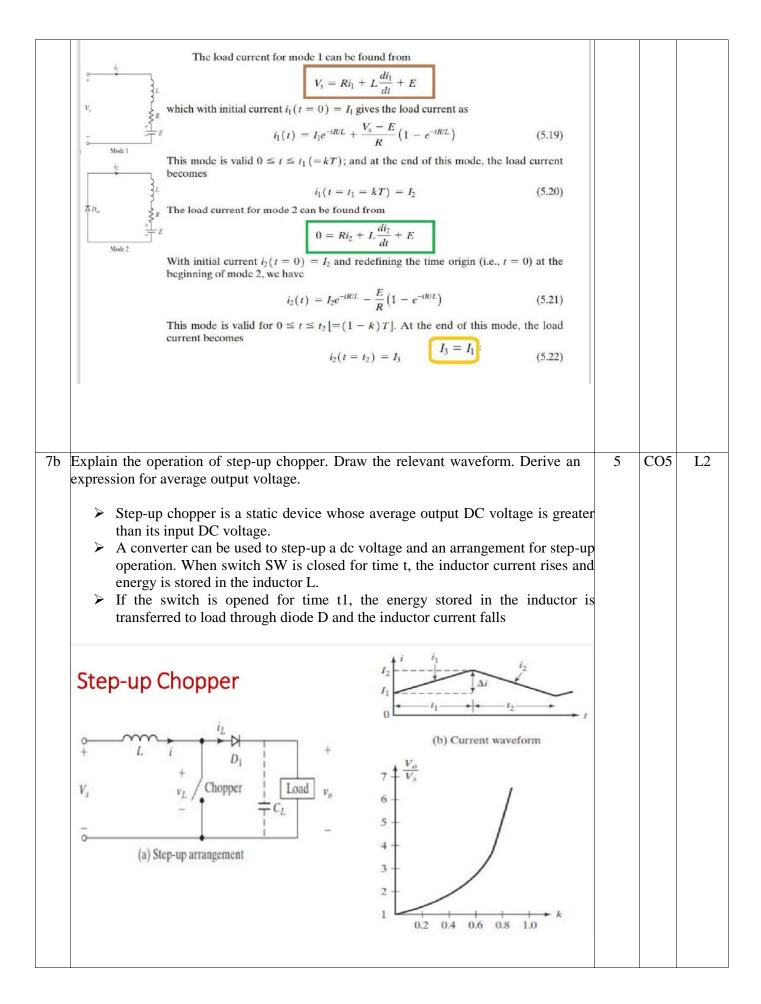

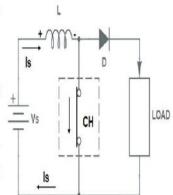

# Mode 1: Switch is ON

- When chopper (CH) is switched ON, the <u>current</u> will flow through the closed path formed by supply source Vs, <u>inductor</u> L and chopper CH.

- During this period, no current will flow through the load.

- Only source current i<sub>s</sub> will flow and the value of load current i<sub>o</sub> will be ZERO during the ON period.

- Also, during the T<sub>ON</sub> period, energy is stored in the inductor L.

- This energy storage in L is essential to boost the load output voltage above the source voltage.

- Therefore, a large value of L is essential in a step-up chopper.

# Mode 2: Switch is OFF

- When the chopper CH is switched OFF, the current through the L can not reduce instantaneously rather it decays exponentially.

- Due to this behavior of L, it will force the current through the diode D and load for the entire time period T<sub>DEF</sub>.

- Since, the current through the inductor L tends to decrease, the polarity of the emf induced in inductor L is reversed as shown in above figure.

- As a result, the voltage across the load becomes equal to the sum of source voltage and emf induced in inductor.

- $\bullet\,$  Thus, the output voltage exceeds the source voltage  $V_s.$

- The load / output voltage may be written as below.

$$V_0 = V_s + L(di/dt)$$

|   | Average<br>Output<br>Voltage<br>Equation                                                                                                                                                                    | When the converter is turned on, the voltage across the inductor is $v_L = L\frac{di}{dt} \implies di = \frac{v_L}{L} dt = \frac{V_s}{L} t_1$ and this gives the peak-to-peak ripple current in the inductor as $\Delta I = \frac{V_s}{L} t_1$ The average output voltage is $v_o = V_s + L\frac{\Delta I}{t_2} \qquad \qquad \Delta I = \frac{V_s}{L} t_1$ $= V_s \left(1 + \frac{t_1}{t_2}\right) = V_s \left(1 + \frac{k  \text{T}}{(1 - k )  \text{T}}\right) \qquad t_2 = (1 - k )  \text{T}$ $= V_s \frac{1}{1 - k}$ $v_o = V_s \frac{1}{1 - k}$ K value can be changed from 0 to 1.                                |    |     |    |