USN

18EE35

# Third Semester B.E. Degree Examination, Feb./Mar. 2022 Digital System Design

WGITime: 3 hrs.

CMR

Max. Marks: 100

Note: Answer any FIVE full questions, choosing ONE full question from each module.

#### Module-1

1 a. Explain the definition of combinational logic. Convert the given Boolean expression into minterm canonical form and maxterm canonical form.

$$F(x, y, z) = X + \bar{x} \,\bar{z}(y+z).$$

(08 Marks)

b. Simplify the function:

$Y = f(a, b, c, d) = \sum m(2, 3, 4, 5, 13, 15) + \sum d(8, 9, 10, 11)$  using Karnaugh map. (06 Marks)

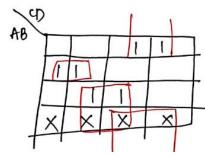

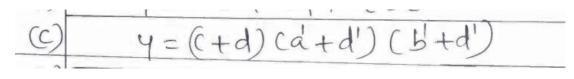

c. Simplify the function:

$Y = f(a, b, c, d) = \pi M(0, 4, 5, 7, 8, 9, 11, 12, 13, 15)$  using the Karnaugh map. (06 Marks)

#### OR

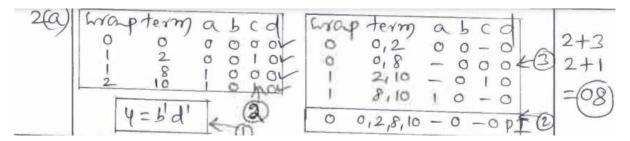

2 a. Simplify wing the Quine – McClusky minimization technique:

$Y = f(a, b, c, d) = \Sigma m(0, 2, 8, 10).$

(08 Marks)

b. Using the Quine – McCluskey method, obtain all the prime implicates for the following Boolean function:

$$f(a, b, c, d) = \pi M(0, 2, 3, 4, 5, 12, 13) + dc(8, 10)$$

(12 Marks)

#### Module-2

3 a. With the aid of general structure, clearly distinguish between a decoder and encoder.

(06 Marks)

b. Implement the following Boolean function using 4:1 multiplexer.

$F(A, B, C) = \Sigma m(1, 3, 5, 6)$

(06 Marks)

c. Implement full subtractor using a decoder and two NAND gates and write its truth table.

(08 Marks)

#### OR

4 a. What is carry look ahead adder? Explain general organization of it.

(06 Marks)

b. Write a truth table for two – bit magnitude comparator. Write the Karnaugh map for each output of two bit magnitude comparator and the resulting equation. (14 Marks)

Module-3

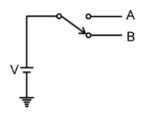

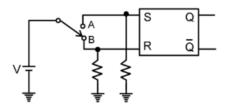

- 5 a. What is a Flip-Flop? Discuss the working principle of SR Flip Flop with its truth table. Also high light the role of SR Flip Flop in switch debouncer circuit. (12 Marks)

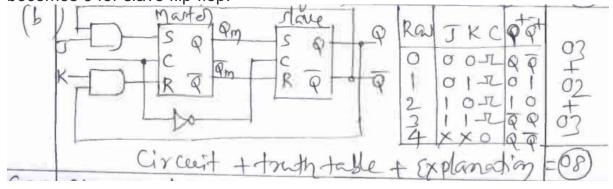

- b. Explain the operation of Master Slave JK flip-flop along with its circuit diagram. (08 Marks)

#### OR

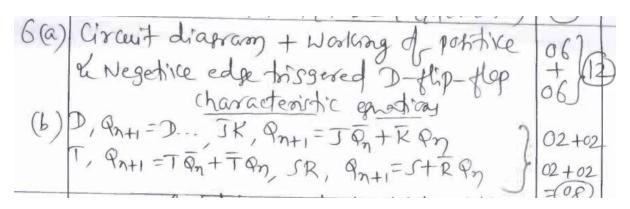

6 a. Draw and explain the working of Positive and Negative edge triggered D flip-flop. (12 Marks)

b. Derive the characteristic equations for D, JK, T and SR flip flops.

(08 Marks)

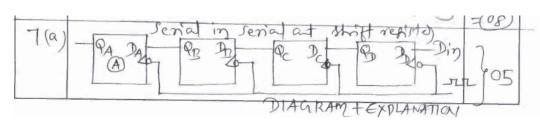

- 7 a. Explain with suitable logic and timing diagram

- i) Serial-in serial-out shift register

ii)Parallel-in parallel out shift register.

(10 Marks)

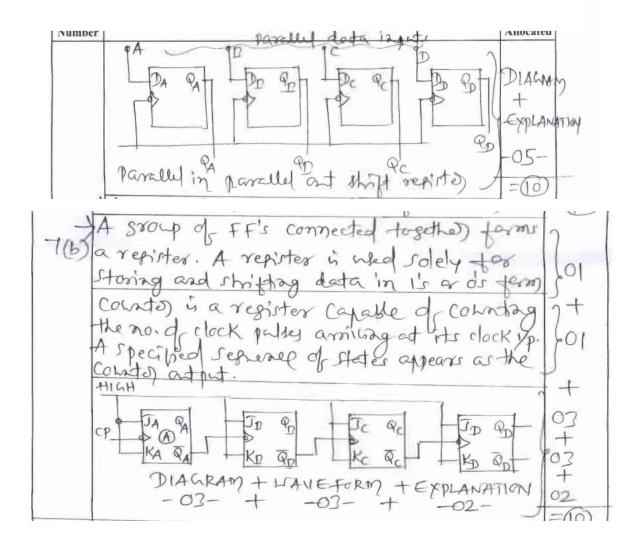

b. Compare Registers and Counters. Explain the working of 4-bit Asynchronous counter using JK flip-flops. (10 Marks)

OR

- 8 a. Describe the block diagram of a MOD 7 Jonson counter and explain its operation. Give the count sequence table and the decoding logic used to identify the various states. (10 Marks)

- b. Design a MOD 5 synchronous binary counter using clocked J-K flip-flops.

(10 Marks)

Module-5

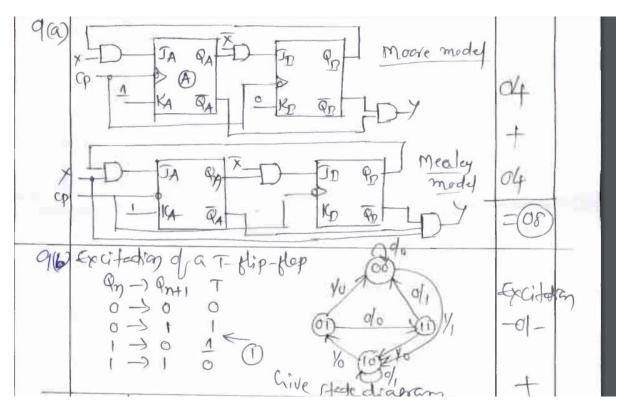

- 9 a. With a suitable example, explain Mealy and Moore model in a sequential circuit analysis.

(08 Marks)

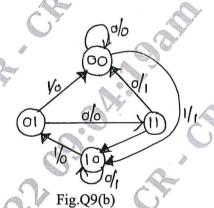

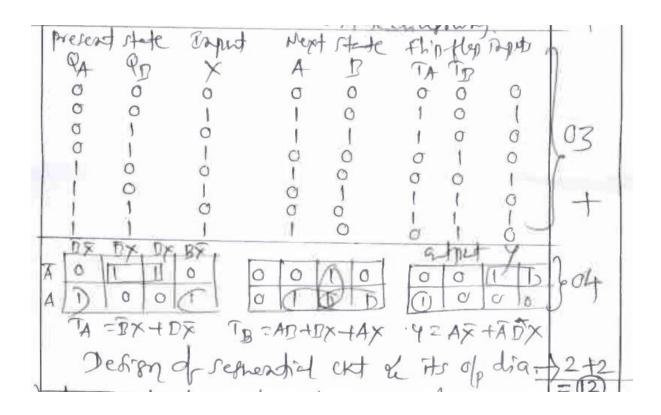

- b. A sequential circuit has one input and one output. The state diagram is as shown in Fig.Q9(b). Design a sequential circuit with 'T' flip-flop.

(12 Marks)

OR

- 10 a. With a basic structure, explain clearly Programmable Read Only Memories (PROMS) and EPROM. (13 Marks)

- b. Write short note on:

- i) Read only and Read/Write memories

- ii) Flash memory.

(07 Marks)

CMRIT LIBRARY BANGALORE - 560 037

**1a.**Combinational circuit is a circuit in which we combine the different gates in the circuit, for example encoder, decoder, multiplexer and demultiplexer. Some of the characteristics of combinational circuits are following —

- The output of combinational circuit at any instant of time, depends only on the levels present at input terminals.

- The combinational circuit do not use any memory. The previous state of input does not have any effect on the present state of the circuit.

- A combinational circuit can have an n number of inputs and m number of outputs.

### Block diagram

b.

c.

| (b) Fo  | r prime implicates don't care cells as o cells?                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 8 CALDICAD = 11 CO. 2, 3, 4,3,8,10,12,13)                                                                                                              |

|         | $f(a,b,c,d) = \overline{m_0, m_2, m_3, m_4, m_5, m_p, m_{10}, m_{12}, m_{15}} = \overline{m_0 + m_2 + m_3 + m_4 + m_5 + m_p + m_{10} + m_{12} + m_5} $ |

| <u></u> | € €a,b,c,d) = 5,m (0,2,2,4,5,8,10,12,12)                                                                                                               |

| Cor     | Ut. of amc table in 1/2 notation                                                                                                                       |

| 0       | a b c d o o o o o Const of steps to 2                                                                                                                  |

| 13      | ab cd 10010 2 All frather steps 02                                                                                                                     |

| \$31,3  | ne imp. of that prime implicates of the co2                                                                                                            |

|         | 5d 5d 5+d 5+c =(2                                                                                                                                      |

## 3a.

| S.NO. | ENCODER                                                                                           | DECODER                                                                                           |

|-------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 1.    | The combinational circuits that modify the binary data into N output lines are known as Encoders. | The combinational circuits that convert the binary data into 2N output lines are called Decoders. |

| 2.    | In this the output lines are n.                                                                   | In this the output lines are 2n.                                                                  |

| 3.    | The implemented signal is considered as actual signal input.                                      | It receives coded binary data as its input.                                                       |

| 4.    | It is utilized in videos, E-mail, and more.                                                       | It is mostly utilized in memory chips, microprocessors, and more.                                 |

| 5.    | When it comes to the communication mode, the encoder is situated at the transmitting end.         | Here, the decoder is situated at the receiving side.                                              |

| 6.    | The operating procedure is quite simple here.                                                     | The operating procedure is complex.                                                               |

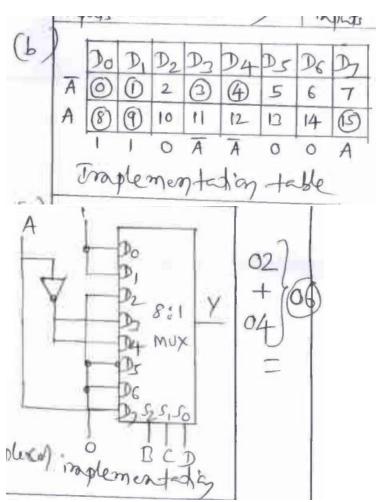

b.

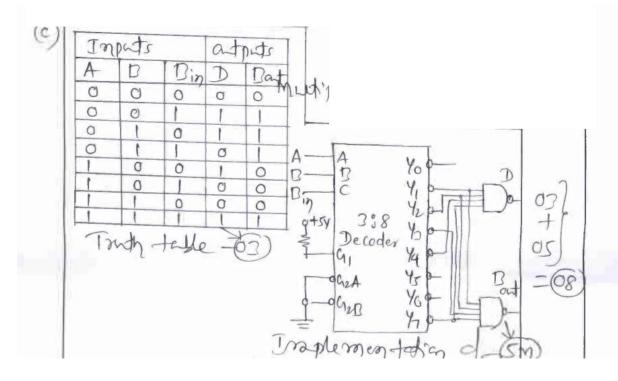

c.

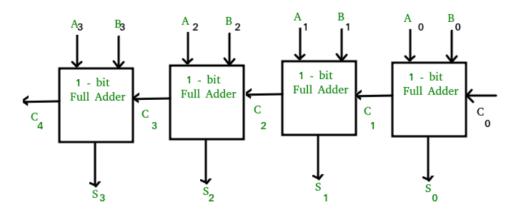

#### 4a.

In ripple carry adders, for each adder block, the two bits that are to be added are available instantly. However, each adder block waits for the carry to arrive from its previous block. So, it is not possible to generate the sum and carry of any block until the input carry is known. The  $i^{th}$  block waits for the  $i-1^{th}$  block to produce its carry. So there will be a considerable time delay which is carry propagation delay.

Consider the full adder circuit shown above with corresponding truth table. We define two variables as 'carry generate'  $G_i$  and 'carry propagate'  $P_i$  then,

$$P_i = A_i \oplus B_i$$

$$G_i = A_i B_i$$

The sum output and carry output can be expressed in terms of carry generate  $G_i$  and carry propagate  $P_i$  as

$$S_i = P_i \oplus C_i$$

$$C_{i+1} = G_i + P_i C_i$$

where  $G_i$  produces the carry when both  $A_i$ ,  $B_i$  are 1 regardless of the input carry.  $P_i$  is associated with the propagation of carry from  $C_i$  to  $C_{i+1}$ .

The carry output Boolean function of each stage in a 4 stage carry look-ahead adder can be expressed as

$$\begin{split} C_1 &= G_0 + P_0 C_{in} \\ C_2 &= G_1 + P_1 C_1 = G_1 + P_1 G_0 + P_1 P_0 C_{in} \\ C_3 &= G_2 + P_2 C_2 = G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 C_{in} \\ C_4 &= G_3 + P_3 C_3 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 P_1 G_0 + P_3 P_2 P_1 P_0 C_{in} \end{split}$$

4(b) 1. solading to ant pats

$$(A=B)=\xi_1(0,5,10,15)$$

$(A>B)=\xi_1(1,2,3,6,9,11)$  04

$(A 06

2 K-maps ---->06

3 Resultage Emadiag

$(A=B)=a'a'_0b'_1b'_0+a'_1a'_0b'_1b'_0$

$(A>B)=a'a'_0b'_1b'_0+a'_1a'_0b'_0b'_0$

$(A>B)=a_1b'_1+a_0b'_1b'_0+a_1a_0b'_0$

$(A$$

Module 3

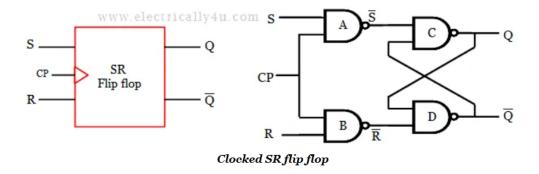

**5a.** A flip-flop is a device which stores a single bit (binary digit) of data; one of its two states represents a "one" and the other represents a "zero". Such data storage can be used for storage of state, and such a circuit is described as sequential logic in electronics. SR flip flop, also known as SR latch is the basic and simplest type of flip flop. It is a single bit storage element. It has only two logic gates. The output of each gate is connected to the input of another gate.

The state of the SR flip flop is determined by the condition of the output Q. If its value is 1, then the state is said to be SET and if Q = o, the state is said to be RESET. Hence it is called SR flip flop.

The Clocked SR flip-flop consists of 4 NAND gates, two inputs(S and R) and two outputs(Q and Q'). The clock pulse is given at the inputs of gate A and B.

If the clock pulse input is replaced by an enable input, then it is said to be SR latch. Let us assume that this flip flop works under <u>positive edge triggering</u>. The following figure shows the block diagram and the logic circuit of a clocked SR flip flop.

For interfacing keys to the digital systems, push bottom keys are used. Such push button key when pressed bounces a few seconds and then after few times it comes back to its initial position automatically during stable state. But before coming in to stable state if we take output then such output may be faulty. This problem is known as key debounce. It is undesirable and must be avoided.

Fig 7.3 Key bouncing switch.

One way to avoid key debounce problem is to use S-R latch. The circuit where S-R latch is used to avoid key bounce is called a switch debouncer.

**b.** The Master-Slave Flip-Flop is basically a combination of two JK flip-flops connected together in a series configuration. Out of these, one acts as the "**master**" and the other as a "**slave**". The output from the master flip flop is connected to the two inputs of the slave flip flop whose output is fed back to inputs of the master flip flop.

In addition to these two flip-flops, the circuit also includes an **inverter**. The inverter is connected to clock pulse in such a way that the inverted clock pulse is given to the slave flip-flop. In other words if CP=0 for a master flip-flop, then CP=1 for a slave flip-flop and if CP=1 for master flip flop then it becomes 0 for slave flip flop.

|                                                                                        | 1-(10) |

|----------------------------------------------------------------------------------------|--------|

| 8 (a) In Johnson counter, the a adjust of earling of flip-flop is connected to the Dia | els    |

| stage of thip-top is connected to the Dia                                              | n't    |

| of the next stage.                                                                     |        |

| DIAGRAM, + nuth table, Explanation                                                     | 12+2   |

| tironag diapram                                                                        | 2 3+3  |

|                                                                                        | -      |

| (b) Flip-for required 27>N, N=5, n=                                                    | 3      |

| (1) Excitedian table to JK (2) transits                                                | ian    |

| (1) Excitedian table for JK, (2) transitististe (3) K-map (4) Lopic-diagram            | =2×5   |

| (5) tirañas diagram                                                                    | =10    |

|                                                                                        |        |

(5) (1) Read any & Reed Linte memories (2) Flash 2+3+2707