| USN |  |  |  |  |  |  |  |  |  |

|-----|--|--|--|--|--|--|--|--|--|

|-----|--|--|--|--|--|--|--|--|--|

## Internal Assessment Test 1 – May 2022

|                                                                       | ystems                                                                                                      |                                                                                                                                                           | Sub Code:                                                                                                                                                                                                                                                      | 18EC62                                                                                                                                                                                                                                                                                                                                    | Branch:                                                                                                                                                                                                                                                                                                                                                          | EC                                                                                                                                                                                                                                                                                                                                                                                                                                                    | E                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ate: 06-05-2022 Duration: 90 Minutes Max Marks: 50 Sem / Sec: 6/A,B,C |                                                                                                             |                                                                                                                                                           |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                       | Ans                                                                                                         | wer any FIVE                                                                                                                                              | FULL Questions                                                                                                                                                                                                                                                 | <u>s</u>                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MARKS                                                                                                                                                                                                                                                                                                                                                                                                                                                    | СО                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

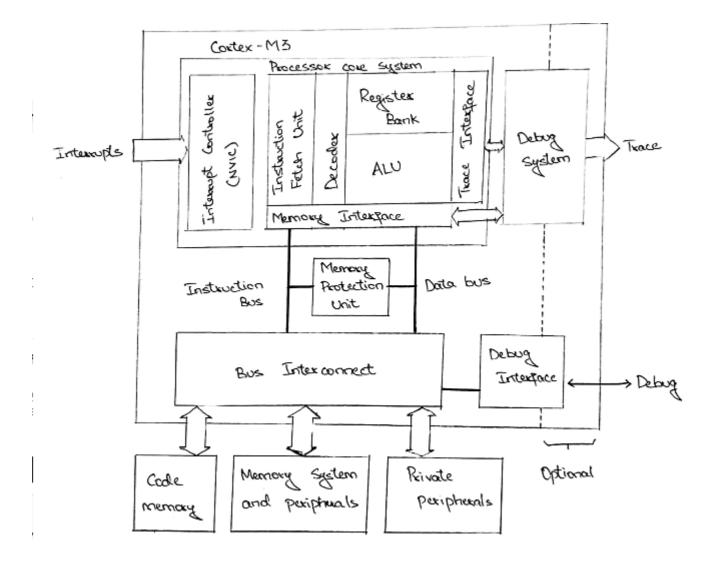

| With a neat                                                           | diagram,                                                                                                    | explain t                                                                                                                                                 | he architectu                                                                                                                                                                                                                                                  | ire (                                                                                                                                                                                                                                                                                                                                     | of ARM                                                                                                                                                                                                                                                                                                                                                           | Cortex M3                                                                                                                                                                                                                                                                                                                                                                                                                                             | [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Microcontrolle                                                        | er.                                                                                                         |                                                                                                                                                           |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -                                                                     | tack opera                                                                                                  | ations using                                                                                                                                              | PUSH and                                                                                                                                                                                                                                                       | POP                                                                                                                                                                                                                                                                                                                                       | instruction                                                                                                                                                                                                                                                                                                                                                      | ns in ARM                                                                                                                                                                                                                                                                                                                                                                                                                                             | [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Cortex M3.                                                            |                                                                                                             |                                                                                                                                                           |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Explain the ap                                                        | plications                                                                                                  | of Cortex M                                                                                                                                               | <b>I3.</b>                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                       | iagram, ex                                                                                                  | plain operat                                                                                                                                              | ion modes an                                                                                                                                                                                                                                                   | d pri                                                                                                                                                                                                                                                                                                                                     | vilege leve                                                                                                                                                                                                                                                                                                                                                      | ls in Cortex                                                                                                                                                                                                                                                                                                                                                                                                                                          | [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| M3.                                                                   |                                                                                                             |                                                                                                                                                           |                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Explain ARM                                                           | Cortex-M                                                                                                    | 3 Program S                                                                                                                                               | tatus Register                                                                                                                                                                                                                                                 | r in d                                                                                                                                                                                                                                                                                                                                    | etail.                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                       | functions                                                                                                   | of exceptio                                                                                                                                               | ns with a ve                                                                                                                                                                                                                                                   | ctor                                                                                                                                                                                                                                                                                                                                      | table and 1                                                                                                                                                                                                                                                                                                                                                      | priorities in                                                                                                                                                                                                                                                                                                                                                                                                                                         | [10]                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CO1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | L2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                       | With a neat Microcontrolle Explain the second M3. Explain the appearance with a neat decord M3. Explain ARM | Answith a neat diagram, Microcontroller. Explain the stack operations. Explain the applications. With a neat diagram, explain ARM Cortex-Microcontroller. | Answer any FIVE With a neat diagram, explain t Microcontroller. Explain the stack operations using Cortex M3. Explain the applications of Cortex M With a neat diagram, explain operat M3. Explain ARM Cortex-M3 Program S Describe the functions of exception | Answer any FIVE FULL Question With a neat diagram, explain the architectu Microcontroller. Explain the stack operations using PUSH and Cortex M3. Explain the applications of Cortex M3. With a neat diagram, explain operation modes an M3. Explain ARM Cortex-M3 Program Status Register Describe the functions of exceptions with a ve | Answer any FIVE FULL Questions With a neat diagram, explain the architecture of Microcontroller. Explain the stack operations using PUSH and POP Cortex M3. Explain the applications of Cortex M3. With a neat diagram, explain operation modes and prim M3. Explain ARM Cortex-M3 Program Status Register in describe the functions of exceptions with a vector | Answer any FIVE FULL Questions  With a neat diagram, explain the architecture of ARM Microcontroller.  Explain the stack operations using PUSH and POP instruction Cortex M3.  Explain the applications of Cortex M3.  With a neat diagram, explain operation modes and privilege lever M3.  Explain ARM Cortex-M3 Program Status Register in detail.  Describe the functions of exceptions with a vector table and privilege and privilege lever M3. | Answer any FIVE FULL Questions With a neat diagram, explain the architecture of ARM Cortex M3 Microcontroller. Explain the stack operations using PUSH and POP instructions in ARM Cortex M3. Explain the applications of Cortex M3. With a neat diagram, explain operation modes and privilege levels in Cortex M3. Explain ARM Cortex-M3 Program Status Register in detail. Describe the functions of exceptions with a vector table and priorities in | Answer any FIVE FULL Questions  With a neat diagram, explain the architecture of ARM Cortex M3  Microcontroller.  Explain the stack operations using PUSH and POP instructions in ARM  Cortex M3.  Explain the applications of Cortex M3.  [10]  With a neat diagram, explain operation modes and privilege levels in Cortex M3.  Explain ARM Cortex-M3 Program Status Register in detail.  [10]  Describe the functions of exceptions with a vector table and priorities in [10] | Answer any FIVE FULL Questions  With a neat diagram, explain the architecture of ARM Cortex M3 [10] CO1  Microcontroller.  Explain the stack operations using PUSH and POP instructions in ARM [10] CO1  Cortex M3.  Explain the applications of Cortex M3.  With a neat diagram, explain operation modes and privilege levels in Cortex [10] CO1  M3.  Explain ARM Cortex-M3 Program Status Register in detail.  Describe the functions of exceptions with a vector table and priorities in [10] CO1 |

| USN |  |  |  |  |  |  |  |  |  |  |

|-----|--|--|--|--|--|--|--|--|--|--|

|-----|--|--|--|--|--|--|--|--|--|--|

## $Internal\ Assessment\ Test\ 1-May\ 2022$

| Sub:  | Embedded Sy                                                           | stems      |              |                                |        | Sub Code:     | 18EC62        | Branch:    | EC        | Е         |

|-------|-----------------------------------------------------------------------|------------|--------------|--------------------------------|--------|---------------|---------------|------------|-----------|-----------|

| Date: | tte: 06-05-2022 Duration: 90 Minutes Max Marks: 50 Sem / Sec: 6/A,B,C |            |              |                                |        |               |               |            |           | OBE       |

| 1     | With a neat                                                           | diagram,   | •            | FULL Question<br>he architectu |        | of ARM        | Cortex M3     | MARKS [10] | CO<br>CO1 | RBT<br>L1 |

| 2     | Microcontrolle: Explain the st Cortex M3.                             |            | ntions using | PUSH and                       | POP    | ' instruction | ns in ARM     | [10]       | CO1       | L2        |

| 3     | Explain the app                                                       | olications | of Cortex M  | I3.                            |        |               |               | [10]       | CO1       | L2        |

| 4     | With a neat dia M3.                                                   | agram, ex  | plain operat | ion modes an                   | d pri  | ivilege leve  | ls in Cortex  | [10]       | CO1       | L2        |

| 5     | Explain ARM                                                           | Cortex-M   | 3 Program S  | Status Register                | r in d | etail.        |               | [10]       | CO1       | L2        |

| 6     | Describe the f cortex m3                                              | unctions   | of exceptio  | ns with a ve                   | ctor   | table and     | priorities in | [10]       | CO1       | L2        |

1. With a neat diagram, explain the architecture of ARM Cortex M3 Microcontroller.

The Costex-M3 is a 32-bit microprocessor. It has a 32-bit data path, a 32-bit register bank, and 32-bit memory interfaces. The processor has a Harvard architecture, which means that it has a separate instruction bus and data bus. This allows instructions and data accesses to take place at the same time, and as a result of this, the performance of the processor increases because data accesses do not affect the instruction pipeline. This feature results in multiple bus interfaces on Cotex-M3, each with optimized usage and the ability to be used simultaneously.

For complex applications that require more memory system poilure features, the Coxlex-M3 processor, has an optional Memory Rotection Unit (MPU), and it is possible to use an external cache if it's required. Both little endian and big endian memory systems are supported.

The Cortex-M3 processor includes a number of fixed internal debugging components. These components provide debugging operation supports and features, such as breakpoints and watchpoints. In addition, optional components provide debugging features, such as instruction trace, and various types of debugging interfaces.

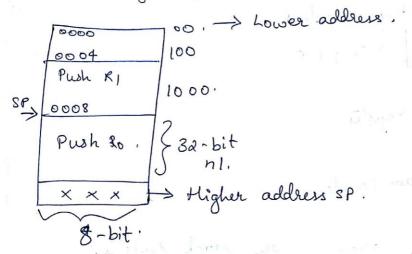

2. Explain the stack operations using PUSH and POP instructions in ARM Cortex M3.

22. Explain stack memory operations on Cortex M3 processor with necessary diagrams.

Push : Decrements 3P by 4.

POP: Increments SP by 4.

Push {RO}; RI3=R13-4, then memory [RI3]=RO POP {RO}; RO = memory [RI3], then RI3=RI3+4

Multiple registers can be pushed & poped in

Eg: push. { Ro, Ri} Push { Ro- R7, R12, R83

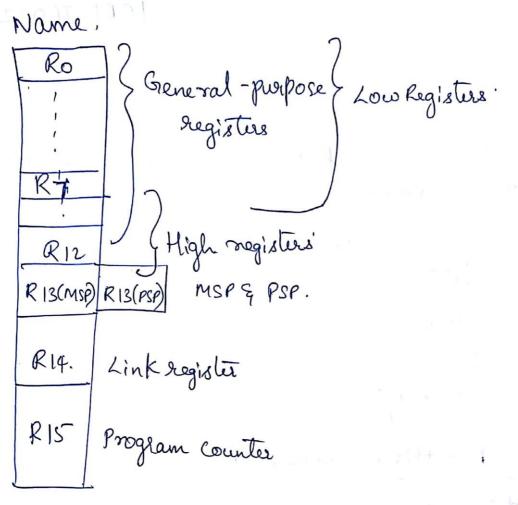

Coolex #13 con tains & Stack pointers (R13), They are banked so that only one is visible at a time.

\*\*Main Stack pointer (MSP): The default stack pointer

\*\*Process Stack pointer (PSP) - Used by user applicate code.

stack register. showing the

Lad Janguary CA

Mushipe " exclusion ou he present a property

inst itc- 6ty 612, 82

can HE Conjuly & want you they (RE)

banked so that mayour holdes at a true

|      |         | 730                                                                                                                                                                                                              |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |         | Sena Jacob<br>1CRISTEONA                                                                                                                                                                                         |

|      |         |                                                                                                                                                                                                                  |

| V    | 10<br>→ | List and explain the application of cortex<br>M3 processon.                                                                                                                                                      |

|      | (a)     | LONE- cost micro-controlle:                                                                                                                                                                                      |

| 1    |         | consumer products quem dags to elitrical appliances.                                                                                                                                                             |

|      |         | At is highly competitive market du to<br>the many well known 8-bit & 16-bit<br>microconholles products on the market-                                                                                            |

|      | 4       | Automolive:  H has very high putormance efficiency l  love interrupt latency allowing it to be  used in real-time system in the automotive  industry.                                                            |

| · KK | 49      | At supports AO external vectored interests reigh a built-in interrupt controller with risted interrupt supports I an optical Mpu makiting it ideal for highly integrated I cost-susiline automotive application. |

|      | (c)     | Dala communication:  H's love pover & high efficiency features  coupled with thumb-is instructions for  bit filld manipulation make the  cortex M3 ideal for many communication  application.                    |

|      | (al)    | Andus/vial control: The processor's interrupts fro features                                                                                                                                                      |

love latericy e enhanced Fault- Jinding. Jeatures make éta virrong cardicale (e) Consumu products;

4 CORTEX-M3, being a small procusor,

is Lighly efficient & low in power a

supply support a MPU enabling complex softwar to execute while

providing ubust memory protection.

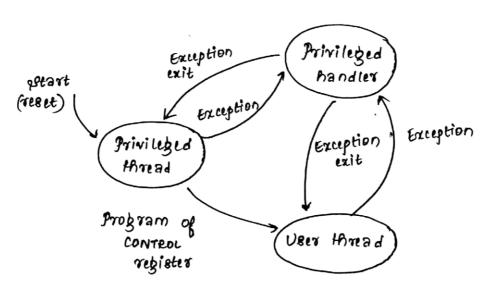

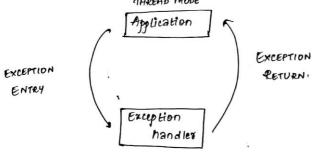

- 4. With a neat diagram, explain operation modes and privilege levels in Cortex M3.

- (15) Kist & Explain various operating modes of lortex M3 processor.

Two types of operating modes:

- (a) Thread mode.

- (b) Handler mode.

The privilege kevels provide a mechanism for safeguarding memory access to critical regions as well as providing a basic security model.

- (a) Thread mode: Used to execute application software.

The processor enters Thread mode when it comes out of reset:

- (b) Handler mode: Used to handle exceptions.

is running a normal program or running an exception handler like an interrupt handler or system exception handler.

+ control register bits directs modes & kevels.

⇒Privileged kerel & user level provide a mechanism for safeguarding memory accesses to critical regions as well as providing a basic security model.

## The privilege kevels:

- (1) unprivileged: The software,

- Has kimited access to control register (MSR & MRS) instructions, and cannot use the co-processor (CPS) instruction.

- · cannot access the s/m timer, NVIC or system control block.

- . Might have restricted access to memory or peripherals.

- Unprivileged software can use the exceptions (svc) instruction to make a supervisor call to transfer control to privileged software.

- E has access to all resources.

- . Only privileged software can write to control register.

- · In Handler mode, software execution is always privileged.

## 5. Explain ARM Cortex-M3 Program Status Register in detail.

14. Explain structure of CPSR

Gowtham A. 1 CRISTEDIS

A: The PSR are subdivided into 3:

12 APSR 2) IPSR 3) EPSR

They can be accessed together or seperately using special oregister MSR and MRS. When accounted as a collective item xPSR is used.

MO, APSR nead flag state into RO MRS rusuite flag state. APSR, STO MCR

|       | 31 | 30 | 29 | 58 | 27 | 26:25  | 24 | 23:20 | 19:16 | 15:10 | 2 | 9 167         |

|-------|----|----|----|----|----|--------|----|-------|-------|-------|---|---------------|

| A PSR | N  | Z  | c  | V  | a  |        |    |       |       |       |   | Fauntien num. |

| IPSR  |    |    |    |    |    |        |    |       |       |       |   | , viring      |

| F293  |    |    | 0  |    |    | ICY IT | +  |       | 1     | k1/iT |   |               |

Desouiption Rit Negative EUD Z Carry/borr w C overflow Sticky Saturato flag 0 Interrupt-landouvable Instruction, IF-Then instruction status hit 101/17 Thumb stat

which exception the processor is handling Enception num.

xPSR is orequired, assembler, when arrassing Boun nead commined program status word no, PSR MRS unite combined status word. MSR PSR , ND

Explain interrupts and exceptions in Cortex M3 processor.

Exceptions

Exceptions are numbered 1 do 15 for system exceptions and the next 240 for external interrupt inputs (Total 256 entries in vector table)

Most of the exceptions have programmable priosity, and a few have fixed priosity.

The value of the current running exception is endicated by the special register IPSR or from the NVIC'S Interrupt Control state Register.

| 1                   |                    |              | <i>'</i>                                                                                      |

|---------------------|--------------------|--------------|-----------------------------------------------------------------------------------------------|

| Exception<br>Number |                    | Paloaity     | Description                                                                                   |

| 1.                  | Reset              | -3(Highest   | Reset                                                                                         |

| 2                   | EMI                | -2           | Nonmaskable interrupt<br>(external NME (1p)                                                   |

| 3                   | Hardfault          | -1           | All fault condition, if<br>the corresponding fault                                            |

| н.                  | MenMarage<br>fault | Programmable | handler is not enabled.  Memory management fault, MPU violation.  access to illegal locations |

| 5·                  | Busfault           | Programmable | Bus error like Brefitch                                                                       |

| 6 -                 | Wage fault         |              | a 60 a 6                                                                                      |

|                     |                    |              | access coprocessor.                                                                           |

|     | 1               |                          |               |                                                                   |

|-----|-----------------|--------------------------|---------------|-------------------------------------------------------------------|

|     | 7-10            | Reserved                 | NA            | _                                                                 |

|     | t)              | SVCall                   | Porogrammable | System Service call                                               |

|     | 12.             | Debug Monitor            | Programmable  | Debug Monitor.                                                    |

|     | 13              | Reserved                 | N11.0         |                                                                   |

|     | 14              |                          | Poragrammable | Systes Pendakle request                                           |

|     | ائ <sup>.</sup> | SYSTICK                  | Programmable  | System Pendakle request<br>for System device<br>System Tick Timer |

|     | 16.             | External<br>Interrupt #0 | Programmable  | External Interrupt                                                |

|     | 17.             | External<br>Interrupt #1 |               | External Interrupt                                                |

|     | ٠               | '                        |               | ~ ~ =                                                             |

|     | 256             | External Interry<br>#239 | Perogrammable | External Interrupt.                                               |

| - 1 |                 |                          |               |                                                                   |

Vector Table

The processor will need to locate the starting address of the exception handler when an exception is being landled. This information is stored in the rector table.

Exception Vector Table After Paver Up.

| 2,000      |           |                                              |

|------------|-----------|----------------------------------------------|

| Address    | Exception | Value (Word Size)                            |

| 1,7000     | Number    |                                              |

| 000000000  | -         | MSPInitial Value                             |

| 0x00000004 | 1         | Resetvector (Pro gram counter initial value) |

| 800000000  | 2         | NMI landler starting address                 |

| 0000000 c  | 3         | Hard fault hardler starting address          |

|            |           | other handler starting address               |

|            |           |                                              |

For example, if the next is exception type 1, the address, of the next vector is I times [4] leach word is 4 bytes), which equals 0x00000004, and NM2 vector (type 2) is located in 2x4 = 0x00000008. The address ox000000000 is used to store the starting value for the MSP.