## **Internal Assessment Test1–December 2022**

(Schemes and Solutions)

Sub Code: 21CS34

| Sub:  |                                                                                                                                                                             | rganization and Archi                              | tecture              | Sub Code:     | 21CS34            | Branc | ch: ISE |     |     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------|---------------|-------------------|-------|---------|-----|-----|

| Date: | 03/12/2022                                                                                                                                                                  | Duration: 90min's                                  | Max Marks: 50        | Sem /Sec:     | IIIA, B &C        |       | MARKS   |     | BE  |

|       | Answer any FIVE FULL Questions  Write a note on byte addressability, big endian and little endian Assignments                                                               |                                                    |                      |               |                   |       |         | CO  | RBT |

| 1     |                                                                                                                                                                             |                                                    | ty, big endian and   | l little endi | an Assignme       | nts   | 4+3+3   | CO1 | L1  |

|       | with supporti                                                                                                                                                               | . 1 .                                              |                      |               |                   |       |         |     |     |

|       | Byte Addres                                                                                                                                                                 |                                                    |                      |               |                   |       |         |     |     |

|       | address space                                                                                                                                                               |                                                    |                      |               |                   |       |         |     |     |

|       | entities. The                                                                                                                                                               | abie                                               |                      |               |                   |       |         |     |     |

|       | entity.                                                                                                                                                                     |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       | 16-bit Word Addressable 128 KB<br>32-bit Word Addressable 256 KB                                                                                                            |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       | Big Endian                                                                                                                                                                  |                                                    |                      |               |                   |       |         |     |     |

|       | In this format,                                                                                                                                                             | ence.                                              |                      |               |                   |       |         |     |     |

|       | Because memor                                                                                                                                                               |                                                    |                      |               |                   |       |         |     |     |

|       | If a 32-bit work                                                                                                                                                            | n the                                              |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             | showing how it will be in                          | n the register).     |               |                   |       |         |     |     |

|       | Little Endian                                                                                                                                                               |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             | the LSB is stored at the e to how bytes were store |                      |               | er significant c  | ytes. |         |     |     |

|       | * *                                                                                                                                                                         | d has value 0x0A0B0C                               | · ·                  |               | red as below i    | n the |         |     |     |

|       |                                                                                                                                                                             | showing how it will be in                          |                      | a will be sto | ica as selow i    | n the |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      | nificant byte | is stored first ( | thus, |         |     |     |

|       | To remember which is which, recall whether the least significant byte is stored first (thus little endian) or the most significant byte is stored first (thus, big endian). |                                                    |                      |               |                   |       |         |     |     |

|       | Note that it is "                                                                                                                                                           |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       | TI TI TI 31 23 15 7 0                                                                                                                                                       |                                                    |                      |               |                   |       |         |     |     |

|       | The Big End                                                                                                                                                                 | 01 02                                              | 03 04                | The Li        | ttle End          |       |         |     |     |

|       | Byte 3 Byte 2 Byte 1 Byte 0                                                                                                                                                 |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

| 2a    | <b>Define Process</b>                                                                                                                                                       | sor clock, SPEC rating                             | and Basic perforn    | nance equati  | on of comput      | er.   | 2*3     | CO1 | L1  |

|       | Processor clock                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       | Processor circu                                                                                                                                                             | its are controlled by a                            | timing signal called | d clock. The  | clock designe     | r the |         |     |     |

|       | _                                                                                                                                                                           | tervals called clock cyc                           |                      |               | _                 |       |         |     |     |

|       |                                                                                                                                                                             | ion to be performed int                            | -                    | _             | _                 |       |         |     |     |

|       | completed in                                                                                                                                                                | one clock cycle. The                               | length P of one      | clock cycle   | e is an impo      | rtant |         |     |     |

|       | Basic performance Equation                                                                                                                                                  |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       | $T = \frac{N 	imes S}{R}$                                                                                                                                                   |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       | Spec Rating                                                                                                                                                                 |                                                    |                      |               |                   |       |         |     |     |

|       | Spec Rating                                                                                                                                                                 |                                                    |                      |               |                   |       |         |     |     |

|       | SPEC rating = Running time on the reference computer                                                                                                                        |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             | Running time on the computer under test            |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

|       |                                                                                                                                                                             |                                                    |                      |               |                   |       |         |     |     |

| •     | •                                                                                                                                                                           |                                                    |                      |               |                   |       |         |     |     |

| 2b | Explain Subrouti                                                                                                                                                                                          | 4                                                                           | CO1                                                                                                         | L2                            |     |    |  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------|-----|----|--|

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

|    | Subroutine  A subroutine performs a function required by the program from which it is called  The interrupt-Service round not have anything in compart the program being executing the interrupt received |                                                                             |                                                                                                             |                               |     |    |  |

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

| 3  | clock cycles.40%                                                                                                                                                                                          | instructions require 3 clock<br>ecution. Find the total time                | f that 25% instruction requires 5<br>k cycles and remaining requires 4<br>e required to execute the program | 5+5<br>(procedure<br>and sol) | CO1 | L3 |  |

| 4  | What is an addre                                                                                                                                                                                          | 2*5                                                                         | CO1                                                                                                         | L2                            |     |    |  |

|    | example and supp                                                                                                                                                                                          | example and supportive diagrams.                                            |                                                                                                             |                               |     |    |  |

|    | Table 2.1 Generic a                                                                                                                                                                                       |                                                                             |                                                                                                             |                               |     |    |  |

|    | Name                                                                                                                                                                                                      | Assembler syntax                                                            | Addressing function                                                                                         |                               |     |    |  |

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

|    | Immediate                                                                                                                                                                                                 | # Value                                                                     | Operand = Value                                                                                             |                               |     |    |  |

|    | Register<br>Absolute (Direct)                                                                                                                                                                             | Ri<br>LOC                                                                   | EA = Ri<br>EA = LOC                                                                                         |                               |     |    |  |

|    | Indirect                                                                                                                                                                                                  | (Ri)                                                                        | EA = LOC<br>EA = [Ri]                                                                                       |                               |     |    |  |

|    | manect                                                                                                                                                                                                    | (LOC)                                                                       | EA = [KI]<br>EA = [LOC]                                                                                     |                               |     |    |  |

|    | Index                                                                                                                                                                                                     | X(Ri)                                                                       | EA = [Ri] + X                                                                                               |                               |     |    |  |

|    | Base with index                                                                                                                                                                                           | (Ri, Rj)                                                                    | EA = [Ri] + [Rj]                                                                                            |                               |     |    |  |

|    | Base with index                                                                                                                                                                                           | X (Ri, Rj)                                                                  | EA = [Ri] + [Rj] + X                                                                                        |                               |     |    |  |

|    | and offset                                                                                                                                                                                                |                                                                             |                                                                                                             |                               |     |    |  |

|    | Relative                                                                                                                                                                                                  | X(PC)                                                                       | EA = [PC] + X                                                                                               |                               |     |    |  |

|    | Autoincrement                                                                                                                                                                                             | (Ri)+<br>-(Ri)                                                              | EA = [Ri]; Increment Ri<br>Decrement Ri; EA = [Ri]                                                          |                               |     |    |  |

|    | Autodecrement                                                                                                                                                                                             |                                                                             |                                                                                                             |                               |     |    |  |

| 5  |                                                                                                                                                                                                           | Value = a signed number  Explain Interrupt Hardware in detail with diagram. |                                                                                                             |                               |     |    |  |

| 5  | Processor Processor                                                                                                                                                                                       | t Hardware in detail with t                                                 | nagram.<br>V <sub>dd</sub>                                                                                  | 5+5<br>(diagram<br>+theory)   | CO2 | L2 |  |

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

|    | INTR —                                                                                                                                                                                                    | INTR INTR                                                                   |                                                                                                             |                               |     |    |  |

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

|    | Figure 4.6 An equive interrupt-r                                                                                                                                                                          |                                                                             |                                                                                                             |                               |     |    |  |

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

|    | • Interrupt re                                                                                                                                                                                            |                                                                             |                                                                                                             |                               |     |    |  |

|    | <ul> <li>If several I</li> </ul>                                                                                                                                                                          |                                                                             |                                                                                                             |                               |     |    |  |

|    | <ul> <li>A single in</li> </ul>                                                                                                                                                                           |                                                                             |                                                                                                             |                               |     |    |  |

|    | When devi                                                                                                                                                                                                 |                                                                             |                                                                                                             |                               |     |    |  |

|    | is '0'                                                                                                                                                                                                    | -                                                                           | -                                                                                                           |                               |     |    |  |

|    | <ul> <li>INTR is lo</li> </ul>                                                                                                                                                                            | gic OR                                                                      |                                                                                                             |                               |     |    |  |

|    |                                                                                                                                                                                                           | • INTR=INTR1+INTR2++INTRn                                                   |                                                                                                             |                               |     |    |  |

|    | • INTR is ac                                                                                                                                                                                              |                                                                             |                                                                                                             |                               |     |    |  |

|    |                                                                                                                                                                                                           | -                                                                           |                                                                                                             |                               |     |    |  |

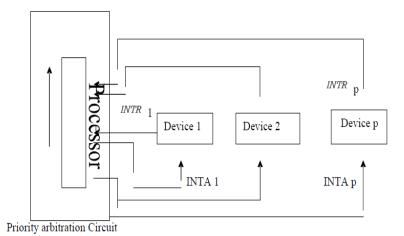

| 6  | Explain the follow                                                                                                                                                                                        | wing methods of handling in                                                 | nterrupt from multiple devices                                                                              | 10                            | CO2 | L2 |  |

|    |                                                                                                                                                                                                           | red interrupt ii) Interrupt pr                                              |                                                                                                             |                               |     |    |  |

|    | Vectored Interru                                                                                                                                                                                          | 1 ' 1 1                                                                     | -                                                                                                           |                               |     |    |  |

|    |                                                                                                                                                                                                           |                                                                             |                                                                                                             | 1                             | 1   |    |  |

- ✓ To reduce the time involved in the polling process, a device requesting an interrupt may identify itself directly to the processor. Then, the processor can immediately start executing the corresponding interrupt-service routine.

- ✓ A device requesting an interrupt can identify itself by sending a special code to the processor over the bus. This enables the processor to identify individual devices even if they share a single interrupt-request line.

- ✓ The code supplied by the device may represent the starting address of the interrupt-service routine for that device. The code length is typically in the range of 4 to 8 bits. The remainder of the address is supplied by the processor based on the area in its memory where the addresses for interrupt-service routines are located.

- ✓ This arrangement implies that the interrupt-service routine for a given device must always start at the same location. The programmer can gain some flexibility by storing in this location an instruction that causes a branch to the appropriate routine.

## **Interrupt Priority**

Figure 2: Implementation of interrupt priority using individual interrupt-request and acknowledge lines.