## Internal Assessment Test 2–December2022

# (Scheme & solution)

| e: 27/12/2022 Duration: 90min's MaxMarks: 50 Sem/Sec: IIIA, B &C OBE  Answer any FIVE FULL Questions  MARKS CO RB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ub:<br>ate:   | Computer Organization and Architecture SubCode: 21CS34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bran                             | 1                          | ICE |     |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------|-----|-----|----|

| Answer any FIVE FULL Questions  List out functions of the I/O interface.  1. Provides a storage buffer for at least one word of data (or one byte, in the case of byte-oriented devices)  2. Contains status flags that can be accessed by the processor to determine whether the buffer is full (for input) or empty (for output)  3. Contains address-decoding circuitry to determine when it is being addressed by the processor  4. Generates the appropriate timing signals required by the bus control scheme  5. Performs any format conversion that may be necessary to transfer data between the bus and the I/O device, such as parallel-serial conversion in the case of a serial port  Define Bus arbitration. Explain in detail any one approach of bus arbitration.  Processor and DMA controllers both need to initiate data transfers on the bus and access main fitton the device of the device that is allowed to initiate transfers on the bus at any given time is called the "Diagr bus master. When the current bus master relinquishes its status as the bus master, another device am+ can acquire this status. The process by which the next device to become the bus master is selected explan and bus mastership is transferred to it is called bus arbitration.  • 2 Approaches of Bus arbitration:  • A single bus arbiter performs the arbitration.  • Distributed arbitration:  • All devices participate in the selection of the next bus master.  Centralized Bus Arbitration  Processor    DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | te:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Diai                             | ncn:                       | DE  |     |    |

| List out functions of the I/O interface.  1. Provides a storage buffer for at least one word of data (or one byte, in the case of byte-oriented devices)  2. Contains status flags that can be accessed by the processor to determine whether the buffer is full (for input) or empty (for output)  3. Contains satuts flags that can be accessed by the processor to determine whether the buffer is full (for input) or empty (for output)  3. Contains address-decoding circuitry to determine when it is being addressed by the processor  4. Generates the appropriate timing signals required by the bus control scheme  5. Performs any format conversion that may be necessary to transfer data between the bus and the I/O device, such as parallel-serial conversion in the case of a serial port  Define Bus arbitration. Explain in detail any one approach of bus arbitration.  Processor and DMA controllers both need to initiate data transfers on the bus and access main (Definition Honor |               | 27/12/2022 Duration: 90min's MaxMarks: 50 Sem/Sec: IIIA, B &C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | C                                |                            |     | OBE | Ξ  |

| List out functions of the I/O interface.  1. Provides a storage buffer for at least one word of data (or one byte, in the case of byte-oriented devices)  2. Contains status flags that can be accessed by the processor to determine whether the buffer is full (for input) or empty (for output)  3. Contains address-decoding circuitry to determine when it is being addressed by the processor  4. Generates the appropriate timing signals required by the bus control scheme  5. Performs any format conversion that may be necessary to transfer data between the bus and the I/O device, such as parallel-serial conversion in the case of a serial port  Define Bus arbitration. Explain in detail any one approach of bus arbitration.  Processor and DMA controllers both need to initiate data transfers on the bus and access main memory. The device that is allowed to initiate transfers on the bus at any given time is called the +Diagr bus master. When the current bus master relinquishes its status as the bus master, another device am+can acquire this status. The process by which the next device to become the bus master is selected explan and bus mastership is transferred to it is called bus arbitration.  • 2 Approaches of Bus arbitration:  • A single bus arbitration:  • A single bus arbitration the selection of the next bus master.  Centralized Bus Arbitration  FESS   DMA  Controller  DMA  Controller  CO2 L  CO3 L  CO4  L  CO5 L  CO5 L  CO6 L  CO7 L  CO7 L  CO7 L  CO8 L  CO9 L  C |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ]                                | MARK                       | S   | CO  | RB |

| 1. Provides a storage buffer for at least one word of data (or one byte, in the case of byte-oriented devices)  2. Contains status flags that can be accessed by the processor to determine whether the buffer is full (for input) or empty (for output)  3. Contains address-decoding circuitry to determine when it is being addressed by the processor  4. Generates the appropriate timing signals required by the bus control scheme  5. Performs any format conversion that may be necessary to transfer data between the bus and the I/O device, such as parallel-serial conversion in the case of a serial port  Define Bus arbitration. Explain in detail any one approach of bus arbitration.  Processor and DMA controllers both need to initiate data transfers on the bus and access main tion the device that is allowed to initiate transfers on the bus at any given time is called the Holiagre am+ can acquire this status. The process by which the next device to become the bus master is selected explan and bus mastership is transferred to it is called bus arbitration.  • 2 Approaches of Bus arbitration:  • A single bus arbitration:  • A single bus arbiter performs the arbitration.  • Distributed arbitration:  • All devices participate in the selection of the next bus master.  Centralized Bus Arbitration  FESS   DMA Controller  DMA Controller  DMA Controller  DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | þ             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  | 4                          | (   | CO2 | L  |

| 3. Contains address-decoding circuitry to determine when it is being addressed by the processor  4. Generates the appropriate timing signals required by the bus control scheme  5. Performs any format conversion that may be necessary to transfer data between the bus and the I/O device, such as parallel-serial conversion in the case of a serial port  Define Bus arbitration. Explain in detail any one approach of bus arbitration.  Processor and DMA controllers both need to initiate data transfers on the bus and access main from the device that is allowed to initiate transfers on the bus at any given time is called the bus master. When the current bus master relinquishes its status as the bus master, another device can acquire this status. The process by which the next device to become the bus master is selected and bus mastership is transferred to it is called bus arbitration.  • 2 Approaches of Bus arbitration:  • A single bus arbiter performs the arbitration.  • Distributed arbitration:  • All devices participate in the selection of the next bus master.  Centralized Bus Arbitration   BBSY  DMA controller  DMA controller  DMA controller  DMA controller  DMA controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | <ol> <li>Provides a storage buffer for at least one word of data (or one byte, in the case of byte-oriented devices)</li> <li>Contains status flags that can be accessed by the processor to determine whether</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |                            |     |     |    |

| 5. Performs any format conversion that may be necessary to transfer data between the bus and the I/O device, such as parallel-serial conversion in the case of a serial port  Define Bus arbitration. Explain in detail any one approach of bus arbitration.  Processor and DMA controllers both need to initiate data transfers on the bus and access main tion memory. The device that is allowed to initiate transfers on the bus at any given time is called the bus master. When the current bus master relinquishes its status as the bus master, another device am+ can acquire this status. The process by which the next device to become the bus master is selected explan and bus mastership is transferred to it is called bus arbitration.  • 2 Approaches of Bus arbitration:  • A single bus arbitration:  • A single bus arbitration:  • All devices participate in the selection of the next bus master.  Centralized Bus Arbitration   BBSV  DMA controller  DMA controller  DMA controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 3. Contains address-decoding circuitry to determine when it is being addressed by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                            |     |     |    |

| Define Bus arbitration. Explain in detail any one approach of bus arbitration.  Processor and DMA controllers both need to initiate data transfers on the bus and access main (Definition House master). The device that is allowed to initiate transfers on the bus at any given time is called the bus master. When the current bus master relinquishes its status as the bus master, another device am+ explan and bus mastership is transferred to it is called bus arbitration.  • 2 Approaches of Bus arbitration:  • A single bus arbiter performs the arbitration.  • All devices participate in the selection of the next bus master.  Centralized Bus Arbitration   BBSY  Processor  DMA controller  DMA controller  DMA controller  DMA controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | <ol> <li>Generates the appropriate timing signals required by the bus control scheme</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |                            |     |     |    |

| Processor and DMA controllers both need to initiate data transfers on the bus and access main memory. The device that is allowed to initiate transfers on the bus at any given time is called the bus master. When the current bus master relinquishes its status as the bus master, another device an acquire this status. The process by which the next device to become the bus master is selected explan and bus mastership is transferred to it is called bus arbitration.  • 2 Approaches of Bus arbitration  • A single bus arbitration:  • A single bus arbitrer performs the arbitration.  • Distributed arbitration:  • All devices participate in the selection of the next bus master.  Centralized Bus Arbitration  BBSY  DMA Controller  DMA Controller  DMA Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |                            |     |     |    |

| Processor  DMA controller controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I<br>l        | memory. The device that is allowed to initiate transfers on the bus at any given time is ca bus master. When the current bus master relinquishes its status as the bus master, another can acquire this status. The process by which the next device to become the bus master is s and bus mastership is transferred to it is called <a href="mailto:bus arbitration">bus arbitration</a> .  • 2 Approaches of Bus arbitration:  • A single bus arbiter performs the arbitration.  • Distributed arbitration:                                                                                                                                                                                                      | lled the +1 device arselected ex | on<br>Diagr<br>n+<br>xplan |     |     |    |

| Processor  DMA controller controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |                            |     |     |    |

| DMA DMA controller controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9             | Centralized Bus Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |                            |     |     |    |

| controller controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>•</u>      | Centralized Bus Arbitration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  |                            |     |     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>(</u>      | Centralized Bus Arbitration  BBSY  BR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                  |                            |     |     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>(</u>      | Centralized Bus Arbitration  BBSY  BR  DMA  DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                  |                            |     |     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | Centralized Bus Arbitration  BBSY  BR  Processor  DMA controller 1 BG2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                  |                            |     |     |    |

| Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | נ             | Centralized Bus Arbitration  BBSY  BR  DMA controller 1 Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                  |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | j             | Centralized Bus Arbitration  BBSY  BR  DMA controller 1  Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prise the bus master, unless it grants bus membership to one of the DMA controllers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . DMA                            |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ]<br>i        | Centralized Bus Arbitration  BBSY  BR  DMA controller 1  Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prise the bus master, unless it grants bus membership to one of the DMA controllers. controller requests the control of the bus by asserting the Bus Request (BR) line. In response                                                                                                                                                                                                                                                                                                                                                                                | DMA                              |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use the bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ]<br>ii<br>K  | Centralized Bus Arbitration  BBSY  BR  DMA controller 1  Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prise the bus master, unless it grants bus membership to one of the DMA controllers. controller requests the control of the bus by asserting the Bus Request (BR) line. In responsible processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use                                                                                                                                                                                                                                                                                       | DMA nse, the the bus             |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use the bus when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. BBSY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ]]<br>ii<br>C | Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the pris the bus master, unless it grants bus membership to one of the DMA controllers. controller requests the control of the bus by asserting the Bus Request (BR) line. In responsible processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion.                                                                                                                                                                                                                                                       | DMA nse, the the bus             |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use the bus when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. BBSY signal is 0, it indicates that the bus is busy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ]<br>i<br>R   | Centralized Bus Arbitration  BBSY  BR  DMA controller 1  Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prise the bus master, unless it grants bus membership to one of the DMA controllers. controller requests the control of the bus by asserting the Bus Request (BR) line. In responsive processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. signal is 0, it indicates that the bus is busy.                                                                                                                                              | DMA nse, the the bus BBSY        |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use the bus when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. BBSY signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ]<br>ii<br>C  | Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prise the bus master, unless it grants bus membership to one of the DMA controller controller requests the control of the bus by asserting the Bus Request (BR) line. In responsive processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the                                                                                                                   | DMA nse, the the bus BBSY        |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use the bus when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. BBSY signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ]<br>ii<br>C  | Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prise the bus master, unless it grants bus membership to one of the DMA controllers. controller requests the control of the bus by asserting the Bus Request (BR) line. In responsary processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the DMA controller 2 asserts the BR signal.                                                                         | DMA nse, the the bus BBSY        |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use the bus when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. BBSY signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | j<br>i<br>I   | Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prise the bus master, unless it grants bus membership to one of the DMA controllers. controller requests the control of the bus by asserting the Bus Request (BR) line. In responsary processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the processor asserts the BR signal.                                                                                | DMA nse, the the bus BBSY        |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use the bus when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. BBSY signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the bus.  DMA controller 2 asserts the BR signal.  Processor asserts the BG1 signal BG1 signal propagates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | j<br>i<br>I   | Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prise the bus master, unless it grants bus membership to one of the DMA controllers. controller requests the control of the bus by asserting the Bus Request (BR) line. In responsive processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the bus asserts the BR signal.  Processor asserts the BG1 signal propagates                                         | DMA nse, the the bus BBSY e bus. |                            |     |     |    |

| is the bus master, unless it grants bus membership to one of the DMA controllers. DMA controller requests the control of the bus by asserting the Bus Request (BR) line. In response, the processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use the bus when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. BBSY signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the bus.  DMA controller 2 asserts the BR signal.  Processor asserts the BG1 signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | Bus arbiter may be the processor or a separate unit connected to the bus.Normally, the prist the bus master, unless it grants bus membership to one of the DMA controllers. controller requests the control of the bus by asserting the Bus Request (BR) line. In responsive processor activates the Bus-Grant1 (BG1) line, indicating that the controller may use when it is free. BG1 signal is connected to all DMA controllers in a daisy chain fashion. signal is 0, it indicates that the bus is busy.  When BBSY becomes 1, the DMA controller which asserted BR can acquire control of the BR signal.  Processor asserts the BR signal.  Processor asserts the BR signal.  BG1 signal propagates to DMA#2. | DMA nse, the the bus BBSY e bus. |                            |     |     |    |

Processor relinquishes control of the bus by setting BBSY to 1.

OR

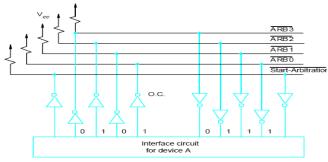

### Distributed arbitration

All devices waiting to use the bus share the responsibility of carrying out the arbitration process. Arbitration process does not depend on a central arbiter and hence distributed arbitration has higher reliability. Each device is assigned a 4-bit ID number.

All the devices are connected using 5 lines, 4 arbitration lines to transmit the ID, and one line for the Start- Arbitration signal. To request the bus a device: Asserts the Start-Arbitration signal Places its 4-bit ID number on the arbitration lines. The pattern that appears on the arbitration lines is the logical-OR of all the 4-bit device IDs placed on the

arbitration lines.

#### Arbitration process:

Each device compares the pattern that appears on the arbitration lines to its own ID, starting with MSB. If it detects a difference, it transmits 0s on the arbitration lines for that and all lower bit positions. The pattern that appears on the arbitration lines is the logical-OR of all the 4-bit device IDs placed on the arbitration lines. Device A has the ID 5 and wants to request the bus. Transmits the pattern 0101 on the arbitration lines.

Device B has the ID 6 and wants to request the bus: - Transmits the pattern 0110 on the arbitration lines. Pattern that appears on the arbitration lines is the logical OR of the patterns Pattern 0111 appears on the arbitration lines.

#### Arbitration process:

Each device compares the pattern that appears on the arbitration lines to its own