| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

|     |  |  |  |  |  |

## Internal Assessment Test 2 – December 2022

## **Scheme and Solution**

| Sub:  | Computer Organization and Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Sub Code:                                                                                                                                                                 | 21CS34                                                                                          | Branch: | CSE |    |      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------|-----|----|------|

| Date: | 27/12/22 Duration: 90 minutes Max Marks: 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sem / Sec:                                                                                                                                                                | III / A                                                                                         | A, B, C |     | OF | BE . |

|       | Answer any FIVE FULL Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                         |                                                                                                 |         | RKS | CO | RBT  |

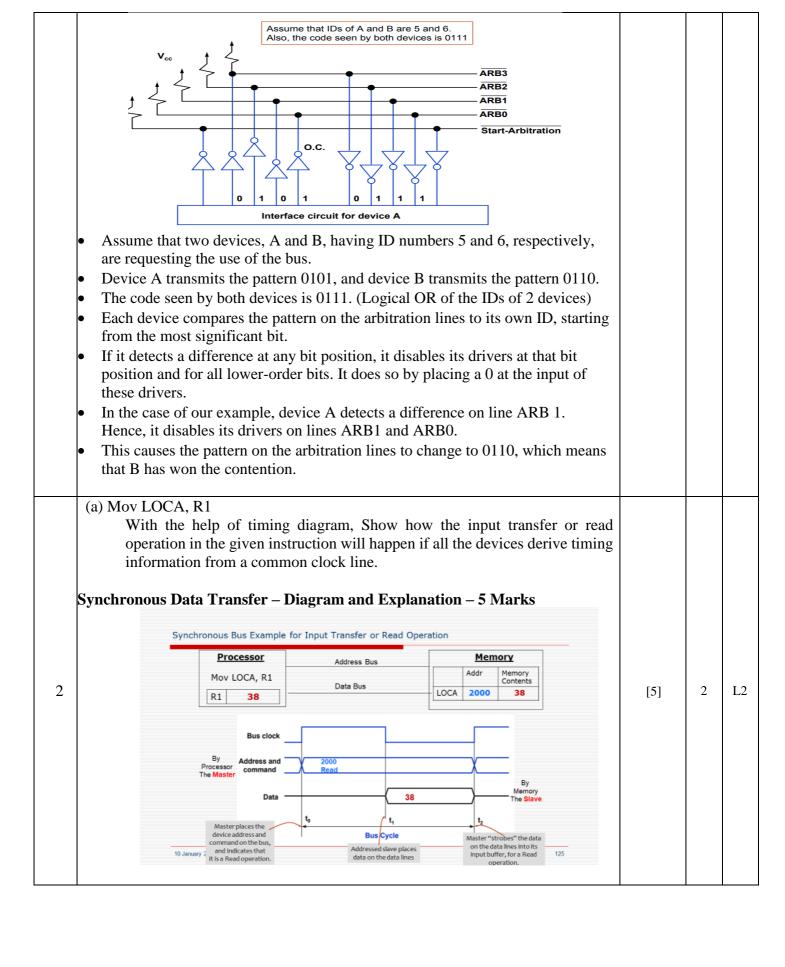

| 1     | What is the process needed to resolve the conflict who use the bus to access main memory?  Explain any 2 approaches in detail with figure.  Bus Arbitration − 2 Marks  The process by which the next device to become the mastership is transferred to it is called bus arbitration.  Two approaches for Bus arbitration  1. Centralized arbitration: 4 Marks  A single bus arbiter performs the arbitration. Usual arbiter  A single bus arbiter performs the arbitration. Usual arbiter  A single bus-arbiter performs the required arbitration  Normally, processor is the bus-master.  Processor may grant bus-mastership to one of the DMA control A DMA controller indicates that it hogical OR of bus-requests from then, processor activates BG1 signal indicating to DMA control BG1 signal is connected to all DMA controllers using a daisy-ch  If DMA controller-1 is requesting the bus, Then, DMA controller-1 blocks propagation of grant-signa Otherwise, DMA controller-1 passes the grant downstrean Current bus-master indicates to all devices that it is using bus  The bus-arbiter is used to coordinate the activities of all device Arbiter ensures that only 1 request is granted at any given time (BR → Bus-Request, BG → Bus-Grant, BBSY → Bus Busy)  2. Distributed arbitration: 4 Marks  All devices participate in the selection of the next bus | DMA Controller  lers. by activating Bf all devices contiers to use bus wain arrangement by activating BB by activating BB s requesting BB s requesting mee according to a | selected and will be the  R line. nected to it. when it becomes s. G2. SY line. mory transfers. | bus Bus | 10] | 2  | L2   |

|   | (b) What is Virtual Memory? Explain its basic organization with neat diagram.                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |   |    |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|----|

|   | Diagram and Explanation – 5 Marks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |   |    |

|   | <ul> <li>Virtual memory – separation of user logical memory from physical memory.</li> <li>Only part of the program needs to be in memory for execution.</li> <li>Logical address space can therefore be much larger than physical address space.</li> <li>Allows address spaces to be shared by several processes.</li> <li>Allows for more efficient process creation.</li> <li>A special hardware unit, called the Memory Management Unit (MMU), translates virtual addresses into physical addresses.</li> </ul> | [5] | 3 | L1 |

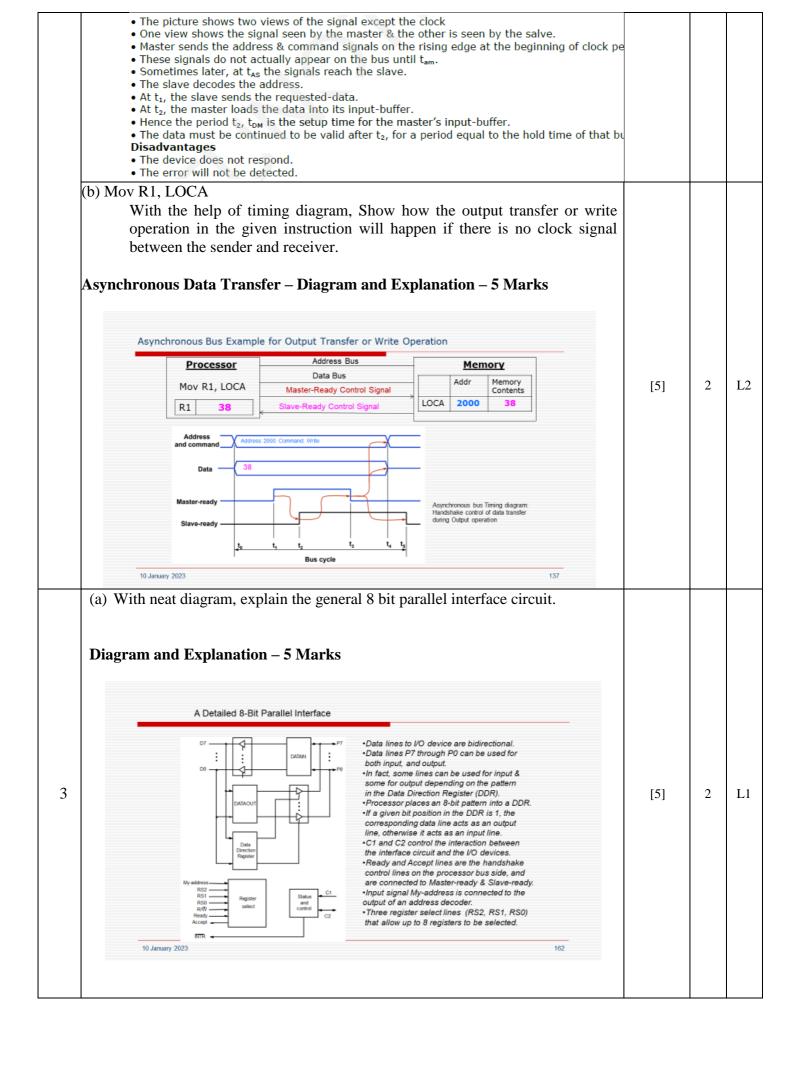

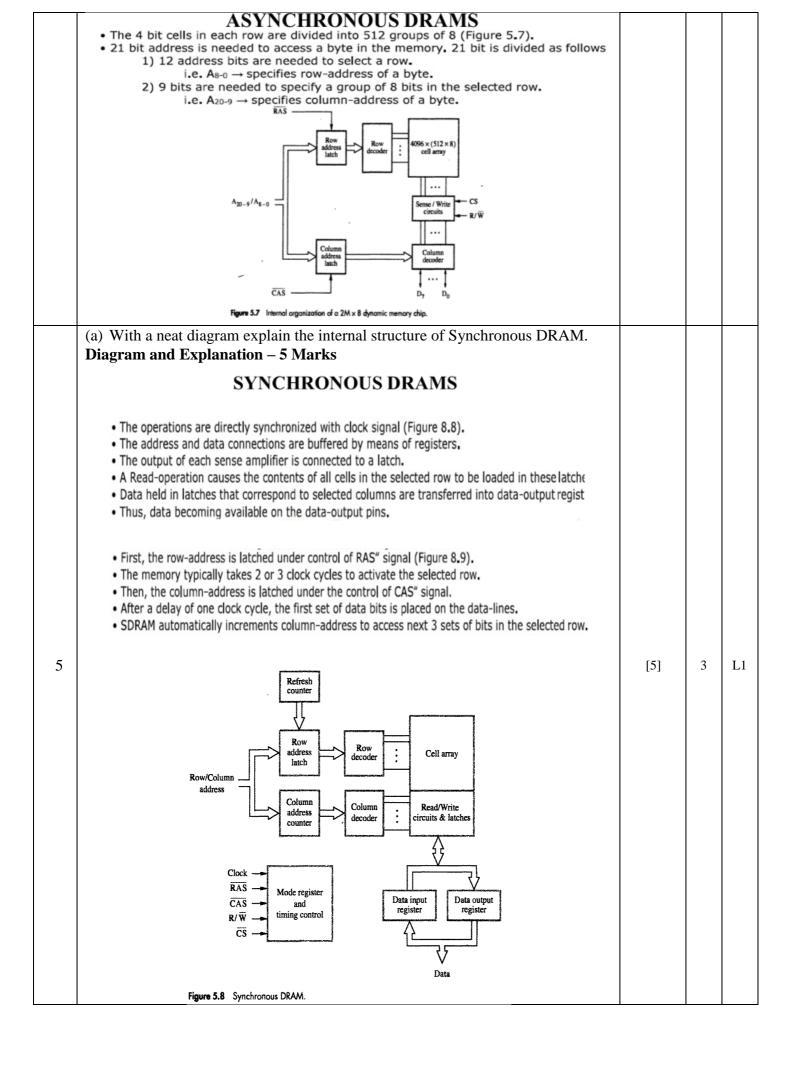

| 4 | Diagram and Explanation – 5 Marks    S-bit row address                                                                                                                                                                                                                                                                                                                                                                                                                                                               | [5] | 3 | L1 |

| - | <ul> <li>(b) With a neat diagram briefly explain the internal organization of 16 Megabit dynamic memory chip configured as 2M x 8</li> <li>Diagram and Explanation – 5 Marks</li> </ul>                                                                                                                                                                                                                                                                                                                              | [5] | 3 | L1 |

|   | (b) Analyze how data are written into Read Only Memories. Discuss the different types of Read Only Memories.                                                                                                                                                                                     |     |   |     |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|-----|

|   | ROM Cell – 2 Marks                                                                                                                                                                                                                                                                               |     |   |     |

|   | ROM Bit line                                                                                                                                                                                                                                                                                     |     |   |     |

|   | Word line  Connected to store a 0  Not connected to store a 1                                                                                                                                                                                                                                    |     |   |     |

|   | Figure 5.12 A ROM cell.                                                                                                                                                                                                                                                                          | [5] | 3 | L2  |

|   | <ul> <li>At Logic value '0' → Transistor(T) is connected to the ground point (P).         Transistor switch is closed &amp; voltage on bit-line nearly drops to zero     </li> <li>At Logic value '1' → Transistor switch is open.         The bit-line remains at high voltage.     </li> </ul> | [5] | 3 | 1.2 |

|   | Types of ROM with explanation – 3 Marks                                                                                                                                                                                                                                                          |     |   |     |

|   | • ROM                                                                                                                                                                                                                                                                                            |     |   |     |

|   | <ul> <li>PROM (Programmable Read Only Memory)</li> <li>EPROM (Erasable Programmable Read Only Memory)</li> <li>EEPROM (Electrically Erasable Programmable Read Only Memory)</li> <li>Flash <ul> <li>Flash Cards</li> <li>Flash Drives</li> </ul> </li> </ul>                                     |     |   |     |

|   | (a) Consider the following 2 scenarios and answer the questions under each.                                                                                                                                                                                                                      |     |   |     |

|   | A cache is organized in direct-mapped manner with the following parameters: Main memory size 32K words; Cache size 512 words; Block size 64 words (i) How many bits are there in a main memory address? (ii) How many bits are there in each of the TAG, BLOCK and WORD fields?                  |     |   |     |

|   | MAIN MEMORY                                                                                                                                                                                                                                                                                      |     |   |     |

| 6 | Total Size $-32,768$<br>That can be represented with $2^x$ addresses<br>Therefore Address length $=$ <b>15 bits</b> . ( $2^{15} = 32,768$ )<br><b>WORD</b>                                                                                                                                       | [5] | 3 | L3  |

|   | 64 Words per block<br>6 <b>bits</b> for WORD field (2 <sup>6</sup> = 64)                                                                                                                                                                                                                         |     |   |     |

|   | BLOCK No. of Blocks = Total Cache Size / Words per block = 1024 / 128 = 8 3 bits for BLOCK field (8 Blocks = 2 <sup>3</sup> = 8)                                                                                                                                                                 |     |   |     |

|   | TAG Remaining 6 bits for TAG field.                                                                                                                                                                                                                                                              |     |   |     |

|             | ek-set-associate cache consists of a total of 128 blocks divided into 8-block       |     |   |   |

|-------------|-------------------------------------------------------------------------------------|-----|---|---|

| sets.       |                                                                                     |     |   |   |

|             | ain memory contains 4096 blocks, each consisting of 128 words.                      |     |   |   |

| (i) Ho      | w many bits are there in a main memory address?                                     |     |   |   |

| (ii) Ho     | ow many bits are there in each of the TAG, SET and WORD fields?                     |     |   |   |

| Answer      |                                                                                     |     |   |   |

| Main Men    | nory size=4096 blocks x128 words                                                    |     |   |   |

|             | =4 x 1024 x 128                                                                     |     |   |   |

|             | $=2^2 \times 2^{10} \times 2^7 = 2^{19}$                                            |     |   |   |

| Hence nun   | nber of bits for address is <b>19-bits</b>                                          |     |   |   |

| Word – 7    |                                                                                     |     |   |   |

| Set - 4     |                                                                                     |     |   |   |

| Tag – 8 bit |                                                                                     |     |   |   |

|             |                                                                                     |     |   |   |

|             | e the following with respect to cache memory                                        |     |   |   |

| (i) Ma      | apping Function (ii) Replacement Algorithm (iii) Stale Data                         |     |   |   |

|             | (iv) Write Through Protocol (v) Write Back Protocol                                 |     |   |   |

|             |                                                                                     |     |   |   |

| Each 1 Ma   |                                                                                     |     |   |   |

| (i)         | Mapping Function                                                                    |     |   |   |

|             | At any given time, only some blocks in the main memory are held in                  |     |   |   |

|             | the cache. Which blocks in the main memory are in the cache is                      |     |   |   |

|             | determined by a "mapping function".                                                 |     |   |   |

| (ii)        | Replacement Algorithm                                                               |     |   |   |

| (/          | When the cache is full, and a block of words needs to be transferred                |     |   |   |

|             | from the main memory, some block of words in the cache must be                      |     |   |   |

|             | replaced. This is determined by a " <b>replacement algorithm</b> ".                 |     |   |   |

|             | replaced. This is determined by a replacement argorithm.                            |     |   |   |

| (iii)       | Stale Data                                                                          | [5] | 3 | I |

|             | During a DMA transfer from Main Memory to Disk and the cache                        |     |   |   |

|             | uses write-back protocol, the data in memory might not reflect the                  |     |   |   |

|             | changes that have been made in the cached copy. That outdated data in               |     |   |   |

|             | the memory is called the stale data                                                 |     |   |   |

|             |                                                                                     |     |   |   |

| (iv)        | Write Through Protocol                                                              |     |   |   |

|             | Contents of the cache and the main memory may be updated                            |     |   |   |

|             | simultaneously. This is the write-through protocol.                                 |     |   |   |

| (v)         | Write Back Protocol                                                                 |     |   |   |

|             | Update the contents of the cache, and mark it as updated by setting a               |     |   |   |

|             | bit known as the <b>dirty bit</b> or <b>modified bit</b> . The contents of the main |     |   |   |

|             | memory are updated when this block is replaced. This is write-back                  |     |   |   |

|             | or copy-back protocol.                                                              |     |   |   |

|             | or copy when protocor.                                                              |     | 1 |   |

## **CO PO Mapping**

|     | Course Outcomes                                                                                      | Modules | P01 | PO2 | P03 | P04 | PO5 | 90d | PO7 | P08 | PO9 | PO10 | P011 | P012 | PSO1 | PSO2 | PSO3 | PSO4 |

|-----|------------------------------------------------------------------------------------------------------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|

| CO1 | Explain the organization and architecture of computer systems with machine instructions and programs | 1       | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    | -    | -    |

| CO2 | Analyze the input/output devices communicating with computer system                                  | 2       | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | 2    | -    | -    | -    |

| CO3 | Demonstrate the functions of different types of memory devices                                       | 3       | 2   | 2   | 2   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 2    | -    | -    |

| CO4 | Apply different data types on simple arithmetic and logical unit                                     | 4       | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 2    | -    | -    |

| CO5 | Analyze the functions of basic processing unit, Parallel processing and pipelining                   | 5       | 3   | 2   | 3   | 2   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 2    | -    | -    |

| COGNITIVE<br>LEVEL | REVISED BLOOMS TAXONOMY KEYWORDS                                                                                                              |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| L1                 | List, define, tell, describe, identify, show, label, collect, examine, tabulate, quote, name, who, when, where, etc.                          |

| L2                 | summarize, describe, interpret, contrast, predict, associate, distinguish, estimate, differentiate, discuss, extend                           |

| L3                 | Apply, demonstrate, calculate, complete, illustrate, show, solve, examine, modify, relate, change, classify, experiment, discover.            |

| L4                 | Analyze, separate, order, explain, connect, classify, arrange, divide, compare, select, explain, infer.                                       |

| L5                 | Assess, decide, rank, grade, test, measure, recommend, convince, select, judge, explain, discriminate, support, conclude, compare, summarize. |

| PF   | CORRELATION<br>LEVELS                                                              |                                                           |                                       |                |                      |  |  |  |  |

|------|------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------|----------------|----------------------|--|--|--|--|

| PO1  | Engineering knowledge                                                              | PO7                                                       | 0                                     | No Correlation |                      |  |  |  |  |

| PO2  | Problem analysis                                                                   | alysis PO8 Ethics                                         |                                       |                | Slight/Low           |  |  |  |  |

| PO3  | Design/development of solutions                                                    | ign/development of solutions PO9 Individual and team work |                                       | 2              | Moderate/<br>Medium  |  |  |  |  |

| PO4  | Conduct investigations of complex problems                                         | PUILL Communication                                       |                                       | 3              | Substantial/<br>High |  |  |  |  |

| PO5  | Modern tool usage                                                                  |                                                           |                                       |                |                      |  |  |  |  |

| PO6  | The Engineer and society PO12 Life-long learning                                   |                                                           |                                       |                |                      |  |  |  |  |

| PSO1 | Develop applications using differe                                                 | nt stacks                                                 | s of web and programming technologic  | es             |                      |  |  |  |  |

| PSO2 | 2 Design and develop secure, parallel, distributed, networked, and digital systems |                                                           |                                       |                |                      |  |  |  |  |

| PSO3 | Apply software engineering method                                                  | ds to de                                                  | sign, develop, test and manage softwa | re sys         | stems.               |  |  |  |  |

| PSO4 | Develop intelligent applications for                                               | or busine                                                 | ess and industry                      |                |                      |  |  |  |  |