| USN                          |  |  |  |  |  |  |  |  |  |  |

|------------------------------|--|--|--|--|--|--|--|--|--|--|

| Internal Assessment Test – I |  |  |  |  |  |  |  |  |  |  |

| Sub:  | Microcontrollers                                                                                        |                |                  |                  |           |         |                 | Code: |       | 18EE52 |     |

|-------|---------------------------------------------------------------------------------------------------------|----------------|------------------|------------------|-----------|---------|-----------------|-------|-------|--------|-----|

| Date: | 11/11/2021                                                                                              | Duration:      | 90 mins          | Max Marks:       | 50        | Sem:    | 5 <sup>th</sup> | Br    | anch: | EEI    | Ξ   |

|       |                                                                                                         | A              | nswer <b>Any</b> | y FIVE FULL      | Question  | ıs      |                 |       | ,     |        |     |

|       |                                                                                                         |                |                  |                  |           |         |                 |       | Marks | OB     | Е   |

|       |                                                                                                         |                |                  |                  |           |         |                 |       |       | CO     | RBT |

|       | Explain the memory organization of 8051 with suitable diagrams.                                         |                |                  |                  |           |         |                 |       |       | CO2    | L1  |

|       | Internal RAM Organization diagram- 3 marks                                                              |                |                  |                  |           |         |                 |       |       |        |     |

|       | Working register b                                                                                      |                | <b>KS</b>        |                  |           |         |                 |       |       |        |     |

|       | Bit Addressable -2                                                                                      |                |                  |                  |           |         |                 |       |       |        |     |

|       | Scratch pad-2 Mar                                                                                       | `KS            |                  |                  |           |         |                 |       |       |        |     |

|       | ROM- 1 marks Explain with suitable                                                                      | le evample t   | he differe       | ent types of ad  | dreccina  | r modes | nsed            |       | 10    | CO1    | L1  |

|       | in 8051.                                                                                                | ic example, t  | iic differe      | on types of ad   | aressing  | 5 modes | uscu            |       | 10    | COI    | Li  |

|       | Five Addressing m                                                                                       | odes along     | with exar        | nples            |           |         |                 |       |       |        |     |

|       | 1. Immediate Addr                                                                                       | _              |                  | -                |           |         |                 |       |       |        |     |

|       | 2.Register addressi                                                                                     | 0              |                  |                  |           |         |                 |       |       |        |     |

|       | 3.Indirect Address                                                                                      |                |                  |                  |           |         |                 |       |       |        |     |

|       | 4. Register Indirect Addressing Mode- 2 marks                                                           |                |                  |                  |           |         |                 |       |       |        |     |

|       | 5. Indexed Address                                                                                      | sing mode- 2   | 2Marks           |                  |           |         |                 |       |       |        |     |

| 5     | With a neat block di                                                                                    | iagram of 80   | 51. brief        | about its salier | nt featur | res.    |                 |       | 10    | CO2    | L1  |

|       | With a neat block diagram of 8051, brief about its salient features.  10 CO2 L1  Block Diagram- 4 Marks |                |                  |                  |           |         |                 |       |       |        |     |

|       | <b>Salient Features-6</b>                                                                               |                |                  |                  |           |         |                 |       |       |        |     |

| 6     | Explain in brief for the following                                                                      |                |                  |                  |           |         |                 |       | 10    | CO1    | L4  |

|       | 1. Program Counter & DPTR 2. PSW3.Stack Pointer 4.Register Bank                                         |                |                  |                  |           |         |                 |       |       |        |     |

|       | Each Brief                                                                                              |                | – 2.5 ma         | rks              |           |         |                 |       |       |        |     |

| 7     | Compare the follow                                                                                      |                |                  |                  |           |         |                 |       | 10    | CO1    | L3  |

|       | i)CISC & RISC -a                                                                                        |                |                  |                  |           |         |                 |       |       |        |     |

|       | ii) Microprocessor                                                                                      | & Microco      | ntroller-        | any five diffe   | rence -   | 5M      |                 |       |       |        |     |

|       | Write an ALP to tog                                                                                     | ggle all the b | its of P0        | & P1-            |           |         |                 |       | 10    | CO2    | L4  |

|       | ALP -5M                                                                                                 |                |                  |                  |           |         |                 |       |       |        |     |

|       | b. Write an ALP to                                                                                      | take the com   | plement (        | of value 68h fo  | or 1000   | times.  |                 |       |       |        |     |

|       | ALP -5M                                                                                                 |                | 1 . "            |                  |           |         |                 | _     | 10    | 00.4   | 1.0 |

|       | Explain the four por                                                                                    |                |                  |                  |           |         |                 |       | 10    | CO4    | L2  |

|       | Four ports explain                                                                                      |                |                  |                  |           |         |                 |       | 10    | CO2    | 1.2 |

| 3.    | Explain the logical i                                                                                   |                |                  |                  | M 0= -1   |         |                 |       | 10    | CO2    | L2  |

|       | AND, OR, XOR, C                                                                                         | rl expiana     | uon With         | ı exampie-2.51   | vi each   |         |                 |       |       |        |     |

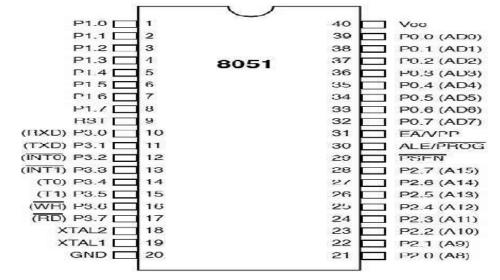

# 1. Ports of 8051

- To access the pins of port O as input & output ports, each pin must be connected externally to a 10K pull-up resistor.

- Port 0 is designated as AD0-AD7, allowing it to be used for both address & data.

- When Port 0 is connected to an external memory, port 0 provides address and data.

### Port-1

- Total of 8 pins.

- Can be used as an input or output.

- Does not require any pull up resistors

- If port 1 has been configured as an output port, to make it an input port again, it can programmed by writing 1 to all its bits.

### Port-2

- Total of 8 pins.

- Do not require pull up resistor.

- On reset, port 2 is configured as an input port.

# Port-3

- Total of 8 pins.

- Do not require pull up resistor

- Port 3 has the additional function of providing extremely important signal such as interrupts.

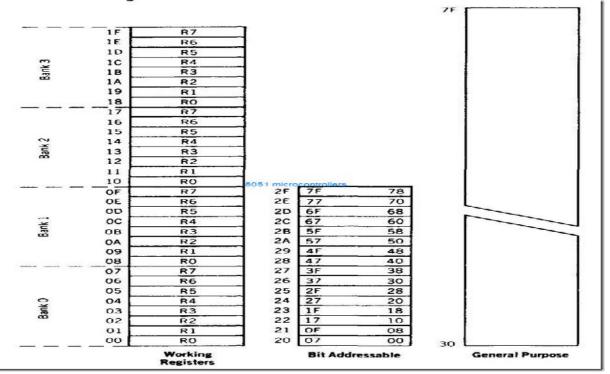

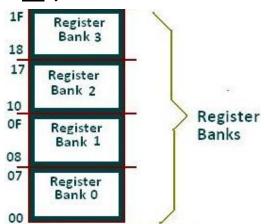

• Four register banks.

2.

- Each bank containing 8 registers labeled from R0-R7.

- Total of 32 working registers labeled from 00-1FH.

- By default bank 0 will be selected on reset

| Bank 0 | Bank 1 | Bank 2 | Bank 3 |

|--------|--------|--------|--------|

| 7 R7   | F R7   | 17 R7  | 1F R7  |

| 6 R6   | E R6   | 16 R6  | 1E R6  |

| 5 R5   | D R5   | 15 R5  | 1D R5  |

| 4 R4   | C R4   | 14 R4  | IC R4  |

| 3 R3   | B R3   | 13 R3  | 1B R3  |

| 2 R2   | A R2   | 12 R2  | 1A R2  |

| 1 R1   | 9 R1   | 11 R1  | 19 R1  |

| 0 R0   | 8 R0   | 10 R0  | 18 R0  |

### Bit Addressable RAM

16 bytes of RAM from address 20h to 2fh are bit addressable.

Each bit of has an address and can be accessed individually

Total of 128 bits address is given in the register bank.

General purpose RAM-registers above bit addressable registers are called Scratch pad registers. Used for temporary

Addressing Modes. The CPU can acces data in nations nearys. The data could be in a register, be in memory or be promided as an enmediate name. The various ways of accessing a data are called addressing Modes. There are fine different types of Addressing Mode are called addressing modes. 1. Immediate 2. Register 3. priect 4. Regrister Indirect 5. Indexed. 1. Immediate · Addressing Mode :--) In this addressing needle, the source operand is a constant i e immediate data. I The immediate data must be preceded by the pround -) This oddereng made can be used to load information the DPTR legister. I The immediate data must is -) This oddersoning made can be used to load information cuito any of the segnitees wicholing the DPTR segniter.

; head 56H wito Accumulate

Eg: 10 MOVA, #56H MOV R3, # 62; load the decimal habite box Lito R3 MOU B, #40H ; load 404 wito B MOU DATE, \$145214; DATE = 45124.

MOU DPTR, #2550H. DPL, #50H MOV MOU . DPH, #25H.

2. Register Addressing Mode:-91 in notices the use of registers to hold the data to be completed.

Eg: MOV A, Ro; copy the contents of Ro into A MOV Ro, A: copy the contents of A cito Ro ADD A, R5; Add the contents of A for the Contents of R5 ADD A, R7; add the contents of R7 to MOV R6, A; Save the accumulator in R6

-) The size of the source of distination should be matched.

Eg: O MOU DPTR, #25F5H -> valid.

Source is A > & bit Register

Destination is > 16 bit Register

The data can be moved between the accumulator of Rn (for n=0 to 7), but the movement of data between 2n is not allowed.

Eg:- MOU A, RO <u>valid</u>.

MOU RO, R7 <u>invalid</u>.

The data is in a RAM memory to cali on whose addressing is known of this enddress is given as past of a construction.

Although the entire 12x boytes of RAM can be addressing the hing direct addressing Made.

Is must often used to access RAM locations 30-7FH.

If is must often used to access RAM locations of RAM.

Rg: MOV RO, 40H; sop save the contents of RAM.

Rg: MOV RO, 40H; sop save the contents of A into RAM location 40H to RO.

RAM location 47-4.

In the Register indirect addressing mode, a significant is used as a positive to the data, only hegister to & RI are undirect data transfer. 4. Indirect Addressing Mode: when they hold the address of ROM Tolestions they must be preceded by the @ symbol. ; more the contents of RAM Eg: MOUA, @RO location of 20 into A. ; more the bontents of B into MOU QRI, B the kan location whose address 5. Indeped Addressing Mode's held at 21. Indexed addressing mode is said andely hard in accessing data elements of look-up table entries localed in the program Rom space of the 8051. Eq: MOU A, @A+DPTR

MOVA, QA+PC.

# 6.Register Bank

- Four register banks.

- Each bank containing 8 registers labeled from R0-R7.

- Total of 32 working registers labeled from 00-1FH.

- By default bank 0 will be selected on reset

| Bank 0 | Bank 1 | Bank 2 | Bank 3 |

|--------|--------|--------|--------|

| 7 R7   | F R7   | 17 R7  | 1F R7  |

| 6 R6   | E R6   | 16 R6  | 1E R6  |

| 5 R5   | D R5   | 15 R5  | 1D R5  |

| 4 R4   | C R4   | 14 R4  | 1C R4  |

| 3 R3   | B R3   | 13 R3  | 1B R3  |

| 2 R2   | A R2   | 12 R2  | 1A R2  |

| 1 R1   | 9 R1   | 11 RI  | 19 R1  |

| 0 R0   | 8 R0   | 10 R0  | 18 R0  |

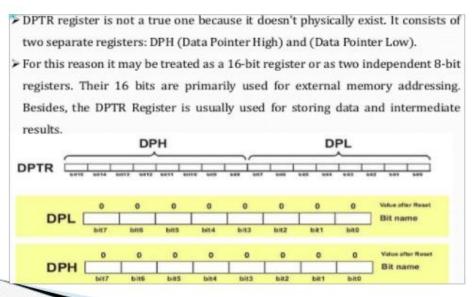

**Data Pointer**

PSW-Program Status word

The 8051 Mc has a flag rigister to indicate authoretic conditions buch as like Carry bits. The flag register en the 8051 is Called the program status word (PSW) register.

The Program Status wood (PSW) register is an 8-bit register. Hence it is refused to as the flag register. It have used by the PSW is a 8 bit wide, only 6 bits of it are used by the 8051. The two named bits are used - olefinable flags. I form of the flags are called conditional flags, that they indicate some conditions that the result after an instantian is escented. The form flags are CY (Carry), Ac (Anxi hisry Carry), P (Parity) & OU (Onerflow).

|                                         |                                         |                   |                                | V.                                        |      |                      |        |          |     |            |   |

|-----------------------------------------|-----------------------------------------|-------------------|--------------------------------|-------------------------------------------|------|----------------------|--------|----------|-----|------------|---|

| cy                                      | AC                                      | F0                | RSI                            | RS0                                       | OV   |                      | P      |          |     | 3 .        |   |

| CY<br>AC<br>FO<br>RSI<br>RS2<br>OV<br>P | PSW. PSW. PSW. PSW. PSW. PSW. PSW. PSW. | 7<br>5<br>4<br>.3 | Anxi<br>Avai<br>Regis<br>Regis | y flag<br>hary<br>lable<br>ter B<br>ter I | flag | te no<br>Sele<br>Sel | see fo | e go bit | o . | lwase each | h |

# Stack in the 8051.

The stack is a section of RAM need by the CPU to store enformation tempor arily. This enformation could be deata as an address.

of The register used to access the stack is called the Stack pointer register. The Stack pointer in the 8051 is only 8 bits wide, which means that it can take values of oo to FFH.

of, which means that RAM location 08 is the first water used for & the stack by the 8051 -> The storing of a CPU register in the stack is called PUSH of pulling the contents off the stack back wito a CPU register is Called a POP.

Pushing onto the Stack.

In the 8051, the stack pointer (SP) points to the last used location of the stack.

I when the data is forehed onto the stack, the stack fronter (SP) is incremented by one.

Popping the contents of the stack hack into a given register is the opposite process of pushing. Register is the opposite process of pushing.

I with every prop, the top byte of the stack is copied to the register specified by the instanction of the stack pointer is decremented once.

# **DATA POINTER**

| Microprocessor                                                                                                                                          | Micro Controller                                                                                                                                 |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Read-Only Read-Write Memory (ROM) Memory Serial                                                                                                         | Microcontroller Read-Only Read-Write Memory                                                                                                      |  |  |  |  |  |  |

| System Bus I/O Port                                                                                                                                     | Timer I/O Port Serial Interface                                                                                                                  |  |  |  |  |  |  |

| Microprocessor is heart of Computer system.                                                                                                             | Micro Controller is a heart of embedded system.                                                                                                  |  |  |  |  |  |  |

| It is just a processor, Memory and I/O components have to be connected externally                                                                       | Micro controller has external processor along with internal memory and i/O components                                                            |  |  |  |  |  |  |

| Since memory and I/O has to be connected externally, the circuit becomes large.                                                                         | Since memory and I/O are present internally, the circuit is small.                                                                               |  |  |  |  |  |  |

| Cannot be used in compact systems and hence inefficient                                                                                                 | Can be used in compact systems and hence it is an efficient technique                                                                            |  |  |  |  |  |  |

| Cost of the entire system increases                                                                                                                     | Cost of the entire system is low                                                                                                                 |  |  |  |  |  |  |

| Due to external components, the entire power consumption is high. Hence it is not suitable to used with devices running on stored power like batteries. | Since external components are low, total power consumption is less and can be used with devices running on stored power like batteries.          |  |  |  |  |  |  |

| Most of the microprocessors do not have power saving features.                                                                                          | Most of the micro controllers have power saving modes like idle mode and power saving mode. This helps to reduce power consumption even further. |  |  |  |  |  |  |

| Since memory and I/O components are all external, each instruction will need external operation, hence it is relatively slower.                         | Since components are internal, most of the operations are internal instruction, hence speed is fast.                                             |  |  |  |  |  |  |

| Microprocessor have less number of registers, hence more operations are memory based.                                                                   | Micro controller have more number of registers, hence the programs are easier to write.                                                          |  |  |  |  |  |  |

| Microprocessors are based on von Neumann<br>model/architecture where program and data are stored<br>in same memory module                               | Micro controllers are based on Harvard architecture<br>where program memory and Data memory are separate                                         |  |  |  |  |  |  |

| Mainly used in personal computers                                                                                                                       | Used mainly in washing machine, MP3 players                                                                                                      |  |  |  |  |  |  |

| RISC                                                                                                                      | CISC                                                                                            |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                           |                                                                                                 |  |  |  |  |  |

| It is a Reduced Instruction Set Computer.                                                                                 | It is a Complex Instruction Set Computer.                                                       |  |  |  |  |  |

| It emphasizes on software to optimize the instruction set.                                                                | It emphasizes on hardware to optimize the instruction set.                                      |  |  |  |  |  |

| It is a hard wired unit of programming in the RISC Processor.                                                             | Microprogramming unit in CISC Processor.                                                        |  |  |  |  |  |

| It requires multiple register sets to store the instruction.                                                              | It requires a single register set to store the instruction.                                     |  |  |  |  |  |

| RISC has simple decoding of instruction.                                                                                  | CISC has complex decoding of instruction.                                                       |  |  |  |  |  |

| Uses of the pipeline are simple in RISC.                                                                                  | Uses of the pipeline are difficult in CISC.                                                     |  |  |  |  |  |

| It uses a limited number of instruction that requires less time to execute the instructions.                              | It uses a large number of instruction that requires more time to execute the instructions.      |  |  |  |  |  |

| It uses LOAD and STORE that are independent instructions in the register-to-register a program's interaction.             | It uses LOAD and STORE instruction in the memory-to-memory interaction of a program.            |  |  |  |  |  |

| RISC has more transistors on memory registers.  CISC                                                                      | has transistors to store complex instructions.                                                  |  |  |  |  |  |

| The execution time of RISC is very short.                                                                                 | The execution time of CISC is longer.                                                           |  |  |  |  |  |

| RISC architecture can be used with high-end applications like telecommunication, image processing, video processing, etc. | CISC architecture can be used with low-end applications like home automation, secu system, etc. |  |  |  |  |  |

### 1. AND

ANL Destination, Source

- Performs a logical AND operation of two operands and place the result in the destination.

- The source operand can be register, memory or immediate.

- The destination: Accumulator

Eg: MOV A, #35H 0011 0101

ANL A, #0FH 0000 1111

### 0000 0101

### XRL destination, source

- Performs a logical XOR operation of two operands and place the result in the destination.

- The source operand can be register, memory or intermediate.

- The destination: Accumulator

- Used to check if two registers have the same value.

Eg: XRL A,R1

## XRL destination, source

- Performs a logical XOR operation of two operands and place the result in the destination.

- The source operand can be register, memory or intermediate.

- The destination: Accumulator

- Used to check if two registers have the same value.

Eg: XRL A,R1

This instruction complements the contents of registers A

Eg 1: MOV A, #85H 1000 0101 -85

CPL A 0111 1010 – 7A

ADD A,#1 0111 1011-7B

Eg 2:MOV A, #55H

CPL A ;now A=AAH ; 0101 0101(55H)

;becomes 1010 1010(AAH)

#### 8.

```

ORG OH ; START PROGRAM FROM OH

START: MOV A, #0;

MOV P1, A;

MOV P0,a

MOV R0, #30H;

ACALL DELAY; CALL DELAY

CPL A; COMPLEMENT A TO TOGGLE

MOV P1, A; TOGGLE P1 BY TRANSFERING A

```

Mov p0,a Mov R0, #OFFH; CHANGE R0 VALUE TO CHANGE DELAY ACALL DELAY; CALL DELAY WITH DIFFERENT R0 SJMP START; JUMP BACK TO START

DELAY: NOP ; DELAY SUBROUTINE

LOOP: DJNZ RO, LOOP;

RET ;

END

ORG 00H

Mov a,#68H

MOV R3,#10

NEXT: MOV R2,#10

AGAIN: CPL A

DJNZ R2, AGAIN

DJNZ R3, NEXT

**END**