| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

## Internal Assessment Test 3–February 2023

## Scheme & Solution

| Sub:  | Computer Organization and Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SubCode:                                                          | 21CS34                                                                                         | Bra               | nch:         | ISE   |     |     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------|--------------|-------|-----|-----|

| Date: | 09/02/2023   Duration:   90min's   MaxMarks:   50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Sem/Sec:                                                          | III A, B &C                                                                                    |                   |              |       | OB  | E   |

|       | Answer any FIVE FULL Questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                   |                                                                                                |                   |              | RKS   |     | RBT |

| 1     | Explain the internal organization of a 16 Megabits DRAM ch Also, describe how it can be made to work in fast page mode.  RAS  ROW  address latch  ROW  address latch  Column  address latch  Column  decoder  Column  decoder  Total of 21 bits.  First apply the row address, RAS signal latches the row ad address, CAS signal latches the address.  Timing of the memory unit is controlled by a specialized to CAS. This is asynchronous DRAM  Suppose if we want to access the consecutive bytes in the s  This can be done without having to reselect the row.  Add a latch at the output of the sense circuits in example.  All the latches are loaded when the row is selecte.  Different column addresses can be applied to sele the data lines.  Consecutive sequence of column addresses can be applied without reselecting the row.  Allows a block of data to be transferred at a much accesses.  A small collection/group of bytes is usually referred. | go bits to selected row each row. Each and places the faster rate | ect a group in a sapply the colurgenerates RAS as different bytes ontrol signal CA than random | row.<br>nn<br>und | 10(D<br>m-3+ | iagra | CO3 | L2  |

|       | <ul> <li>This transfer capability is referred to as the fast page mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                   |                                                                                                |                   |              |       |     |     |

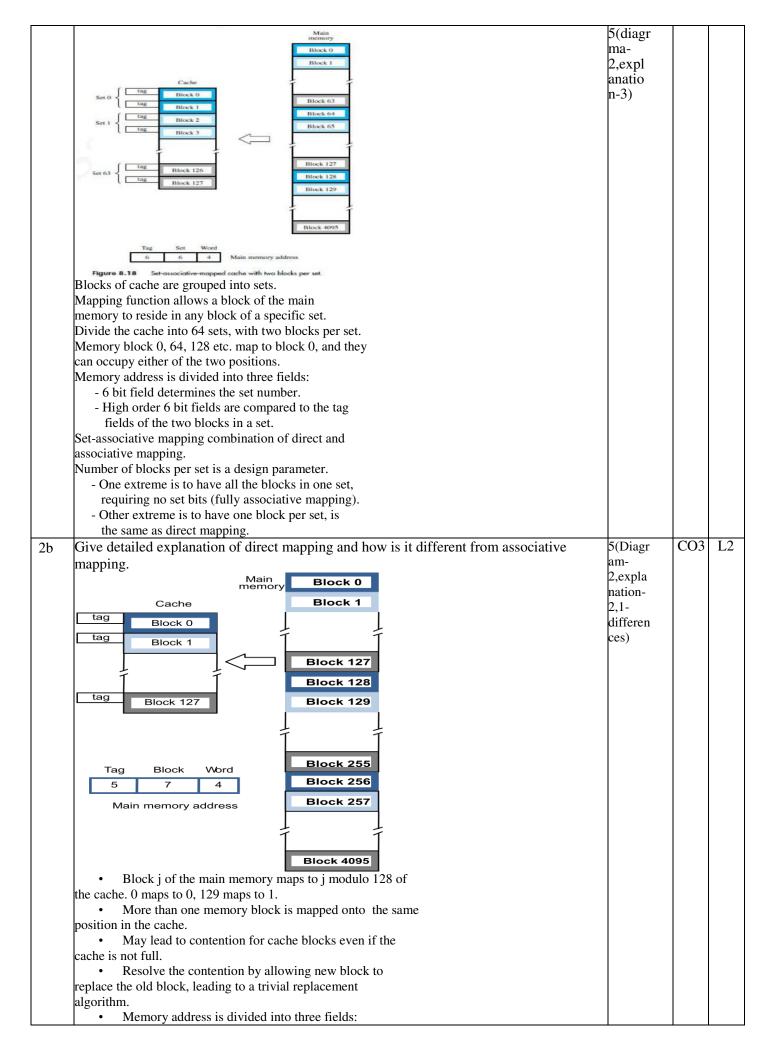

| 2a    | Explain Set Associative Memory in detail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                   |                                                                                                |                   |              |       | CO3 | L2  |

| •      | Ai* Bi + Ci for $i = 1, 2, 3,,$                                     | ows through the pipeline one step at a time.                                                                        |                           |     |   |

|--------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------|-----|---|

|        | activity.                                                           |                                                                                                                     |                           |     |   |

|        | of the next segment.                                                | ers after enough time has elapsed to perform all segment                                                            |                           |     |   |

|        | particular segment.                                                 | al circuit in a given segment is applied to the input register                                                      |                           |     |   |

| •      | Each segment consists of an in                                      | put register followed by a combinational circuit. the combinational circuit performs the suboperation in the        |                           |     |   |

| •      |                                                                     | between each segment so that each can operate on distinct                                                           |                           |     |   |

| •      | The overlapping of computation segment in the pipeline.             | on is made possible by associating a register with each                                                             |                           |     |   |

| •      | It is characteristic of pipelines segments at the same time.        | that several computations can be in progress in distinct                                                            |                           |     |   |

| •      | The final result is obtained after                                  | er the data have passed through all segments.                                                                       |                           |     |   |

| •      |                                                                     | omputation in each segment is transferred to the next                                                               |                           |     |   |

| •      | information flows.  Each segment performs partial                   | processing dictated by the way the task is partitioned.                                                             | 2)                        |     |   |

| •      | with all other segment.  A pipeline can be visualized as            | a collection of processing segments through which binary                                                            | n-<br>5,eg                |     |   |

| •      | each subprocess being executed                                      | composing a sequential process into suboperations, with d in a special dedicated segment that operates concurrently | gram-<br>3,Expl<br>anatio |     |   |

| Explai | n pipelining with the necessar                                      | y diagram and example.                                                                                              | 10(Dia                    | CO5 | I |

| •      | Cost is higher than direct-mapped determine whether a given blo     | bed cache because of the need to search all 128 patterns to                                                         |                           |     |   |

| •      | Replacement algorithms can be cache is full.                        | e used to replace an existing block in the cache when the                                                           |                           |     |   |

| •      | Flexible, and uses cache space                                      | efficiently.                                                                                                        |                           |     |   |

| are    | tag bits. Simple to implement but not ve                            | ary flavibla                                                                                                        |                           |     |   |

|        | gh order 5 bits determine which oblocks is currently present in the |                                                                                                                     |                           |     |   |

|        | ck this new block is placed in.                                     | f the pessible                                                                                                      |                           |     |   |

|        | nen a new block is brought into the the next 7 bits determine which | cache                                                                                                               |                           |     |   |

|         | on all three segm               |                         |                                                               | •                          | in Pipel  | ine Example            | =                    |         |     |   |

|---------|---------------------------------|-------------------------|---------------------------------------------------------------|----------------------------|-----------|------------------------|----------------------|---------|-----|---|

|         | Clock<br>Pulse<br>Number        | Segment 1               |                                                               | Segment 2                  |           | Segment 3              |                      |         |     |   |

|         |                                 | R1                      | R2                                                            | R3                         | R4        | <b>R</b> 5             | _                    |         |     |   |

|         | 1                               | $A_1$                   | $\boldsymbol{B}_1$                                            | _                          | _         | _                      | _                    |         |     |   |

|         | 2                               | $A_2$                   | $B_2$                                                         | $A_1 * B_1$                | $C_1$     |                        |                      |         |     |   |

|         | 3<br>4<br>5<br>6<br>7<br>8<br>9 | $A_3$                   | $B_3$                                                         | $A_2 * B_2$                |           | $A_1 * B_1 + C_1$      |                      |         |     |   |

|         |                                 | $A_4$ $A_5$ $A_6$ $A_7$ | B <sub>4</sub> B <sub>5</sub> B <sub>6</sub> B <sub>7</sub> — | $A_3 * B_3$<br>$A_4 * B_4$ |           |                        |                      |         |     |   |

|         |                                 |                         |                                                               | $A_5 * B_5$                |           | $A_4*B_4+C_4$          |                      |         |     |   |

|         |                                 |                         |                                                               | $A_6 * B_6$ $A_7 * B_7$    | $C_6$     | $A_5*B_5+C_5$          | + C <sub>5</sub>     |         |     |   |

|         |                                 | _                       |                                                               |                            |           | $A_6 * B_6 + C_6$      |                      |         |     |   |

|         |                                 | _                       |                                                               | _                          |           | $A_7*B_7+C_7$          |                      |         |     |   |

| •       | It places A1 and                | R1 into                 | P1 and                                                        | P2 transfer                | s the pro | oduct of R1 and R2     | into P3 transfers    |         |     |   |

|         | C, into R4, and p               |                         |                                                               |                            |           |                        | into K3, transfers   |         |     |   |

| •       | _                               |                         |                                                               |                            |           | ieve the first outpu   | t from R5.           |         |     |   |

| •       |                                 | _                       |                                                               |                            |           | moves the data or      |                      |         |     |   |

|         | pipeline.                       |                         | 1                                                             |                            | 1         |                        | 1                    |         |     |   |

| •       | This happens as                 | long as 1               | new inp                                                       | ut data flow               | into the  | system. When no n      | nore input data are  |         |     |   |

|         |                                 |                         |                                                               |                            |           | erges out of the pipel |                      |         |     |   |

| Calcul  | ate the Speedup                 | ratio of                | non p                                                         | ipeline to p               | pipeline  | e, if $t_p=20$ ns, no  | of tasks, $n = 100$  | , 10    | CO5 | I |

| and no  | of segments, k=                 | 4.                      |                                                               |                            |           | -                      |                      |         |     |   |

| •       | the time it takes               | to proce                | ss a sub                                                      | -operation in              | each se   | egment be equal to     | tp = 20  ns.         |         |     |   |

| •       | K=4, n=100 task                 | S,                      |                                                               |                            |           |                        |                      |         |     |   |

| •       | Pipeline= $(k + n)$             | - 1)*tp=                | (4+99)*                                                       | 20=2060 ns                 |           |                        |                      |         |     |   |

| •       | If tn=ktp=4*20=                 | 80 ns                   |                                                               |                            |           |                        |                      |         |     |   |

| •       | Non pipeline=n*                 | ktp=100                 | *80=80                                                        | 00 ns.                     |           |                        |                      |         |     |   |

| •       | Speedup ratio=8                 | 000/206                 | 0=3.88                                                        |                            |           |                        |                      |         |     |   |

| In deta | il describe Arith               |                         |                                                               |                            |           |                        |                      | 10(exa  | CO5 | Ι |

| •       |                                 | _                       | _                                                             |                            | very hi   | gh speed computer      | ·s.                  | mple-   |     |   |

| •       | _                               |                         |                                                               | -                          | -         | s, multiplication of   |                      | 3,diagr |     |   |

|         | numbers, and sir                | nilar cor               | nputatio                                                      | ns encounte                | red in so | cientific problems.    | -                    | am-     |     |   |

| •       | Example:-The in                 | puts to t               | he float                                                      | ing-point ad               | der pipe  | line are two norma     | lized floating-poin  | 4,expl  |     |   |

|         | binary numbers.                 |                         |                                                               |                            |           |                        |                      | n-3)    |     |   |

| •       | $X = A X 2^a$                   |                         |                                                               |                            |           |                        |                      |         |     |   |

| •       | $Y = B X 2^b$                   |                         |                                                               |                            |           |                        |                      |         |     |   |

| A and B | are two fractions th            | at represe              | nt the m                                                      | antissas and a             | and b ar  | e the exponents.       |                      |         |     |   |

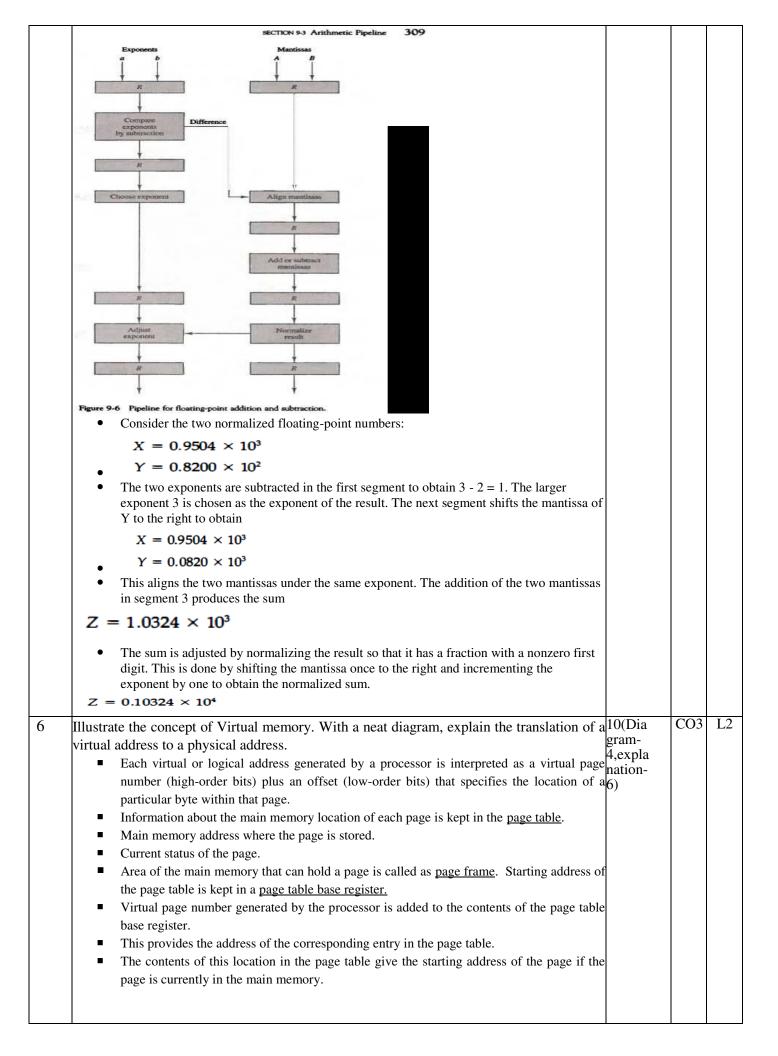

| •       | The floating-point in Fig. 9-6. | nt additi               | on and s                                                      | subtraction c              | an be pe  | erformed in four se    | gments, as shown     |         |     |   |

| •       | -                               |                         |                                                               |                            |           |                        | nediate results. The |         |     |   |

| •       | 1. Compare the                  | _                       |                                                               |                            | -         |                        |                      |         |     |   |

| •       | 2. Align the man                | _                       |                                                               |                            |           |                        |                      |         |     |   |

| •       | 3. Add or subtract              |                         | intissas.                                                     |                            |           |                        |                      |         |     |   |

| _       | 4. Normalize the                |                         |                                                               |                            |           |                        |                      |         |     | 1 |

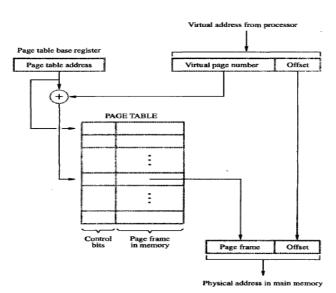

Figure 5.27 Virtual-memory address translation.

- Page table entry for a page also includes some control bits which describe the status of the page while it is in the main memory.

- One bit indicates the validity of the page.

- Indicates whether the page is actually loaded into the main memory.

- Allows the operating system to invalidate the page without actually removing it.

- One bit indicates whether the page has been modified during its residency in the main memory.

- This bit determines whether the page should be written back to the disk when it is removed from the main memory.

- Similar to the dirty or modified bit in case of cache memory.

- Other control bits for various other types of restrictions that may be imposed.

- For example, a program may only have read permission for a page, but not write or modify permissions.

Faculty Signature CCI Signature HOD Signature