| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

# Internal Assessment Test 3 – February 2023

| Sub:  | Computer O     | rganization    | and Archite  | ecture          |        | Sub Code:    | 21CS34           | Bra   | nch: | CSE  |    |     |

|-------|----------------|----------------|--------------|-----------------|--------|--------------|------------------|-------|------|------|----|-----|

| Date: | 09/02/23       | Duration:      | 90 minutes   | Max Marks:      | 50     | Sem / Sec:   | III / A          | A, B, | С    |      | OH | BE  |

|       |                |                | •            | VE FULL Questi  | ons    |              |                  |       | MA   | ARKS | CO | RBT |

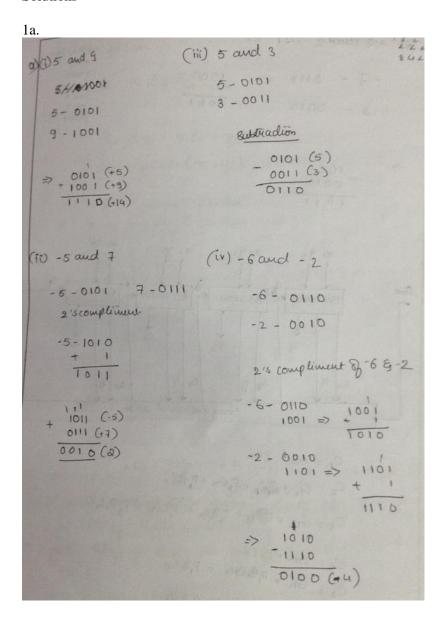

|       | (a) Perform A  |                |              |                 |        |              |                  |       |      |      |    |     |

|       | (i)            |                |              |                 |        |              |                  |       |      |      |    |     |

|       | (ii)           | -5 and 7       |              |                 |        |              |                  |       |      |      |    |     |

|       | Perform S      | ubtraction ı   |              |                 | [:     | 5]           | 4                | L2    |      |      |    |     |

| 1     | (iii)          | 5 and 3        |              |                 |        |              |                  |       |      |      |    |     |

| 1     | (iv)           | -6 and -2      |              |                 |        |              |                  |       |      |      |    |     |

|       | (v)            | -7 and 2       |              |                 |        |              |                  |       |      |      |    |     |

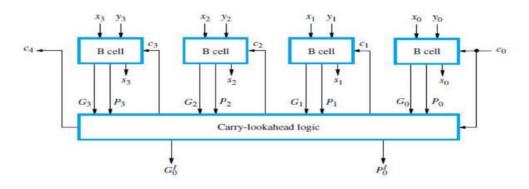

|       | (b) Explain4 b | oit Carry Lo   | ok Ahead A   | Adder with nea  | at dia | ıgram        |                  |       | [:   | 5]   | 4  | L2  |

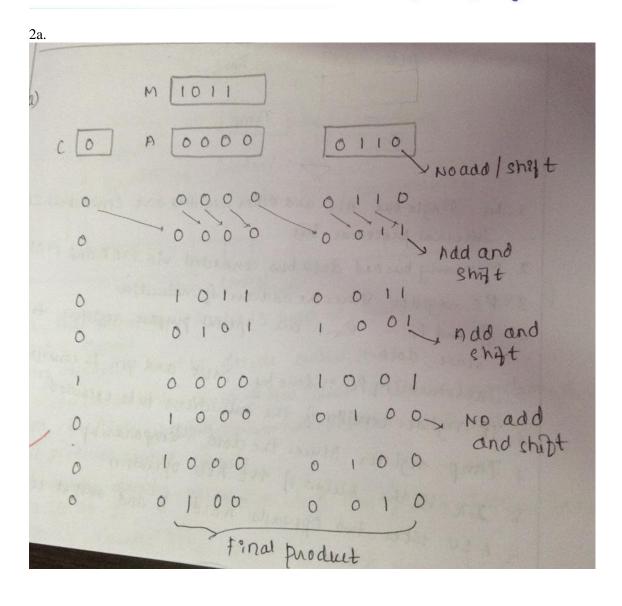

|       | (a) Multiply 1 | 1 and 6 usi    | ng Sequenti  | al Multiplicati | ion    |              |                  |       | [    | 5]   | 4  | L2  |

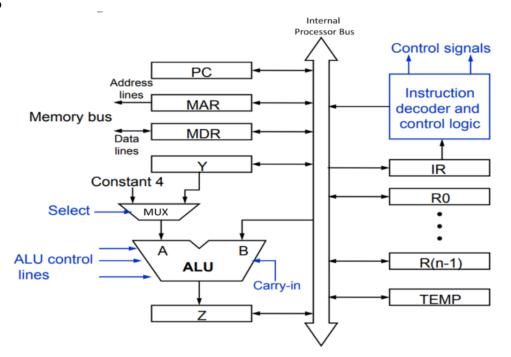

| 2     | (b) Discuss w  | ith post dis   | gram the si  | nala bus orga   | nizot  | ion of the c | loto poth incid  | do 0  |      |      |    |     |

|       | ` ′            | itii ileat uia | grain the si | ligie dus diga  | ınzaı  | ion of the c | iata patii iiist | ae a  | ſ    | [5]  | 4  | L2  |

|       | processor      |                |              |                 |        |              |                  |       | L    | .01  | '  | 132 |

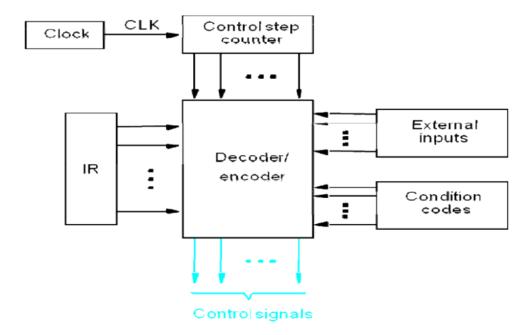

| 3     | (a) Explain i  |                | [            | [5]             | 4      | L1           |                  |       |      |      |    |     |

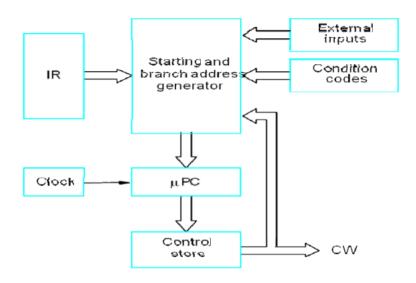

| 3     | (b) Explain tl | unit.          |              | [5]             |        | 4            | L1               |       |      |      |    |     |

| CI | CCI | НоГ |

|----|-----|-----|

|    |     |     |

| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

# Internal Assessment Test 3 – February 2023

| Sub:  | Computer O                                                               | rganization  | and Archite  |                 | Sub Code: | 21CS34       | Bra             | nch:  | CSE |     |    |    |

|-------|--------------------------------------------------------------------------|--------------|--------------|-----------------|-----------|--------------|-----------------|-------|-----|-----|----|----|

| Date: | 09/02/23                                                                 | Duration:    | 90 minutes   | Max Marks:      | 50        | Sem / Sec:   | III / A         | A, B, | С   |     | OI | BE |

|       |                                                                          |              | MA           | RKS             | CO        | RBT          |                 |       |     |     |    |    |

|       | (b) Perform A                                                            |              |              |                 |           |              |                 |       |     |     |    |    |

|       | (vi)                                                                     | 5 and 9      |              |                 |           |              |                 |       |     |     |    |    |

|       | (vii)                                                                    |              |              |                 |           |              |                 |       |     |     |    |    |

|       |                                                                          |              | using 2's Co | ompliment       |           |              |                 |       |     | [5] | 4  | L2 |

| 1     | (viii)                                                                   | 5 and 3      |              |                 |           |              |                 |       |     |     |    |    |

|       | (ix)                                                                     | -6 and -2    |              |                 |           |              |                 |       |     |     |    |    |

|       | (x)                                                                      | -7 and 2     |              |                 |           |              |                 |       |     |     |    |    |

|       | (b) Explain4 b                                                           | oit Carry Lo | ook Ahead A  | Adder with nea  | at dia    | ıgram        |                 |       | [5  | 5]  | 4  | L2 |

|       | (a) Multiply 1                                                           | 1 and 6 uci  | na Seguenti  | al Multiplicati | ion       |              |                 |       |     |     |    |    |

|       | (a) Munipiy 1                                                            | 1 and 0 usi. | ng bequenti  | ai wianipiican  | 1011      |              |                 |       | Ľ   | 5]  | 4  | L2 |

| 2     | (b) Discuss w                                                            | ith neat dia | gram the si  | ngle bus orga   | nizat     | ion of the c | lata path insid | de a  |     |     |    |    |

|       | processor                                                                |              |              |                 |           |              | -               |       | [:  | 5]  | 4  | L2 |

|       |                                                                          |              |              |                 |           |              |                 |       |     |     |    |    |

|       | (a) Explain i                                                            |              | [:           | 5]              | 4         | L1           |                 |       |     |     |    |    |

| 3     | 3 (b) Explain the basic organization of a Micro Programmed Control unit. |              |              |                 |           |              |                 |       |     |     | 4  | L1 |

|   | (a) Explain in de Classificatio                                                                                     |                                                                                                                                                                                                                                                                                                                                                         | l abo  | out P | arall | lel P | roce  | ssin | g. A  | lso r    | nent  | ion a | abou   | t the | Fly      | nn's  | [5] | 5  | L1 |

|---|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-------|-------|-------|------|-------|----------|-------|-------|--------|-------|----------|-------|-----|----|----|

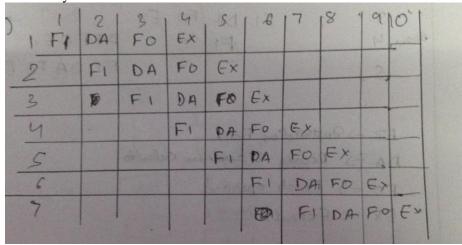

| 4 | (b) Consider the                                                                                                    |                                                                                                                                                                                                                                                                                                                                                         | low    | ing F | Pipel | ine a | and a | answ | er tl | ne qu    | ıesti | ons   | belo   | w.    |          |       |     |    |    |

|   | Step: 1 2 3 4 5 6 7 8 9 10 11 12 13                                                                                 |                                                                                                                                                                                                                                                                                                                                                         |        |       |       |       |       |      |       |          |       |       |        |       |          |       |     |    |    |

|   | Instruction:                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                       | FI     | DA    | FO    | EX    |       |      |       |          |       |       |        |       |          |       |     |    |    |

|   |                                                                                                                     | 2                                                                                                                                                                                                                                                                                                                                                       |        | FI    | DA    | FO    | EX    |      |       | $\Box$   |       |       |        |       |          |       |     |    |    |

|   | (Branch)                                                                                                            | 3                                                                                                                                                                                                                                                                                                                                                       |        |       | FI    | DA    | FO    | EX   |       |          |       |       |        |       |          |       |     |    |    |

|   |                                                                                                                     | 4                                                                                                                                                                                                                                                                                                                                                       |        |       |       | FI    | -     | -    | FI    | DA       | FO    | EX    |        |       |          |       |     |    |    |

|   |                                                                                                                     | 5                                                                                                                                                                                                                                                                                                                                                       |        |       |       |       | -     | -    | -     | FI       | DA    | FO    | EX     |       |          |       | [5] | 5  | L3 |

|   |                                                                                                                     | 6                                                                                                                                                                                                                                                                                                                                                       |        | _     |       | -     |       |      |       | $\vdash$ | FI    | DA    | FO     | EX    |          |       | [3] | 3  | L3 |

|   |                                                                                                                     | 7                                                                                                                                                                                                                                                                                                                                                       |        |       |       |       |       |      |       |          |       | FI    | DA     | FO    | EX       |       |     |    |    |

|   | (ii) How many<br>(iii) Redraw the                                                                                   | <ul> <li>(i) How many stage pipeline dose the diagram depict? (1)</li> <li>(ii) How many clock cycles does it take to complete the 7 instructions? (1)</li> <li>(iii) Redraw the timing diagram after removing the branch instruction. (2)</li> <li>(iv) How many clock cycles does it take to the instructions after branch is removed? (1)</li> </ul> |        |       |       |       |       |      |       |          |       |       |        |       | ved? (1) |       |     |    |    |

| 5 | (a) How many su<br>same in deta                                                                                     |                                                                                                                                                                                                                                                                                                                                                         | pera   | tion  | s car | an .  | Aritl | hmet | ic P  | ipeli    | ne b  | e div | ided   | . Ex  | plaiı    | n the | [5] | 5  | L1 |

|   | (b) With neat fig<br>Pipeline.                                                                                      | gure                                                                                                                                                                                                                                                                                                                                                    | , illu | ıstra | te th | e foi | ır se | gme  | nt o  | pera     | tions | of t  | the I  | nstru | ictio    | n     | [5] | 5  | L2 |

| 6 | (a) Elucidate Vector Processing. Also explain how Memory Interleaving impacts the performance of vector processing. |                                                                                                                                                                                                                                                                                                                                                         |        |       |       |       |       |      |       |          |       |       | npacts | [5]   | 5        | L2    |     |    |    |

|   | (i) Attached                                                                                                        | the performance of vector processing.  (b) Explain the following  (i) Attached Array Processor  (ii) SIMD Array Processor                                                                                                                                                                                                                               |        |       |       |       |       |      |       |          |       |       |        |       |          | [5]   | 5   | L1 |    |

|   | (a) Explain in detail about Parallel Processing. Also mention about the Flynn's Classification |      |          |          |       |       |       |      |       |          |        |        |       | [5]    | 5     | L1       |     |   |    |

|---|------------------------------------------------------------------------------------------------|------|----------|----------|-------|-------|-------|------|-------|----------|--------|--------|-------|--------|-------|----------|-----|---|----|

| 4 | Classification.  (b) Consider the following Pipeline and answer the questions below.           |      |          |          |       |       |       |      |       |          |        |        |       |        |       |          |     |   |    |

| 4 | (b) Consider the                                                                               | fol  | low      | ing F    | Pipel | ine a | and a | answ | er tl | ne qu    | ıesti  | ons    | belo  | w.     |       |          |     |   |    |

|   | Step:   1   2   3   4   5   6   7   8   9   10   11   12   13                                  |      |          |          |       |       |       |      |       |          |        |        |       |        | [5]   | 5        | L3  |   |    |

|   | Instruction:                                                                                   | 1    | FI       | DA       | FO    | EX    |       |      |       |          |        |        |       |        |       |          |     |   |    |

|   | Tibli dellott.                                                                                 | 2    |          | FI       | DA    | FO    | EX    | -    |       | $\vdash$ |        |        |       | _      |       | 1        |     |   |    |

|   | (71)                                                                                           |      |          | FI       | _     |       |       | EV   |       | -        | _      | _      |       |        |       | 1        |     |   |    |

|   | (Branch)                                                                                       | 3    | -        |          | FI    | DA    | FO    | EX   |       |          |        |        | -     |        |       | {        |     |   |    |

|   |                                                                                                | 4    |          | <u> </u> |       | FI    | -     |      | FI    | DA       | FO     | EX     |       |        |       | -        |     |   |    |

|   |                                                                                                | 5    | <u> </u> | L.       |       |       | -     | -    | -     | FI       | DA     | FO     | EX    |        |       |          |     |   |    |

|   |                                                                                                | 6    |          |          |       |       |       |      |       |          | FI     | DA     | FO    | EX     |       | ]        |     |   |    |

|   |                                                                                                | 7    |          |          |       |       |       |      |       |          |        | FI     | DA    | FO     | EX    |          |     |   |    |

|   | (i) How many                                                                                   | stag | ge pi    | pelin    | e do  | se th | e dia | gran | ı dep | ict?     | (1)    |        |       |        |       |          |     |   |    |

|   | (ii) How many                                                                                  | clo  | ck cy    | ycles    | does  | it ta | ke to | con  | nplet | e the    | 7 in   | struc  | tions | ? (1)  | )     |          |     |   |    |

|   | (iii) Redraw the                                                                               |      |          |          |       |       |       |      |       |          |        |        |       |        |       |          |     |   |    |

|   | (iv) How many                                                                                  | clo  | ck cy    | ycles    | does  | it ta | ke to | the  | instr | uctio    | ons at | fter t | oranc | h is 1 | emo   | ved? (1) |     |   |    |

|   | (a) How many su                                                                                | ub o | pera     | ation    | s car | n an  | Aritl | hmet | ic P  | ipeli    | ne b   | e div  | ided  | . Ex   | plaiı | n the    | [5] | 5 | L1 |

| 5 | same in deta                                                                                   |      | 1        |          |       |       |       |      |       | 1        |        |        |       |        |       |          |     |   |    |

|   | (b) With neat fig                                                                              | gure | , illı   | ıstra    | te th | e foi | ır se | gme  | nt o  | pera     | tions  | of t   | he I  | nstru  | ictio | n        | [5] | 5 | L2 |

|   | Pipeline.                                                                                      |      |          |          |       |       |       |      |       |          |        |        |       |        |       |          |     |   |    |

| 6 | (b) Elucidate Ve                                                                               |      |          |          |       |       |       |      | hov   | v Me     | emoi   | ry In  | terle | avin   | g in  | npacts   | [5] | 5 | L2 |

|   | the performa                                                                                   |      |          |          | r pro | cess  | sing. |      |       |          |        |        |       |        |       |          | [-] |   |    |

|   | (c) Explain the f                                                                              |      |          | _        |       |       |       |      |       |          |        |        |       |        |       |          |     |   |    |

|   | (i) Attached Array Processor (ii) SIMD Array Processor                                         |      |          |          |       |       |       |      |       |          |        |        | [5]   | 5      | L1    |          |     |   |    |

|   | (II) SIMD A                                                                                    | пау  | PIO      | cess     | Οľ    |       |       |      |       |          |        |        |       |        |       |          | 1   |   |    |

# **CO PO Mapping**

|     | Course Outcomes                                                                                      | Modules | P01 | P02 | P03 | P04 | PO5 | 90d | PO7 | P08 | PO9 | PO10 | P011 | PO12 | PSO1 | PSO2 | PSO3 | PSO4 |

|-----|------------------------------------------------------------------------------------------------------|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|

| CO1 | Explain the organization and architecture of computer systems with machine instructions and programs | 1       | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    | -    | -    |

| CO2 | Analyze the input/output devices communicating with computer system                                  | 2       | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | 2    | -    | -    | -    |

| CO3 | Demonstrate the functions of different types of memory devices                                       | 3       | 2   | 2   | 2   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 2    | -    | -    |

| CO4 | Apply different data types on simple arithmetic and logical unit                                     | 4       | 3   | -   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 2    | -    | -    |

| CO5 | Analyze the functions of basic processing unit, Parallel processing and pipelining                   | 5       | 3   | 2   | 3   | 2   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 2    | -    | -    |

| COGNITIVE<br>LEVEL | REVISED BLOOMS TAXONOMY KEYWORDS                                                                                                              |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| L1                 | List, define, tell, describe, identify, show, label, collect, examine, tabulate, quote, name, who, when, where, etc.                          |

| L2                 | summarize, describe, interpret, contrast, predict, associate, distinguish, estimate, differentiate, discuss, extend                           |

| L3                 | Apply, demonstrate, calculate, complete, illustrate, show, solve, examine, modify, relate, change, classify, experiment, discover.            |

| L4                 | Analyze, separate, order, explain, connect, classify, arrange, divide, compare, select, explain, infer.                                       |

| L5                 | Assess, decide, rank, grade, test, measure, recommend, convince, select, judge, explain, discriminate, support, conclude, compare, summarize. |

| PF   | ROGRAM OUTCOMES (PO), PRO                                                                    | GRAM       | SPECIFIC OUTCOMES (PSO)               | С          | ORRELATION<br>LEVELS |  |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------|------------|---------------------------------------|------------|----------------------|--|--|--|--|--|--|--|

| PO1  | Engineering knowledge                                                                        | PO7        | Environment and sustainability        | 0          | No Correlation       |  |  |  |  |  |  |  |

| PO2  | Problem analysis                                                                             | Ethics     | 1                                     | Slight/Low |                      |  |  |  |  |  |  |  |

| PO3  | Design/development of solutions                                                              | PO9        | Individual and team work              | 2          | Moderate/<br>Medium  |  |  |  |  |  |  |  |

| PO4  | Conduct investigations of complex problems                                                   | PO10       | Communication                         | 3          | Substantial/<br>High |  |  |  |  |  |  |  |

| PO5  | Modern tool usage                                                                            | PO11       | Project management and finance        |            |                      |  |  |  |  |  |  |  |

| PO6  | The Engineer and society                                                                     | PO12       | Life-long learning                    |            |                      |  |  |  |  |  |  |  |

| PSO1 | Develop applications using differe                                                           | nt stacks  | of web and programming technologic    | es         |                      |  |  |  |  |  |  |  |

| PSO2 | Design and develop secure, paralle                                                           | el, distri | buted, networked, and digital systems |            |                      |  |  |  |  |  |  |  |

| PSO3 | SO3 Apply software engineering methods to design, develop, test and manage software systems. |            |                                       |            |                      |  |  |  |  |  |  |  |

| PSO4 | PSO4 Develop intelligent applications for business and industry                              |            |                                       |            |                      |  |  |  |  |  |  |  |

## Internal Assessment Test 3 – February 2023

| Sub:  | Computer O | rganization | and Archite | ecture     | Sub Code: | 21CS34     | Branch: | CSE     |  |     |

|-------|------------|-------------|-------------|------------|-----------|------------|---------|---------|--|-----|

| Date: | 09/02/23   | Duration:   | 90 minutes  | Max Marks: | 50        | Sem / Sec: | III /   | A, B, C |  | OBE |

#### Solutions

The diagram of a carry look ahead adder is as shown above,

In ripple casey adders, the casery propagation time is the major speed limiting factor. Most other asithmetic operations like multiplication and division are implemented using several add/subtract steps, Thus, improving the speed of addition will improve the speed of all other asithmetic operations.

Carry-lookahead adder improves the speed by reducing carry propagation aday. It calculates the carry signals in advance; based on input signals instead of waiting for them to ripple through the address.

ALU and all the registers are interconnected via a single common bus.

- ☐ The data and address lines of the external memory bus connected to the internal processor bus via the memory data register, MDR, and the memory addressregister, MAR respectively.

- ☐ Register MDR has two inputs and two outputs.

- $\Box$  Data may be loaded into MDR either from the memory bus or from the internal processor bus.

- ☐ The data stored in MDR may be placed on either bus.

- $\Box$  The input of MAR is connected to the internal bus, and its output is connected to the external bus.

- $\Box$  The control lines of the memory bus are connected to the instruction decoder and control logic.

- ☐ This unit is responsible for issuing the signals that control the operation of all the units inside the processor and for increasing with the memory bus.

- $\ \square$  The MUX selects either the output of register Y or a constant value 4 to be provided as input A of the ALU.

- ☐ The constant 4 is used to increment the contents of the program counter.

#### 3a.

#### Hardwired Control

- $\Box$  To execute instructions, the processor must have some means of generating the control signals needed in the proper sequence.

- ☐ Two categories: hardwired control and micro programmed control

- ☐ Hardwired system can operate at high speed; but with little flexibility.

### **Control Unit Organization**

3b

### Microinstructions

- $\square$  A straightforward way to structure microinstructions is to assign one bit position to each control signal.

- $\square$  However, this is very inefficient.

- $\Box$  The length can be reduced: most signals are not needed simultaneously, and many signals are mutually exclusive.

- ☐ All mutually exclusive signals are placed in the same group in binary coding.

.....

There are a variety of ways that parallel processing can be classified. It can be considered from the internal organization of the processors, from the interconnection structure between processors, or from the flow of information through the system. One classification introduced by M. J. Flynn considers the organization of a computer system by the number of instructions and data items that are manipulated simultaneously. The normal operation of a computer is to fetch instructions from memory and execute them in the processor. The sequence of instructions read from memory constitutes an *instruction stream*. The operations performed on the data in the processor constitutes a *data stream*. Parallel processing may occur in the instruction stream, in the data stream, or in both. Flynn's classification divides computers into four major groups as follows:

Single instruction stream, single data stream (SISD)

Single instruction stream, multiple data stream (SIMD)

Multiple instruction stream, single data stream (MISD)

Multiple instruction stream, multiple data stream (MIMD)

4b.

- i. 4 stage

- ii. 13 Clock cycles

- iii. Diagram shown below

- iv. 10 clocl cycles

\_

v.

An arithmetic pipeline divides an arithmetic operation into suboperations for execution in the pipeline segment

- ☐ Pipeline arithmetic units are usually found in very high speed computers.

- ☐ They are used to implement floating-point operations, multiplication of fixed-point ☐ numbers, and similar computations are out to produce the scientific problems.

- □ numbers, and similar computations encountered in scientific problems.

- ☐ A pipeline multiplier is essentially an array multiplier as described in Fig. (Next slide)

- ☐ With special adders designed to minimize the carry propagation time through ☐ the partial products.

- ☐ Floating-point operations are easily decomposed into suboperations

5b.

Instruction Cycle 1) Fetch the instruction from memory 2) Decode the instruction 3) Calculate the effective address 4) Fetch the operands from memory 5) Execute the instruction 6) Store the result in the proper place

Example: Four-segment Instruction Pipeline Four-segment CPU pipeline:

» 1) FI: Instruction Fetch »

2) DA: Decode Instruction & calculate EA

» 3) FO : Operand Fetch» 4) EX : Execution

6a. Many scientific problems require arithmetic operations on large arrays of numbers. These numbers are usually formulated as vectors and matrices of floating-point numbers. v A vector is an ordered set of a one-dimensional array of data items. A vector V of length v is represented as a row vector by  $V = [V1\ V2\ V, \cdots V.]$ . It may be represented as a column vector if the data items are listed in a column. v A conventional sequential computer is capable of processing operands one at a time. Consequently, operations on vectors must be broken down into single computations with subscripted variables v consider the bfollowing Fortran DO loop:

DO

$$20I = 1$$

,  $100$

$20C(I) = B(I) + A(I)$

This is a program for adding two vectors A and B of length 100 to produce a  $\nu$  vector C This is implemented in machine language by the following sequence of operations.

InitializeI=0

20 R e a d A ( I )

R e a d B ( I )

S t o r e C (I) = A (I) + B (I)

I n c r e m e n t I = I + 1

If I< 100 Goto 20

The loop control variable is then vupdated and the steps repeat 100 times. v A computer capable of vector processing eliminates the overhead associated with the time it takes to fetch and execute the instructions in the program loop. v It allows operations to be specified with a single vector instruction of the form C(1:100) = A(1:100) + B(1:100)

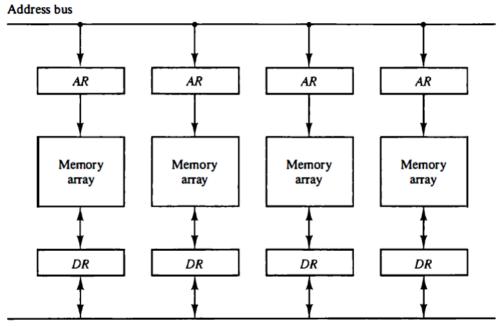

Pipeline and vector processors often require simultaneous access to memory from two or more sources  $\nu$  the memory can be partitioned into a number of modules connected to a common memory address and data buses. A memory module is a memory array together with its own address and data registers. Figure below

Data bus

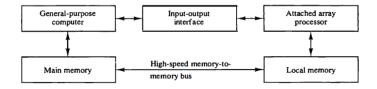

- 6b. An array processor is a processor that performs computations on large arrays of data. The term is used to refer to two different types of processors.

- An attached array processor is an auxiliary processor attached to a generalpurpose computer.

- It is intended to improve the performance of the host computer in specific numerical computation tasks.

- An SIMD array processor is a processor that has a single-instruction multiple-data organization Attached Array Processor

- An attached array processor is designed as a peripheral for a conventional host computer, and its purpose is to enhance the performance of the computer by providing vector processing for complex scientific applications

- It achieves high performance by means of parallel processing with multiple functional units.

- It includes an arithmetic unit containing one or more pipelined floating point adders and multipliers. The array processor can be programmed by the user to accommodate a variety of complex arithmetic problems

- Figure shows the interconnection of an attached array processor to a host computer.