| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

## Internal Assessment Test 1 – Dec 2022

|       |                                                                                                                                                     |                                                                                                                              | Interna                                                                                                                          | Assessment Tes                                                                                                                                                                                                         | st 1 – Dec 2                                                                                                                | 2022                                                                                     |                  |      |          |     |                |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|------|----------|-----|----------------|--|

| Sub:  | Analog and I                                                                                                                                        | Digital Electi                                                                                                               | ronics                                                                                                                           |                                                                                                                                                                                                                        | Sub<br>Code:                                                                                                                | 21CS33                                                                                   | Bran             | nch: | CSE      | ,   |                |  |

| Date: | 8/2/23                                                                                                                                              | Duration:                                                                                                                    | 90 mins                                                                                                                          | Max<br>Marks: 50                                                                                                                                                                                                       | Sem /<br>Sec:                                                                                                               | 3 <sup>rd</sup> seme                                                                     | ester/A          | , В, | С        | 0   | BE             |  |

|       |                                                                                                                                                     | <u>An</u>                                                                                                                    | swer any FI                                                                                                                      | VE FULL Question                                                                                                                                                                                                       | <u>s</u>                                                                                                                    |                                                                                          |                  |      | ARK<br>S | CO  | RBT            |  |

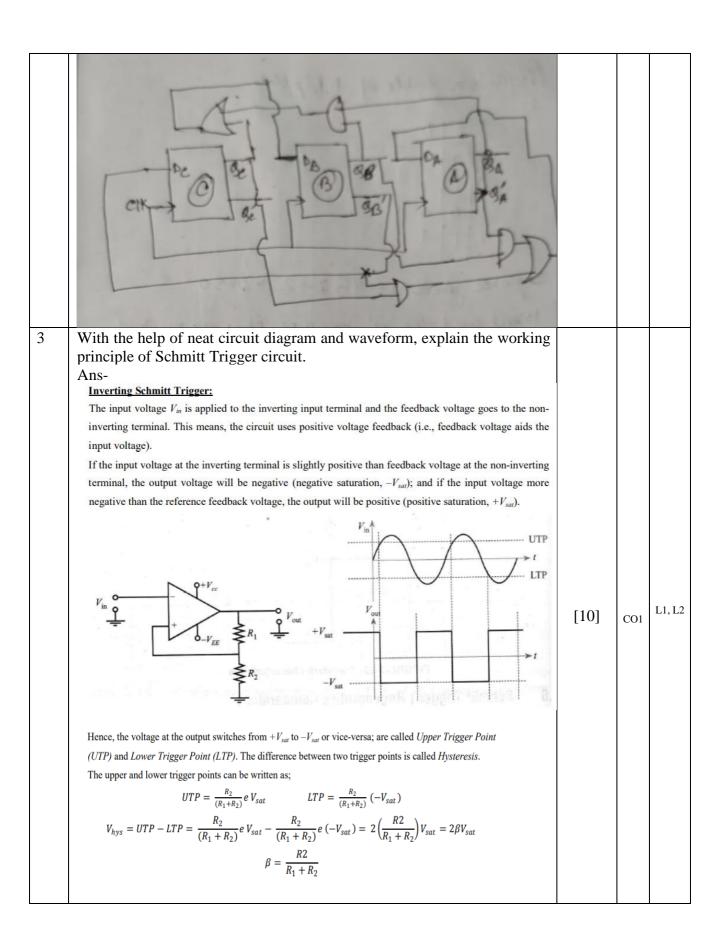

|       | Ans- PISO v<br>In load mode<br>data in each<br>the data seria<br>b) Design Pa                                                                       | works in twe we have of the flip ally from our arallel in so SO shift re                                                     | vo modes of<br>the paralled<br>flop simulation<br>one flip flot<br>erial out sh                                                  | nift/Load signal is one is load and a cl input of the da ltaneously. And op to the next one nift register. Exuit diagram is shown                                                                                      | nother is sl<br>ta in which<br>shift signal<br>e.                                                                           | nift mode.<br>we load th<br>helps shift                                                  |                  | [2+  | -6+2]    |     |                |  |

|       | <u>A</u> 1                                                                                                                                          | D <sub>A</sub>                                                                                                               | 9 G1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                         | G5 G2 G                                                                                                                                                                                                                | 5 (3)<br>1<br>1                                                                                                             | QD Serial Data<br>O/P                                                                    |                  |      |          | CO4 | L1, L2<br>, L3 |  |

|       | diagram sho<br>however the<br>PISO shift re<br>shift register<br>from the shift<br>cycle. Here,<br>pulses are re<br>In this parall<br>gates are use | wn. The C<br>i/p data is<br>egister circ<br>is from DA<br>ft register<br>one CLK<br>quired to u<br>el input se<br>ed. One co | LK i/p sig<br>individua<br>cuit, the inp<br>to DD at<br>serially 1-l<br>pulse is en<br>unload all<br>crial outpur<br>ontrol sign | FFs which are conal is connected to lly connected to put data is applied the same time. It is a time from lough to load the the four bits. It (PISO) shift regal (Shift/Load) is after that, NOT general is connected. | directly to<br>every flip to<br>d to the inp<br>After that, a<br>input pine<br>4-bit of da<br>gister circus<br>s used to co | all the FFs flop. Out pins of it is read out on every that but four it, logic ontrol the | the<br>at<br>CLK |      |          |     |                |  |

| to 'G1', 'G2', and 'G3', and the other inputs of G1, G2 & G3 are B, C & D. Here, 'A' is directly connected to DA of the first flip flop.  The direct control signal is connected to one input of the 'G4', 'G5' & 'G6' and one more input of the 'G4', 'G5' & 'G6' are connected to the outputs of Flip Flops like QA, QB, and QC. The OR gate is connected to the second, third, and fourth Flip Flop's inputs like DB, DC, and DD. All the flip flops are to be connected in a single CLK pulse and the FFs outputs will be in the serial data output.  Here, we are choosing the input data as 1101 then A=1, B=1, C=0 & D=1.  When the control signal applied to NOT gate is '0' then its o/p will become'1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and 7clock pulses are required to transfer the data to an output register |   | 4. (C1) (C2)1(C2)1441 (C1 C2                                |      | 1   |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------------------------------------------------------------------------------------------------|------|-----|--------|

| The direct control signal is connected to one input of the 'G4', 'G5' & 'G6' and one more input of the 'G4', 'G5' & 'G6' are connected to the outputs of Flip Flops like QA, QB, and QC. The OR gate is connected to the second, third, and fourth Flip Flop's inputs like DB, DC, and DD. All the flip flops are to be connected in a single CLK pulse and the FFs outputs will be in the serial data output.  Here, we are choosing the input data as 1101 then A=1, B=1, C=0 & D=1.  When the control signal applied to NOT gate is '0' then its o/p will become '1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                |   |                                                                                                 |      |     |        |

| and one more input of the 'G4', 'G5' & 'G6' are connected to the outputs of Flip Flops like QA, QB, and QC. The OR gate is connected to the second, third, and fourth Flip Flop's inputs like DB, DC, and DD. All the flip flops are to be connected in a single CLK pulse and the FFs outputs will be in the serial data output.  Here, we are choosing the input data as 1101 then A=1, B=1, C=0 & D=1. When the control signal applied to NOT gate is '0' then its o/p will become'1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                               |   |                                                                                                 |      |     |        |

| of Flip Flops like QA, QB, and QC. The OR gate is connected to the second, third, and fourth Flip Flop's inputs like DB, DC, and DD. All the flip flops are to be connected in a single CLK pulse and the FFs outputs will be in the serial data output.  Here, we are choosing the input data as 1101 then A=1, B=1, C=0 & D=1. When the control signal applied to NOT gate is '0' then its o/p will become '1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                       |   |                                                                                                 |      |     |        |

| second, third, and fourth Flip Flop's inputs like DB, DC, and DD. All the flip flops are to be connected in a single CLK pulse and the FFs outputs will be in the serial data output.  Here, we are choosing the input data as 1101 then A=1, B=1, C=0 & D=1. When the control signal applied to NOT gate is '0' then its o/p will become'1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |                                                                                                 |      |     |        |

| flip flops are to be connected in a single CLK pulse and the FFs outputs will be in the serial data output.  Here, we are choosing the input data as 1101 then A=1, B=1, C=0 & D=1. When the control signal applied to NOT gate is '0' then its o/p will become'1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                                                                 |      |     |        |

| will be in the serial data output.  Here, we are choosing the input data as 1101 then A=1, B=1, C=0 & D=1.  When the control signal applied to NOT gate is '0' then its o/p will become'1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                                                                 |      |     |        |

| Here, we are choosing the input data as 1101 then A=1, B=1, C=0 & D=1. When the control signal applied to NOT gate is '0' then its o/p will become '1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                                                                                                 |      |     |        |

| When the control signal applied to NOT gate is '0' then its o/p will become '1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | ±                                                                                               |      |     |        |

| become'1' and 'G1, 'G2' & 'G3' will enable, and 'G4', 'G5' & 'G6' will disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                                                                                                 |      |     |        |

| disable. So, all the inputs are loaded and after that OR gates are also enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                                                                 |      |     |        |

| enabled and the data is to be loaded to the input of each Flip Flop.  Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                                                                 |      |     |        |

| Now we are applying the control signal '1 to NOT gate then the output of this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | •                                                                                               |      |     |        |

| this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | enabled and the data is to be loaded to the input of each Flip Flop.                            |      |     |        |

| this gate will become '0' then G4, G5 & G6 are enabled. Once the CLK pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   | Now we are applying the control signal '1 to NOT gate then the output of                        |      |     |        |

| pulse is applied to FFs, then the data '1101' is shifted to the right side from one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                                                                                                 |      |     |        |

| one OR gate to the other.  c)How many clock pulses are required to load a 4-bit data in SIPO register and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                                                                                                 |      |     |        |

| and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                                                                 |      |     |        |

| and how many clock pulses are required to transfer the data to an output register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | c) How many clock pulses are required to load a 4-bit data in SIPO register                     |      |     |        |

| register?  Ans-4 clock pulses are required to load a 4-bit data in SIPO register and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                                                                                 |      |     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                                                                 |      |     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | And A clock mulgas are required to load a 4 hit data in SIDO register and                       |      |     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                                                                 |      |     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 | Design a synchronous counter using D flip-flops which counts in the                             |      |     |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | following sequence. $0 \rightarrow 4 \rightarrow 7 \rightarrow 2 \rightarrow 3 \rightarrow 0$ . | [10] | CO4 | L2, L3 |

[4+6]

CO1

L1, L2

What is the difference between active filter and passive filter.

4

| S.No | Active filters                                                                                           | tive filter and passive filters                                                                                             |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1    | Filters with components such as                                                                          | Passive filters                                                                                                             |  |  |  |  |  |  |

|      | operational amplifiers, transistors or other active elements are known as active filters.                | Filters with only components like R, L and C are known as passive filters                                                   |  |  |  |  |  |  |

| 2    | Active filters require an external power supply for operation. Capable of providing power gain.          | Passive filters do not need an external power source for operation. Incapable of providing power gain.                      |  |  |  |  |  |  |

| 3    | Due to feedback loops used for regulating the active components may contribute to oscillation and noise. | Passive filters have a better stability and can withstand large currents.                                                   |  |  |  |  |  |  |

| 4    | Active filters have frequency limitations due to active elements.                                        | Passive filters have no frequency limitation.                                                                               |  |  |  |  |  |  |

| 5    | Active filter circuits are more compact and less heavy and operate with high speed                       | Due to presence of inductors, Passive filters are bulky/heavy in nature, they consume more power and operate with low speed |  |  |  |  |  |  |

|      | Can be fabricated in IC form and mass production making it cheaper.                                      | Difficult to fabricate in IC form and usually designed using discrete components.                                           |  |  |  |  |  |  |

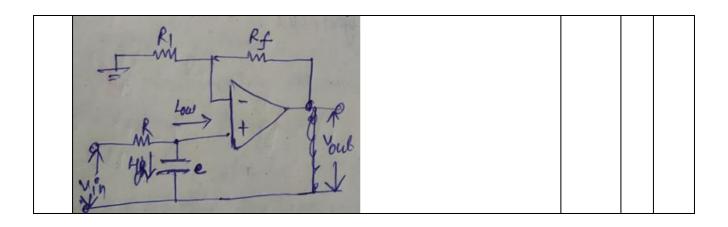

b) Design a first order low pass filter with a cut off frequency of 2.2 kHz and with pass band gain of 2 (Assume C=0.01  $\mu$ F)

and with pass band gain of 2 (Assume C=0.01

$$\mu$$

F)

$$\int_{R} = 2.2 \times H2$$

Assume  $e = 0.01 \times F$

$$\Rightarrow R = \frac{1}{2\pi f_{H}}e^{-\frac{1}{2\pi N2.2 \times 10^{3}}} \times 0.01 \times 10^{6}$$

$$\Rightarrow R = 1 + \frac{R_{1}}{R_{1}}$$

$$\Rightarrow 2 = 1 + \frac{R_{1}}{R_{1}}$$

$$\Rightarrow 2 = 1 + \frac{R_{1}}{R_{1}}$$

$$\Rightarrow R_{1} = 1 \Rightarrow R_{1} = R$$

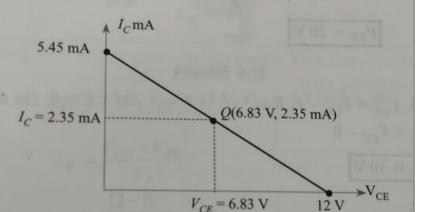

For the circuit shown in figure, a silicon transistor (VBE=0.7 V) with  $\beta$ =50 is used. Draw the dc load line and determine the operating point.  $R_B = 240 \text{ k}\Omega$   $R_C = 2.2 \text{ k}\Omega$ [1] CO1 L2, L3

$$R_B = 240 \text{ k}\Omega, \ \beta = 50, \ V_{CC} = 12 \text{ V}$$

$R_C = 2.2 \text{ k}\Omega. \text{ Assume } V_{BE} = 0.7 \text{ V}$

$I_B = \frac{V_{CC} - V_{BE}}{R_B} = \frac{12 - 0.7}{240 \times 10^3}$

$I_C = \beta I_B$

$= 50 \times 47.08 \, \mu\text{A}$

$I_C = 2.35 \, \text{mA}$

$V_{CE} = V_{CC} - I_{C}R_{C}$

$= 12 - \left[2.35 \times 10^{-3} \times 2.2 \times 10^{3}\right]$

$\therefore V_{CE} = 6.83 \, \text{V}$

When

$$I_C = 0$$

,  $V_{CE} = V_{CC} = 12 \text{ V}$

) When

$$V_{CE} = 0$$

,  $I_C = \frac{V_{CC}}{R_C} = \frac{12}{2.2 \times 10^3}$

$$I_C = 5.45 \, \text{mA}$$

$[1]_{\text{CO1}}$

L1, L2

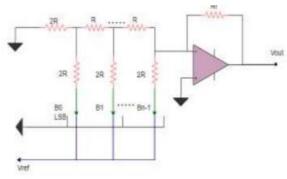

6 Derive the expression of output voltage of R-2R Ladder circuit.

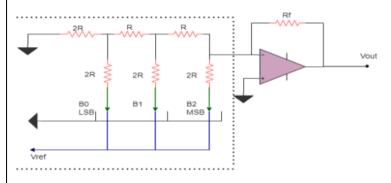

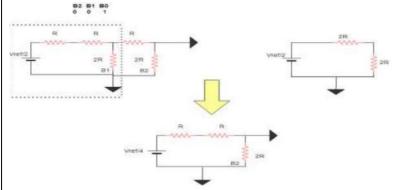

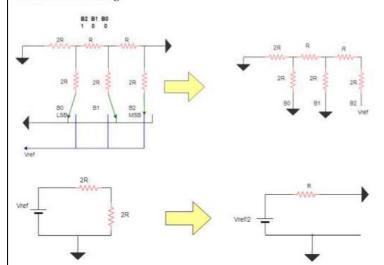

Ans- R-2R configuration is a simple arrangement that consists of parallel and series resistors connected in the cascaded form to an operational amplifier The following diagram shows the R-2R 3-bit ladder DAC.

- The leftmost side of the circuitry has the least significant bit i.e B0 whereas B2 which is the most significant bit is connected to the right side of the circuit to the amplifier.

- The binary inputs are given through the binary switches. So, when we need a high bit, the concerned bit is connected to the reference voltage and when a low bit is needed, the switch gets connected to the ground potential.

• The ladder arrangement consists of two resistors i.e. a base resistor R and a 2R resistor which is twice the value of the base resistor.

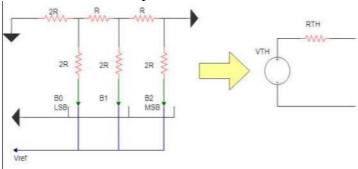

**R-2R Ladder DAC Analysis with Thevenin Theorem** Thevenin's theorem is a technique through which we can obtain an equivalent circuit of the concerned resistance network. A Thevenin circuit consists of a Thevenin resistance and a Thevenin voltage that can be replaced in the circuit and work the same as the original resistance network

RTh is calculated by short-circuiting all the voltage sources and replacing the current sources with open circuits.

## When LSB is high

Let us first consider the binary code 001. Its VTh and RTh will be calculated in three stages.

$VTh= 2R \times Vref / 2R+2R$

VTh=Vref / 2

For measuring the Thevenin resistance, short circuit the reference voltage. Two resistances 2R and 2R become parallel to each other.

So, RTh=2R  $\parallel$  2R

Below is the equivalent circuit of the original after simplifying the first stage. The Thevenin equivalent of the first stage is connected in series to the rest of the circuit.

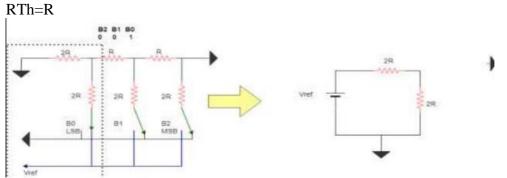

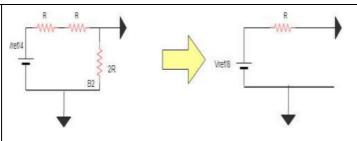

Now, we calculate the Thevenin circuit of the second stage. The dotted block will be solved in the second stage. Two resistors of the same value i.e R are connected in series. So it is replaced by equivalent resistance 2R shown in the given diagram below.

The circuit is again configured to be a voltage divider with reference voltage as Vref/2.

So,  $VTh= (2R \times Vref/2) / 2R+2R$

VTh=Vref / 4

for the Thevenin resistance, we consider the voltage source of this block to be zero. It gives the same Thevenin as the previous because of the exact arrangement and we will replace the concerned portion with equivalent Thevenin values

RTh=2R || 2R

RTh=R

This is the resultant circuit which will be solved in the third stage. The VTh and RTh is as follows:

$VTh = (2R \times Vref/4) / 2R + 2R$

VTh=Vref / 8

$RTh=(R+R) \parallel 2R$

RTh=R

The solution depicts that whenever only B0 is connected to the reference voltage and B2=B1=0, he output voltage of the DAC would be Vref/8.

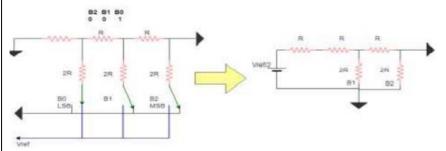

Similarly when the B1 high

When MSB Bit is high

## When all three bits are high

When all 3 bits are connected to the reference voltage, the output voltage will be the superposition of all three voltages.

Vr-2r = (Vref / 2)+(Vref / 4)+(Vref / 8)

$Vr-2r = 7Vref \ / \ 8 \ Vr-2r = Vref \{ B0/2(N) + B0/2(N-1) + B0/2(N-2) + \ldots + B0/22 + B0/21 \ \}$

Where N is the number of bits.

Vr-2r is applied to the inverting operational amplifier and the output voltage is measured. The output would be 180 degrees out of phase with the input Vr-2r. The following is the general output voltage equation of

R-2R DAC

$Vout = -(Rf/R) \times Vr-2r$

Vout =  $-(Rf/R)\{B0/2(N) + B0/2(N-1) + B0/2(N-2) + ... + B0/22 + B0/21\}$  Vref The gain of the DAC is decided by the (Rf/R) factor..

Faculty Signature CCI Signature HOD Signature

## CO PO Mapping

|     |                                                                                                                                                                                                         | Course Outcomes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     | Modu<br>les<br>cover<br>ed | P<br>O<br>1                    | P<br>O<br>2 | P<br>O<br>3 | P<br>O<br>4 | P<br>O<br>5 | P<br>O<br>6 | P<br>O<br>7 | P<br>O<br>8 | P<br>O<br>9 | P<br>O<br>1<br>0 | P<br>O<br>1<br>1 | P<br>O<br>1<br>2 | P<br>S<br>O<br>1 | P<br>S<br>O<br>2 | P<br>S<br>O<br>3 | P<br>S<br>O<br>4 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------|--------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| CO1 | Design and analyze application of analog circuits using photo devices, timer IC, power supply and regulator IC, op-amp and basic principles of A/D and D/A conversion circuits and to develop the same. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                            | 3                              | 3           | 3           | 2           | 2           | 0           | 0           | 0           | 0           | 0                | 0                | 0                | 0                | 2                | 0                | 2                |

| CO2 | SOP, PO                                                                                                                                                                                                 | nte logical expressions for minion of the logical expression |                     | 2                          | 3                              | 3           | 3           | 2           | 2           | 0           | 0           | 0           | 0           | 0                | 0                | 0                | 0                | 2                | 0                | 2                |

| CO3 | Design combinational logic circuits using gates encoders, decoders, multiplexers, demultiplexers, CO3 Comparators, arithmetic-logic units and to build simple applications.                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | lexers,             | 3                          | 3                              | 3           | 3           | 3           | 2           | 0           | 0           | 0           | 0           | 0                | 0                | 0                | 0                | 2                | 0                | 2                |

| CO4 | CO4 Understand the use of latches, flip-flops, Switc Contact Bounce Circuits and Variou Representation of FLIP-FLOPs and use them i designing, registers and counters.                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <sup>7</sup> arious | 5                          | 3                              | 3           | 3           | 3           | 2           | 0           | 0           | 0           | 0           | 0                | 0                | 0                | 0                | 2                | 0                | 2                |

|     | CO5 Develop simple HDL programs  COGNITIVE                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                     |                            | 3                              | 3           | 3           | 3           | 2           | 0           | 0           | 0           | 0           | 0                | 0                | 0                | 0                | 2                | 0                | 2                |

|     | VEL                                                                                                                                                                                                     | F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | REVISE              | D BLOO                     | MS '                           | ГАХ         | KON         | OM          | ΥK          | EYV         | VOF         | RDS         |             |                  |                  |                  |                  |                  |                  |                  |

| I   | ـ1                                                                                                                                                                                                      | List, define, tell, describe, io when, where, etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | dentify             | , show,                    | lab                            | el, c       | olle        | ect,        | exa         | min         | ie, t       | abul        | late        | , qu             | ote,             | na               | me,              | wh               | ο,               |                  |