| USN |  |  |  |  |  |

|-----|--|--|--|--|--|

## Internal Assessment Test 3 – Feb. 2023

| Sub:                           | Digital System Design using Verilog                                                        |                    |              |            | Sub Code | : 21EC32  | Branch:        | ECE       |     |     |  |

|--------------------------------|--------------------------------------------------------------------------------------------|--------------------|--------------|------------|----------|-----------|----------------|-----------|-----|-----|--|

| Date:                          | 08-02-2023 Duration: 90 Minutes Max Marks: 50 Sem/Se                                       |                    |              |            |          | Sem / Sec | 3/A,B,         | 3/A,B,C,D |     | OBE |  |

| Answer any FIVE FULL Questions |                                                                                            |                    |              |            |          | MARKS     | CO             | RBT       |     |     |  |

| 1 (a)                          |                                                                                            |                    |              |            |          |           |                | [04]      | CO3 | L1  |  |

|                                | excitation table for the JK flip-flop.                                                     |                    |              |            |          |           |                |           |     |     |  |

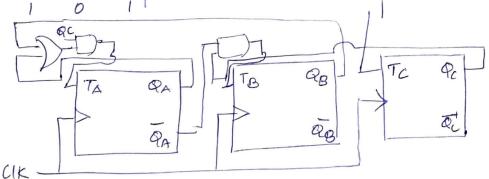

| 1 (b)                          | (b) Design a Mod-6 synchronous counter using T Flip-flop. [06]                             |                    |              |            |          |           | [06]           | CO3       | L2  |     |  |

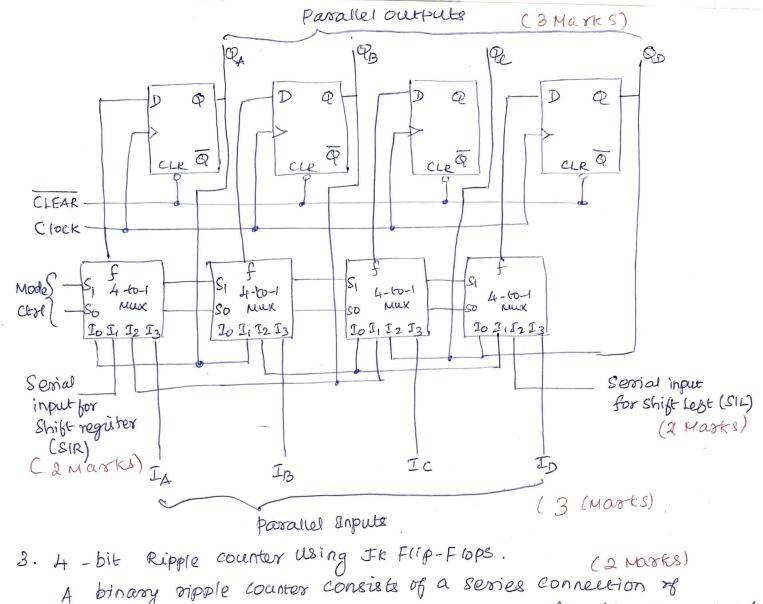

| 2                              | 2 Design a 4-bit universal shift register using positive edge triggered D-flip-flop        |                    |              |            |          |           | ed D-flip-flop | [10]      | CO3 | L3  |  |

|                                | and multiplexer                                                                            | rs to <u>opera</u> | te as indica | ted below: |          |           |                |           |     |     |  |

|                                |                                                                                            | ]                  | Mode select  | d Opera    | tion     |           |                |           |     |     |  |

|                                |                                                                                            |                    | 00           | Hol        | d        |           |                |           |     |     |  |

|                                |                                                                                            |                    | 01           | Right S    | Shift    |           |                |           |     |     |  |

|                                |                                                                                            |                    | 10           | Left S     | hift     |           |                |           |     |     |  |

|                                |                                                                                            |                    | 11           | Parallel   | Load     | 1         |                |           |     |     |  |

| 3                              |                                                                                            |                    |              |            |          |           |                | [10]      | CO3 | L2  |  |

|                                | Compare the counters based shift register.                                                 |                    |              |            |          |           |                |           |     |     |  |

| 4                              | Illustrate with examples the data types used to define nets, registers, vectors [10] CO4 I |                    |              |            |          |           | L2             |           |     |     |  |

|                                | and arrays.                                                                                |                    |              |            |          |           |                |           |     |     |  |

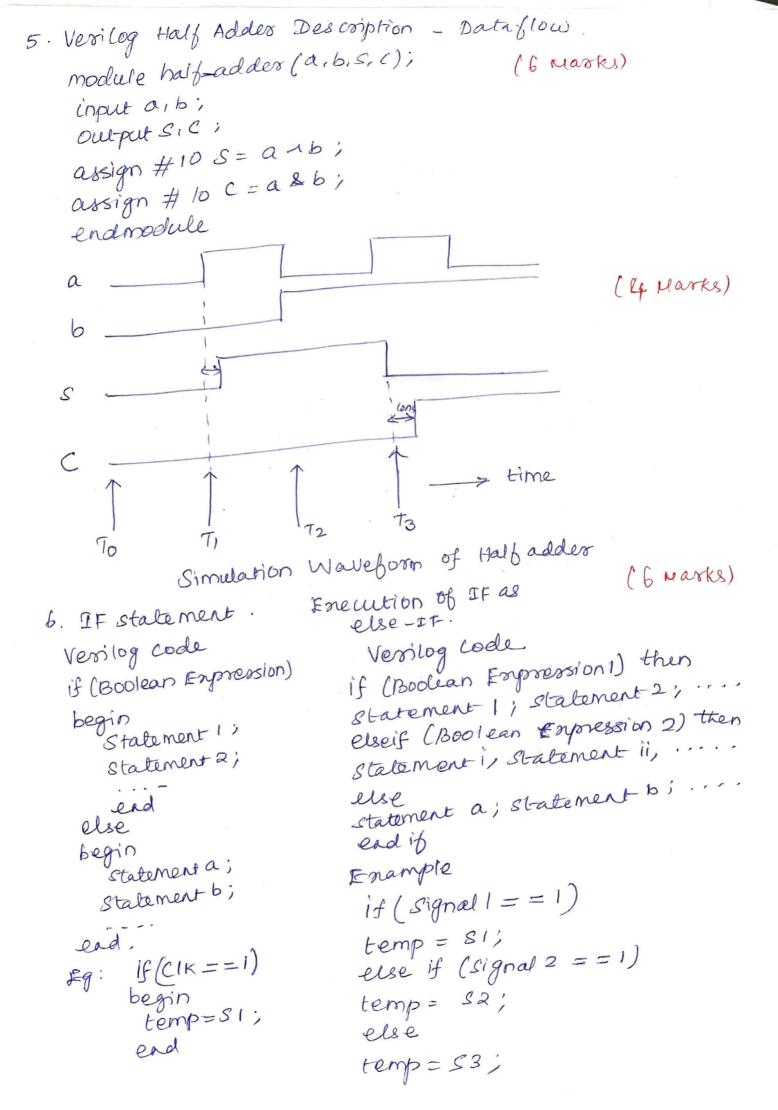

| 5                              |                                                                                            |                    |              |            |          |           | CO4            | L3        |     |     |  |

|                                | assign a delay time to the signal assignment statement with the timing                     |                    |              |            |          |           |                |           |     |     |  |

|                                | waveform.                                                                                  |                    |              |            |          |           |                |           |     |     |  |

| 6                              | 6 Illustrate the IF statement, IF as ELSE-IF, signal and variable assignment with          |                    |              |            |          |           | [10]           | CO4       | L3  |     |  |

|                                | an example.                                                                                |                    |              |            |          |           |                |           |     |     |  |

| 7                              | Explain the behavioral description of a Positive Edge-Triggered JK flip-flop [10] CO4 L2   |                    |              |            |          |           | L2             |           |     |     |  |

|                                | using the CASE statement with the timing waveform.                                         |                    |              |            |          |           |                |           |     |     |  |

## 21 EC32 - Digital System Design Wing Verilog

Internal Assessment Test 3

Answer Key

Characteristic Equation 1. a)

SR Hip-Flop: Qt = S+RQ

T Flip-Flop: 9= TQ+TQ

1 Mark)

(1 Mark)

Excitation Table:

(2 Marks)

| 9 | Qt | J     | K   |

|---|----|-------|-----|

| C | 0  | 0     | X   |

| 0 | )  | 1     | X   |

| 1 | C  | ) .   | X I |

| 1 |    | ( ) > | ( 0 |

7-Flip-Flop b) Mod-6 Synchronous counter using A QA+ QB+QC+ QA QB QC 0 0 0 1 0 0 0 0 TA = BC + AC 0 0 = C(A+B) 0 0

0 0 0 0 1 0 0 1

0 0 0 (2 Marks) 0 0

0 X X TB = AC TC=1

(2 Marks)

4-bit Universal Shift Register 2.

Operation Hode select Hold 00 Right Shift 01 Left shift 10

parallel Load

binary sipple counter consists of a series connection of complementing flip-flops, with the output of each flip-flop connected to clock-pulse input of the next-higher order flip blop. All I and k inputs are equal to 1. (4 Marks) MaB Decimal Value 93 93 Ò J2 92 53 Jo 91 00 0 0 CIK FFO FFI FF2 0 Po I Q1 9 60 11 ( 4 Marks) P3 12 14

15

4. Verilog Data Types

Verilog supports several data types, including: nete, registers,

Vectors, integer, real, parameters and arrays.

Nets: It is declared by the predefined word wire. Nets have Value that Change continuously by the circuits that are driving 12 Marks 1

them.

Net Values Verilog Definiteon Value O logic o (false)

I logic I (true)

X. Lenknown

Z. High impedance Enample: wire sum; (Declares a net by name sum) wire 81=1'60; (initial value of s) is declared).

Registers: It stores the value until they are updated. It is defined by the predefined word neg (4 Marks)

Verilog Register values

| Verollag |                 |

|----------|-----------------|

| Value    | Definition      |

| 0        | Logic o (false) |

| 1        | cogic 1 (Ence)  |

| X        | unknown         |

| Z        | High impedance  |

Enample: veg Sum-total; The statement declares a register by the name sum total.

Vectors: vectors are multiple bits. A register or a net can be declared as a vector. Vectors are declared by brackets[] Example:

Wire [8:0] a = 4'blo10; The Statement declares Net a. It

wire [8:0] a = 4'blo10; has 4-bits and its initial value is 1010. register total. Its size is 8 bits and

reg [7:0] total = 8'd12; Arrays: It doesnot have decimal value is 12. (2 marks

a predefined word for array. Register and integers can be written as arrays.

Enample:

parameter N= 4; pasameter N= 3; reg signed [M; 0] carry[0:N]; reg [M:0] b[0;N]; integer Sum [6: N];

```

Signal and variable Assignment

(4 Marks)

Enample: module D. latch (d. E. P. P6);

input d, E;

Output Q, 96;

reg Q, Qb;

always @ (d, E)

begin

if (E == 1)

begin Q=d;

Qb=NQ;

endmodule

7. positive Edge Inggered JK Flip-flop

positive edge Flip-Flops Sample the input only at the positive

edges of the clock; any change in the input that does not

occur at the edges is not sampled by the output. (4 Marks)

State diagram

Verilog Positive Edge - Triggened Jk Flip-Flop using case

module JK-FF (JK, Clk, 9,96);

(6 Marks)

input [1:0] Jk;

input CIK;

output reg 9,96;

always @ (poredge CIK)

begin

Case (Jt)

2'do: 9=9;

2'd1; q=0;

2'd2: 9=1;

2'd3: 9=~9;

endcase

9b=~91;

end

endmodule

```