## Analog Electronic Circuits- 21EC34

## IAT3 Solution-Feb 2023

|     | IR<br>STITUTE OF<br>CHNOLOGY                                                                                                                                                                            | US                                                                                                                                    | N                     |          |         |            |        |        |                 | TI SER POTTO | SCMR |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------|------------|--------|--------|-----------------|--------------|------|

|     |                                                                                                                                                                                                         | Internal A                                                                                                                            | ssesmer               | nt Test  | - III   |            |        |        |                 |              |      |

| Sub | DE                                                                                                                                                                                                      | Analog Electronic Circuits Code                                                                                                       |                       |          |         |            |        |        | e:              | 21EC34       |      |

| Da  | ate: 07/02/2023                                                                                                                                                                                         | Duration: 90 mins                                                                                                                     |                       |          |         |            |        |        | nch:            | ECE          |      |

|     | 1                                                                                                                                                                                                       | Answer Any                                                                                                                            | FIVE F                | ULL Q    | estions | S          |        |        |                 |              |      |

|     |                                                                                                                                                                                                         |                                                                                                                                       |                       |          |         |            |        | Marks  | OBE             |              |      |

| 1.  | Explain the operati                                                                                                                                                                                     | ion of a Successive -                                                                                                                 | approxi               | mation   | ADC     | with no    | at c   | ircuit |                 | CO4          | L2   |

| 2.  | Give the circuit diagram, gain expression and frequency response plots of:  (a) First order Low pass filter  (b) Second order Low pass filter  (c) Wide band pass filter  (d) Narrow band reject filter |                                                                                                                                       |                       |          |         |            |        | [10]   | CO4             | L2           |      |

| 3.  | What are the different                                                                                                                                                                                  | t turn on methods of SC                                                                                                               | CR? Exp               | olain ea | ch of   | them in o  | letail |        | [10]            | CO5          | L2   |

| 4   | Draw the circuit and fi<br>expression for the cut                                                                                                                                                       | requency response of a off frequency.                                                                                                 | second                | order l  | ow pa   | ss filter. | Deri   | ve an  | [10]            | CO4          | L3   |

| 5.  | Explain the static An                                                                                                                                                                                   | ode – Cathode characte                                                                                                                | eristics o            | of SCR   | with c  | ircuit dia | agran  | n and  | [40]            | 505          |      |

| Э.  | Explain the static Anode – Cathode characteristics of SCR with circuit diagram and VI characteristics. Define Latching and Holding Currents.                                                            |                                                                                                                                       |                       |          |         |            |        | [10]   | CO5             | L2           |      |

| 6.  | Explain the working of UJT and how UJT firing circuit is used for triggering ar SCR.                                                                                                                    |                                                                                                                                       |                       |          |         |            |        | [10]   | CO5             | L2           |      |

| 7   | What is commutation? What are the different types of Commutation? Explain class A commutation in detail.                                                                                                |                                                                                                                                       |                       |          |         |            |        | [10]   | CO <sub>5</sub> | L2           |      |

| 8.  | Determine the trigge<br>Ig(min) = 0.1mA, V                                                                                                                                                              | diagram, explain the ver angle $\alpha$ for the follow $g(min) = 0.5 \text{ V}$ . The diagram $Rv = 100k\Omega$ , $Rmin = 100k\Omega$ | ving spe<br>ode is si | cificati | ons:-   |            | line.  |        |                 | CO5          | L3   |

## 1. SAR ADC

ADC converts an analog voltage to digital outfut that best represents the input. ADC are also openified as 8, 10,12,16. etc. bit.

# Successive - Approximation ADC.

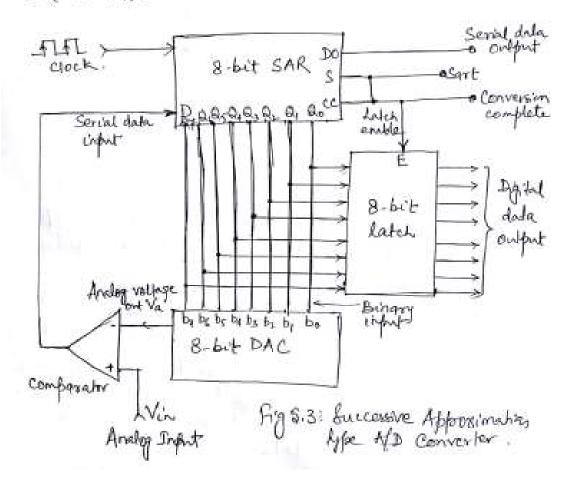

following figure Fig 5.3 shows a successiveapproximation type ADC, which uses a comparator, a successive-approximation regulater, output latches and a DAC:

The circuit work as follows:

· At the start of a convertion cycle, the SAR is reset by holding the start (5) signal high.

. On the LOW- to- HIGH transition, the most significant outfut bit 07 of the

SAROM is set.

. The DIA converter then generales an analog equivalent to the Qq bit, which is compared with Vin.

· If the 100g comparator onlyind is low, that means DAC origint > Vin and the SAR will clear its MSB Q7. On the other hand if comparator outful is high, which mesers . DAC output < Vin. the SAR mill keep MSB Qq sed.

· similarly depending as on the comparator output, the se SAR will then keep either beep Bo or react bit Q6, on the next clock pulse LOW- to- high.

· As soon this process is continued until the SAR fries all the bits i'e Q5, Q4, Q3, Q2, & Q, and Qo

. As soon as LSB Qo 5 forced, the SAR forces the conversion complete (cc) signal HIGH to indicate that the parallel output lines contains valid data.

· The CC signal in turno enables the latch, and digital data appear at he output of the latch, which gives the digital representation of the analog voltage Vin.

· For 8 bit SAR type ADC eight clock fulne is required, for 12 bit, 12 clock forlar is required and so on .

· Advantage -> High speed -> Excellent Resolution.

### Example

| Clk          | B3  | B2         | B1                              | BO     | VD     | VA>VD | Decision                | VO                  | ор  |  |  |  |

|--------------|-----|------------|---------------------------------|--------|--------|-------|-------------------------|---------------------|-----|--|--|--|

|              | 2.5 | 1.25       | 0.625                           | 0.3125 |        |       |                         |                     |     |  |  |  |

| 1            | 1   | 0          | 0                               | 0      | 2.5    | No    | Reset                   | 0                   |     |  |  |  |

| 2            | 0   | 1          | 0                               | 0      | 1.25   | Yes   | Set                     | 1.25                |     |  |  |  |

| 3            | 0   | 1          | 1                               | 0      | 1.875  | Yes   | Set                     | 1.875               |     |  |  |  |

| 4            | 0   | 1          | 1                               | 1      | 2.1875 | No    | Reset                   | 1.875               | 01  |  |  |  |

| VA<br>Atalog |     | Comparator | Soccount Approximation Register | — ак   |        | V =   | 2V<br>=5<br>o Size =5/1 | 16= 0.31            | 125 |  |  |  |

|              |     |            | 1                               | (50)   |        | 1000  |                         | 375)*100/2<br>=6.2% |     |  |  |  |

- 2. Give the circuit diagram, gain expression and frequency response plots of:-

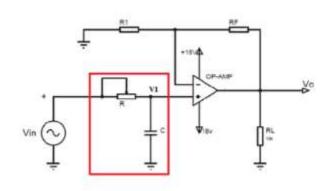

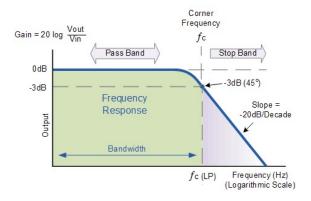

- (a) First order Low pass filter

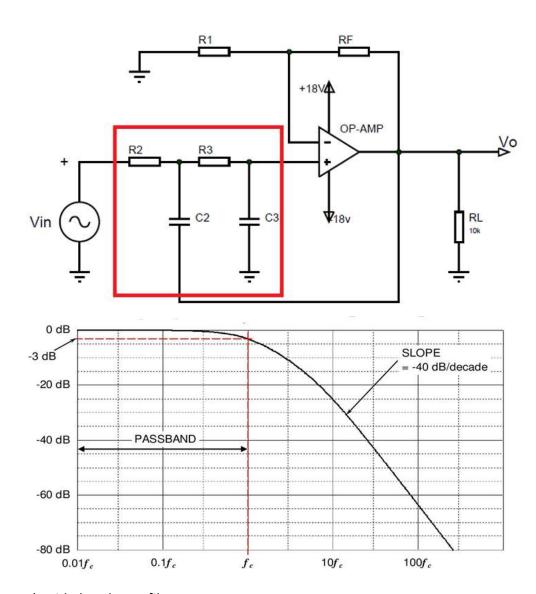

- (b) Second order Low pass filter

- (c) Wide band pass filter

- (d) Narrow band reject filter

- a) First order Lowpass

$$\frac{v_{out}}{V_{in}} = \frac{A_F}{1 + j\frac{f}{f_H}}$$

$$f_H = \frac{1}{2\pi RC}$$

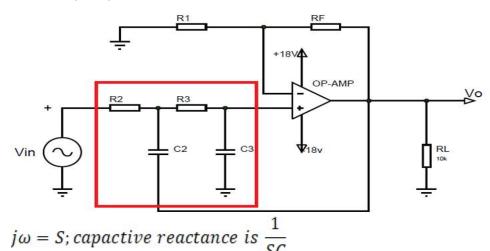

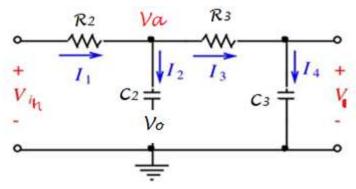

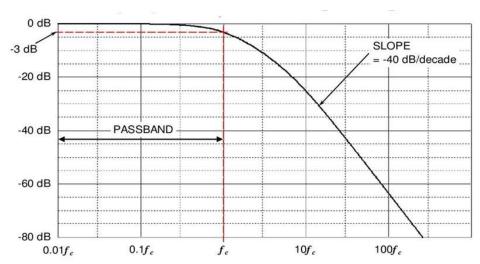

b) Second order Low pass

$$\frac{V_0}{V_{in}} = A_F * \frac{\frac{1}{(R_2 C_2 C_3 R_3)}}{S^2 + \frac{(R_2 C_3 + R_2 C_2 + R_3 C_3 - R_2 C_2 A_F)S}{R_2 C_2 C_3 R_3} + \frac{1}{(R_2 C_2 C_3 R_3)}}$$

$$f_H = \frac{1}{2\pi\sqrt{(R_2C_2\ C_3R_3)}}$$

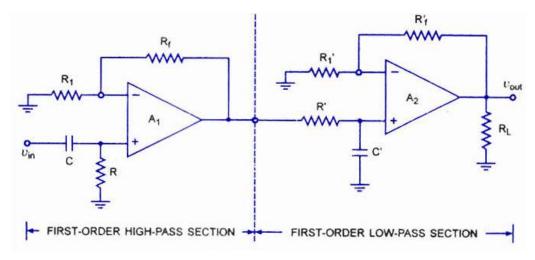

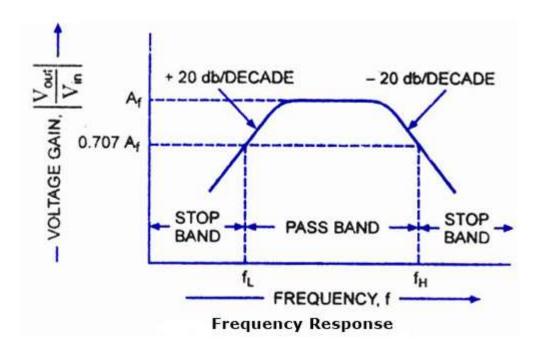

### c) Wide band pass filter

$$\left| \frac{v_{out}}{V_{in}} \right| = \frac{A_{F2}A_{F1} * \frac{f}{f_L}}{\sqrt{\left\{ 1 + (\frac{f}{f_H})^2 \right\} \left\{ 1 + (\frac{f}{f_L})^2 \right\}}} \qquad f_H = \frac{1}{2\pi R^1 C'}$$

$$f_L = \frac{1}{2\pi RC}$$

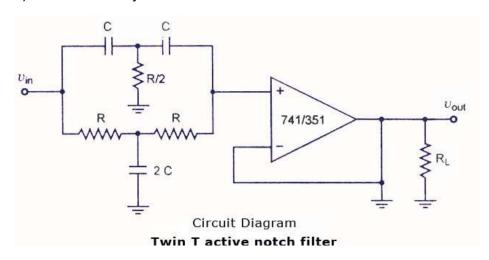

### d) Narrow band reject filter

$$f_N = \frac{1}{2\pi RC}$$

3. What are the different turn on methods of SCR? Explain each of them in detail.

Tuen-on methods A thisperitor can be bruned on from non-conducting state to a Conducting state in several ways :-@ Forward voltage briggering - when VAK is increased with gate cht open, Is will have analometre breakdown at break over vollage VBO At the vollage, theyester Changes from OFF to ON state.

(2) Thermal triggering The width of the depletion Layer of a thyristor decreases on increasing the function temperature. So wherethe VAK in very mean to Van, the device can be triggered by increasing at junction temperature

@ Radiation triggering ( Light triggering). Thyrister is born barded by energy particles such or neutrons or photons with the help of this external energy, elected shok priors are generated which will increase the number of charge carriers causing inflantaneous flow of current For this to happen, the divise must have high value of trale of change of volloge ( dt)

(4) dr laiggering - When seris in farmand brazd mode, Jz will gernain geverse brazd. Jz Two the characteristics of a capacitar due to charges across the junction of the voltage empress a cross the derice is V, the charge Q, and the junction capacitance (G), then

ie = de = de (cjv) - cjdv + vde

1. ic = SI dV

species so if rate of change of ve flago, de u

large, the device may twen on . (5) Grate baggering - Most commonly used method By applying a posture Signal at the gate, Sex can be briggered much before the break overvollage Three ligger of gate briggering pulses are 5

word:

(A) DC gate briggering - DC Vectoge of Proper

magnitude and polarity and applied betweengate

and calkoole. Bready - No wolation, more gate lay.

(b) AC gate langgering - Mort used in all ac

applications. Provides proper wolation between

Power and control arcents. Phase angle control

will provide proper firing angle.

(c) Pulse gate briggering - Most popular method.

A sequence of gate pulses are given to transon

an SCR. This is known as carrier frequency

gating. A transformer is used for isolation.

There is no need of applying continuous signals,

so gate lesses are very much reduced.

4. Draw the circuit and frequency response of a second order low pass filter. Derive an expression for the cut off frequency.

### **KCL** Equations

$$\begin{split} V_{in} &= (R_2 C_2 \ C_3 R_3 S^2 + \ C_3 R_2 S + \ C_3 R_3 S + R_2 C_2 S - R_2 C_2 S A_F + 1) V_1 \\ \frac{V_{in} - V_a}{R_2} &= C_2 S (V_a - V_o) + \frac{V_a - V_1 V_a - V_1}{R_3 \ R_3} = C_3 S V_1 \end{split}$$

$$V_a = (C_3 R_3 S + 1) V_1$$

$$V_{in} = (R_2 C_2 S + 1) V_a + R_2 * \frac{V_a - V_1}{R_3} - R_2 C_2 S V_o$$

$$V_{in} = (R_2 C_2 S + 1) V_a + R_2 * \frac{V_a - V_1}{R_3} - R_2 C_2 S V_o$$

$$V_{in} = (R_2 C_2 S + 1) V_a + R_2 * \frac{V_a - V_1}{R_3} - R_2 C_2 S V_o$$

$$V_{in} = (R_2 C_2 S + 1 + \frac{R_2}{R_3}) V_a - V_1 (\frac{R_2}{R_3} + R_2 C_2 S A_F)$$

$$V_{in} = (R_2 C_2 S + 1 + \frac{R_2}{R_3}) (R_3 C_3 S + 1) V_1 - V_1 (\frac{R_2}{R_3} + R_2 C_2 S A_F)$$

$$\begin{split} \frac{V_1}{V_{in}} &= \frac{\frac{1}{(R_2C_2C_3R_3)}}{S^2 + \frac{(R_2C_3 + R_2C_2 + R_3C_3 - R_2C_2A_F)S}{R_2C_2C_3R_3} + \frac{1}{(R_2C_2C_3R_3)}}\\ \frac{V_0}{V_{in}} &= A_F * \frac{\frac{1}{(R_2C_2C_3R_3)}}{S^2 + \frac{(R_2C_3 + R_2C_2 + R_3C_3 - R_2C_2A_F)S}{R_2C_2C_3R_3} + \frac{1}{(R_2C_2C_3R_3)}}\\ \omega_n &= \frac{1}{\sqrt{(R_2C_2C_3R_3)}} f_H = \frac{1}{2\pi\sqrt{(R_2C_2C_3R_3)}}\\ \left| \frac{v_{out}}{V_{in}} \right| &= \frac{A_F}{\sqrt{1 + (\frac{f}{f_H})^4}} \end{split}$$

$$\frac{V_O}{V_{in}} = A_F * \frac{\frac{1}{RC^2}}{S^2 + \frac{(3 - A_F)S}{RC} + \frac{1}{RC^2}}$$

$$2\zeta = 3 - A_F$$

For Butter-worth Approximation

## $\zeta = 0.707$ , then $A_F = 1.586$

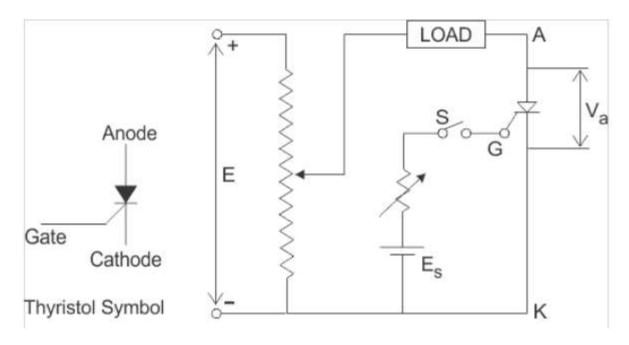

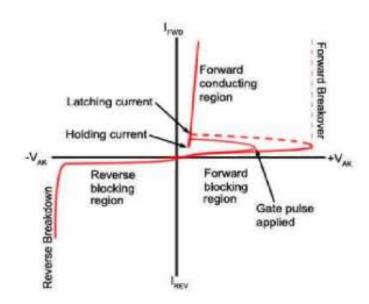

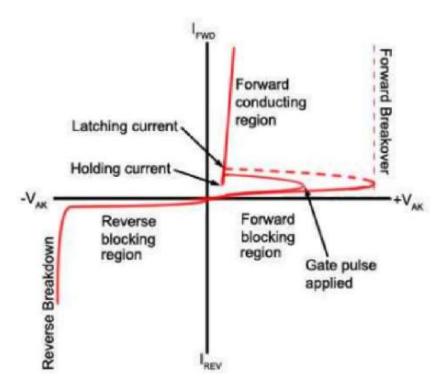

5. Explain the static Anode – Cathode characteristics of SCR with circuit diagram and VI characteristics. Define Latching and Holding Currents.

### Circuit diagram

Forward Blocking mode

In this mode of operation, the positive voltage is applied to the anode and the negative voltage applied to the cathode, there will not be any pulse applied to the gate, it will be kept in the open state. Once the voltage is applied, the junctions J1 and J3 will be forward biased and the junction J2 will be reverse biased. Since J2 is reverse biased the width of the depletion region increases and it acts as an obstacle for conduction, so only a small amount of current will be flowing from J1 to J3.

#### **Forward Conduction Mode**

The Forward Conduction Mode is the only mode at which the SCR will be in the ON state and will be conducting. We can make the SCR conduct in two different ways, one we can increase the applied forward biasWhen we increase the Applied forward bias voltage between the anode and cathode the junction J2 will be depleted due to the avalanche breakdown and the SCR will start conducting. We are not able to do this for all the applications and this method of activating the SCR will eventually reduce the lifetime of the SCR. If you want to use the SCR for low voltage applications you can apply a positive voltage to the gate of the SCR. The applied positive voltage will help the SCR to move to the conduction state. During this mode of operation, the SCR will be operating in forward bias and current will be flowing through it. voltage beyond the breakdown voltage or else we can apply a positive voltage to the gate terminal.

#### **Reverse Blocking Mode**

In the reverse blocking mode, the positive voltage is applied to the Cathode (-) and the Negative voltage is given to the Anode (+), There will not be any pulse given to the gate, it will be kept as an open circuit. During this mode of operation the Junctions J1 and J3 will be reverse biased and the junction J2 will be forward biased. Since the junctions J1 and J3 are reverse biased there will not be any current flowing through the SCR. Although there will be a small leakage current flowing due to the drift charge carriers in the forward-biased Junction J2, it is not enough to turn on the SCR.

- 1. Breakover Voltage- It is the minimum forward voltage, gate being open, at which SCR starts conducting heavily i.e. turned on. Commercially available SCRs have breakover voltages from about 50 V to 500 V.

- 2. Peak Reverse Voltage (PRV)- It is the maximum reverse voltage (cathode positive w.r.t. anode) that can be applied to an SCR without conducting in the reverse direction.

**Latching current** of forward biased SCR is the minimum current which anode current must attain to continue to remain in forward conduction mode even when gate current is removed.

**Holding current** of SCR or thyrsistor is that minimum value of current below which anode current must fall to come in OFF state.

6. Explain the working of UJT and how UJT firing circuit is used for triggering an SCR.

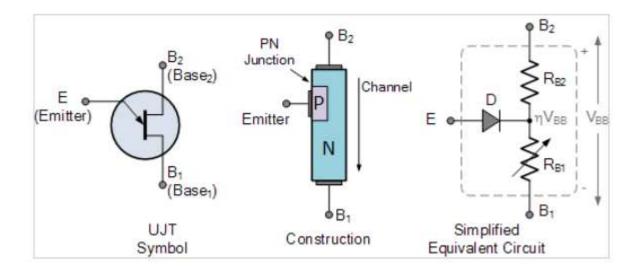

The Unijunction Transistor or UJT for short, is a solid state three terminal device that can be used in gate pulse, timing circuits and trigger generator applications to switch and control either thyristors and triac's for AC power control type applications. Like diodes, unijunction transistors are constructed from separate P-type and N-type semiconductor materials forming a single (hence its name Uni-Junction) PN-junction within the main conducting N-type channel of the device.

## Unijunction Transistor (UJT)

For a Unijunction transistor, the resistive ratio of R<sub>B1</sub> to R<sub>BB</sub> is called the intrinsic stand-off ratio (η).

$$\eta = \frac{R_{B1}}{R_{B1}+R_{B2}}$$

Typical standard values of η range from 0.5 to 0.8 for most common UJT's.

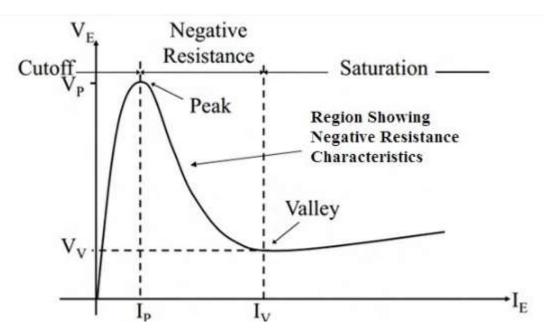

Characteristics

If a small positive input voltage which is less than the voltage developed across resistance, RB1 (  $\eta VBB$  ) is now applied to the Emitter input terminal, the diode p-n junction is reverse biased, thus offering a very high impedance and the device does not conduct. The UJT is switched "OFF" and zero current flows.

However, when the Emitter input voltage is increased and becomes greater than VRB1 (or  $\eta VBB + 0.7V$ , where 0.7V equals the p-n junction diode volt drop) the p-n junction becomes forward biased and the unijunction transistor begins to conduct. The result is that Emitter current,  $\eta IE$  now flows from the Emitter into the Base region.

The effect of the additional Emitter current flowing into the Base reduces the resistive portion of the channel between the Emitter junction and the B1 terminal. This reduction in the value of RB1 resistance to a very low value means that the Emitter junction becomes even more forward biased resulting in a larger current flow. The effect of this results in a negative resistance at the Emitter terminal.

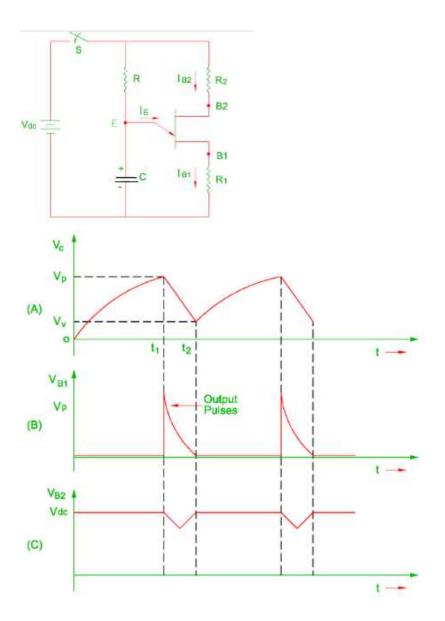

### **UJT Firing Circuit**

It is the most common method of triggering the SCR. The prolonged pulses at the gate using R and RC triggering methods cause more power dissipation at the gate. So by using UJT (Uni Junction Transistor) as triggering device the power loss is limited as it produce a train of pulses. The RC network is connected to the emitter terminal of the UJT which forms the timing circuit. The capacitor is fixed while the resistance is variable and hence the charging rate of the capacitor depends on the variable resistance means that the controlling of the RC time constant.

The UJT is often used in the timing and triggering circuits. Figure A shows the circuit diagram for the UJT relaxation oscillator. When the switch S is kept closed, the capacitor C is charged through resistance R towards voltage VDC. The voltage across capacitor in a given time depends upon circuit time constant RC.

When the voltage across capacitor becomes equal to peak point voltage, the emitter diode is forward biased and UJT conducts. As soon as the UJT starts to conduct, the capacitor discharges through inter base resistance RB1 and the resistance R1. The discharging time constant of the capacitor is very small as compared to charging time constant. The discharging time constant of the capacitor is very small as

compared to charging time constant. When the voltage across capacitor becomes less than the valley point voltage during discharging of the capacitor, the UJT comes in to non-conducting state. (It means that the UJT remains in conducting state until the emitter current drops below valley current).

The capacitor charging and discharging waveform is shown in the Figure A in which time t1 denotes for charging time and time t2 denotes for discharging time of the capacitor.

As the discharging time of the capacitor is very small as compared to charging time, the time required to complete one cycle is considered only for charging time of the capacitor.

```

T = RC \ Loge \ (\ Vdc \ / \ (Vdc - Vp \ ))

As \ Vp = \eta Vdc + VD

Where \ Vp = Peak \ point \ voltage

\eta = Intrinsic \ stand \ off \ ratio

VD = Threshold \ voltage \ of \ the \ diode

T = RC \ Loge \ (\ Vdc \ / \ (Vdc - \eta Vdc - VD \ ))

As \ VD \ is \ small, \ it \ is \ neglected.

T = RC \ Loge \ (\ 1 \ / \ (1 - \eta \ ))

```

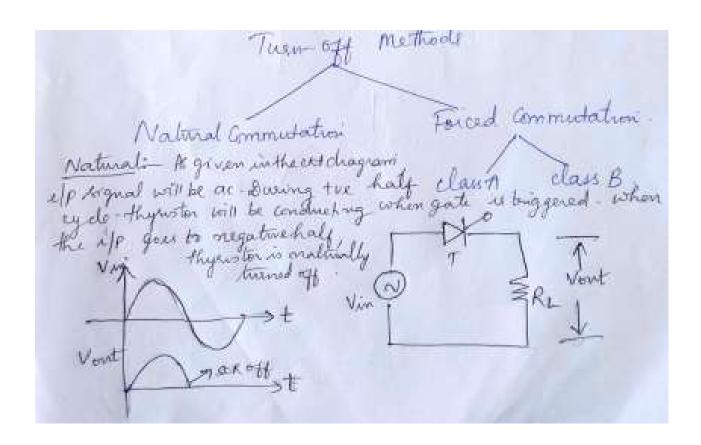

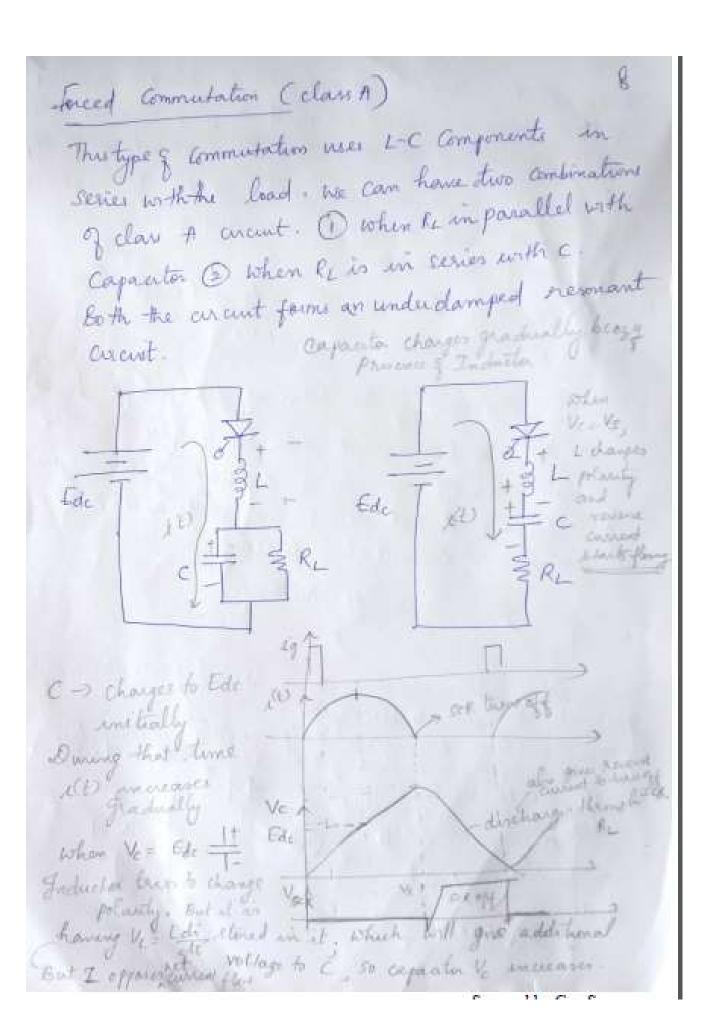

7. What is commutation? What are the different types of Commutation? Explain class A commutation in detail.

The process of turning of SCR is called commutation.

tohen an underdamped resonant curent us reited by a de source, the current will automatically beams sero after some time. The thyrister when ON, caesus only the changing current of Capacitor C, and will soon reduce to a value lesser than the holding current of the ER. This will switch of the thyrister (SCR). The time for switching off the alexace is determined by the resonant frequency which in two depends upon the Land C Components and the total load renstance

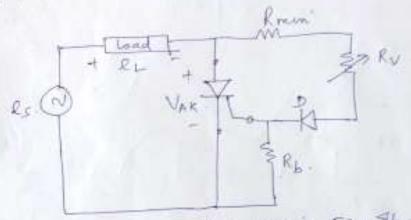

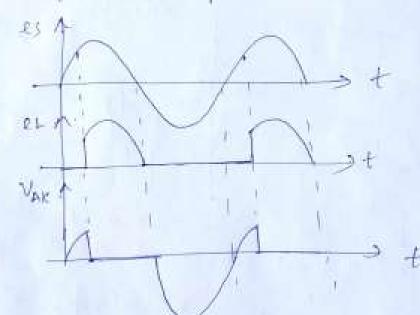

8. With a neat circuit diagram, explain the working of a Resistance Firing circuit. Determine the trigger angle  $\alpha$  for the following specifications:- Ig(min) = 0.1mA, Vg(min) = 0.5 V. The diode is silicon and the peak amplitude of the input is 24 volts. Rv = 100k $\Omega$ , Rmin = 10 k $\Omega$ .

#### **Numerical Part:**

Solution: The first step is to determine the instantaneous value of  $e_s$  at which triggering will occur. At the SCR trigger point,  $V_{g(min)} = 0.5 \text{V}$  and  $I_{g(min)} = 0.1 \text{ mA}$ . Using KVL around the gate circuit, we have

$$e_s = I_g (R_V + R_{\min}) + V_D + V_g$$

At the trigger point,

$e_{s(trigger)} = 0.1 \text{ mA } (110 \text{ k}\Omega) + 0.7\text{V} + 0.5\text{V} = 12.2 \text{ V}.$

Since  $e_s$  is a sine-wave, it obeys the expression

$$e_s = E_{\text{max}}$$

.  $\sin \omega t = E_{\text{max}}$ .  $\sin(2\pi f t)$

where  $2\pi ft$  is the phase angle at any instant of time. For our purposes, this angle is  $\alpha$ . Thus,  $E_{\text{max}} = 24 \text{ V}$ ,

$$e_s = 24 \sin \alpha$$

.  $\therefore 12.2 = 24 \sin \alpha$ .

$$\sin \alpha = \frac{12.2}{24} \qquad \therefore \quad \alpha = 30.6^{\circ}.$$

Resistance fixing circuit — The circuit in the figure shows a simple method of for Varying the brigger angle and there by the power to the lead. Includ of using a gate pulse to trigger the sch, gate current is supplied by an ac voltage source, is, through Rowing Ry and diode D.

(1) As as goes pontine, SCR is FB. It will mot conduct with gate current exceeds Ig min to brigger ser.

(ii) es ferward brases D, allowing gate current to start flowing

(iii) When In reacher, I gimen required to trigger It.

3CR will then ON and EL will be equal to ls

(N) SCR remains ON tell the tre half cycle is over and the when is goes to zero, load current of also reduces. When the loadcurrent goes below holding current, SCR turns off.

(V) SCR Remains in the off state for the whole -ve half cycle and will turn on only when Ignin briggers SER again.

(vi) The purpose of diode as to prevent the gate-cathod neverse bean from exceeding peak severy voltage during -ve half cycle of Rs.

(Vii) The sequence is repeated.

If RV is increased, then gate current will reach its longgar value Ignin for a greater value of Es, making the SCR to twen off at a later stage The the firing angle & will increase

Roman is sequered to to ensure that the peak gode current of the thyrister Igm is not exceeded

Rmin Z Emax Igm

Rb is a stabulising nesister to so that the maximum voltage doop acress it should not exceed max perible gate voltage Vymax.

Rb < (Rv + Rrain) Vymax

Finax - Vymax

The thyristor will brigger when the anstantameous anode voltage ls is

Es = Igmen (Rv + Rrain) + Vd + Vymin

- event is the simplest and most economical will vary from scr to scr and is temp dependent on Igmin which will vary from scr to scr and is temp dependent of a can be varied from 0 to 90° only.

- ls is max at its 90° point