(06 Marks)

Note: Answer any FIVE full questions, choosing ONE full question from each module.

Semester B.E. Degree Examination, June/July 2023

# Module-1

- Explain typical design flow for designing VLSI IC circuits with a neat flow chart. (10 Marks) 1

- Explain top-down design methodology and bottom-up design methodology. (06 Marks) (04 Marks)

- Explain trends in HDL's.

- Explain design hierarchy by taking 4-bit ripple carry counter. (08 Marks)

- Define the following terms with examples

- Module

- ii) Instances

- (06 Marks) iii) Instance name.

- Explain the different levels of abstraction used for programming in verilog.

## Module-2

- With a neat block diagram, explain the components of verilog module (08 Marks) 3

- Explain \$display, \$monitor, \$finish and \$stop system tasks with examples. (08 Marks) (04 Marks)

- How to write comments in verilog HDL, explain with examples.

- Explain the following data types of with an examples:

- i) Nets

- ii) Registers

- iii) Integers

- (08 Marks) iv) Parameters. (08 Marks)

- Write verilog description of SR latch. Also write stimulus code. With an example, explain hierarchical names.

- (04 Marks)

### Module-3

- What are Rise, Fall and Turn-off delays? How they are specified in verilog. (06 Marks) 5

- Write a verilog dataflow level of abstraction for 4 to 1 multiplexer using conditional (08 Marks) operator. Also write stimulus code.

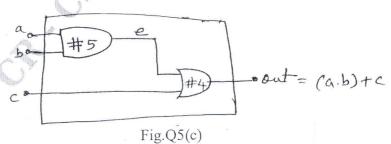

- Design a gate level module according to the logic diagram given Fig.Q5(c). Write stimulus code delay.

1 of 2

(06 Marks)

2. Any revealing of identification, appeal to evaluator and /or equations written eg, 42+8 = 50, will be treated as malpractice Important Note: 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

(10 Marks)

OR

a. Develop a gate-level verilog code for 4-bit ripple carry adder from 1-bit full adder. What is 6 the output if A = 1010, B = 1100 and  $c_{in} = 0$  at t = 0. (10 Marks) b. What would be the output of the following: a = 4'b0111, b = 4'b1001&b i) ii) a < < 2iii)  $\{a,b\}$ iv) {2{b}} a b V) vi) ab vii) a & b (08 Marks) viii) ~ a. c. Declare following variables in Verilog, i) A 8-bit vector called a - in (02 Marks) ii) An integer called count. Module-4 Discuss sequential and parallel blocks with examples. (08 Marks) Write a verilog behavioural description of 8:1 multiplexer using case statement. (06 Marks) Illustrate the use while loop and repeat loop with examples. (06 Marks) Explain blocking and non-blocking assignment statements with relevant examples. (08 Marks) 8 Write verilog behavioral description of 4-bit binary counter. (06 Marks) (06 Marks) Write the verilog behavioral description of Dflip – flap. Module-5 Define the term logic synthesis. With a neat flow-chart explain computer - Aided logic 9 (10 Marks) synthesis process. b. What will the following statement translate to when run on a logic synthesis tool, assign y = (a&b) | (c&b) where y, a, b, c and d are 3 - bit vectors ii) if(s) out = i1; else CMRIT LIBRARY (10 Marks) out = i0BANGALORE - 560 037 With neat flow diagram explain synthesis design flow. (10 Marks) 10 a. Write a notes on:

i) Assign and deassign

ii) Overriding parameters.