| U   | SN                                                                                           |                                                                                                              |               |           | CEEE STAN ACCREDITE | TE OF TECHNOLOG | ARIT Y, BENGALURU. DE BY NAAC |

|-----|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------|-----------|---------------------|-----------------|-------------------------------|

|     |                                                                                              | Internal Assessment Test 1–                                                                                  | July 2023     |           |                     |                 |                               |

| Sub | <b>)</b> :                                                                                   | Microcontroller and Embedded Systems                                                                         | Sub Code:     | 21CS43    | Branch              | ISE             |                               |

| Da  | te:                                                                                          | 06/07/2023 Duration: 90 min's Max Marks: 50                                                                  | Sem/Sec:      | IV / A, B | and C               | OF              | BE                            |

|     |                                                                                              | Answer any FIVE FULL Questions                                                                               |               |           | MARKS               | CO              | RBT                           |

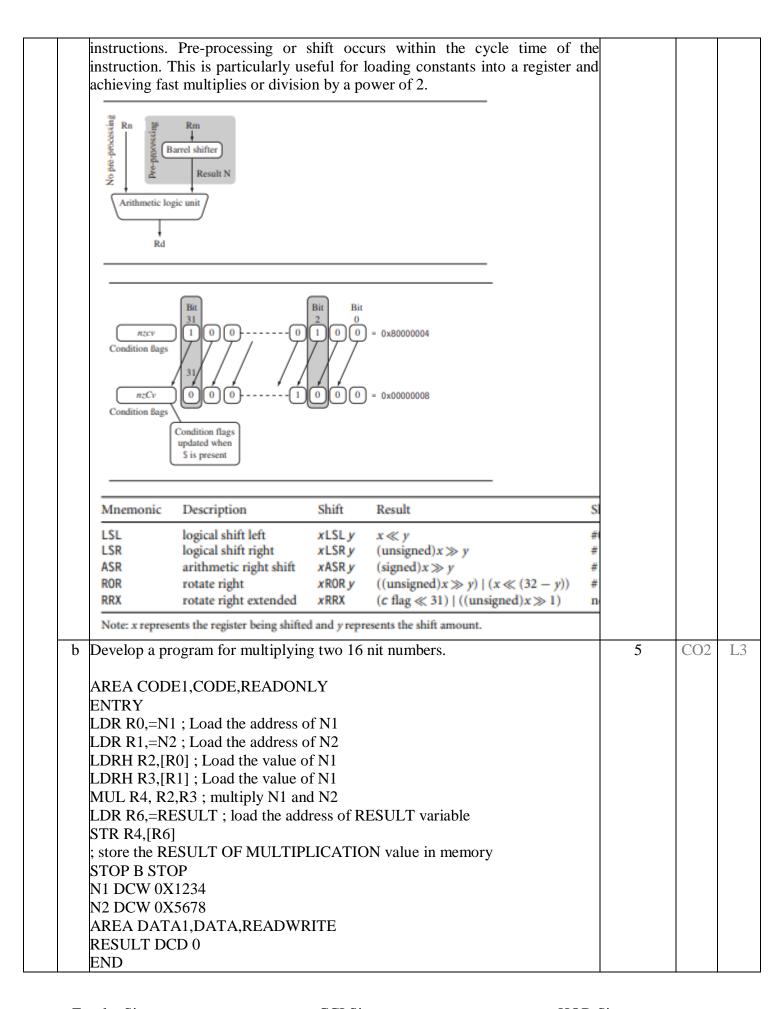

| 1   |                                                                                              | Differentiate between i) RISC and CISC Processors ii) Microprocessor.                                        | Microcontroll | er and    | 10                  | CO1             | L2                            |

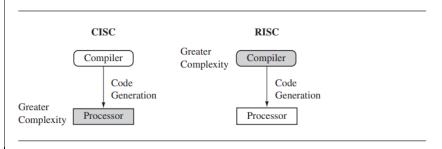

| 2   | Explain the architecture of a typical embedded device based on ARM core with a neat diagram. |                                                                                                              |               |           | 10                  | CO1             | L2                            |

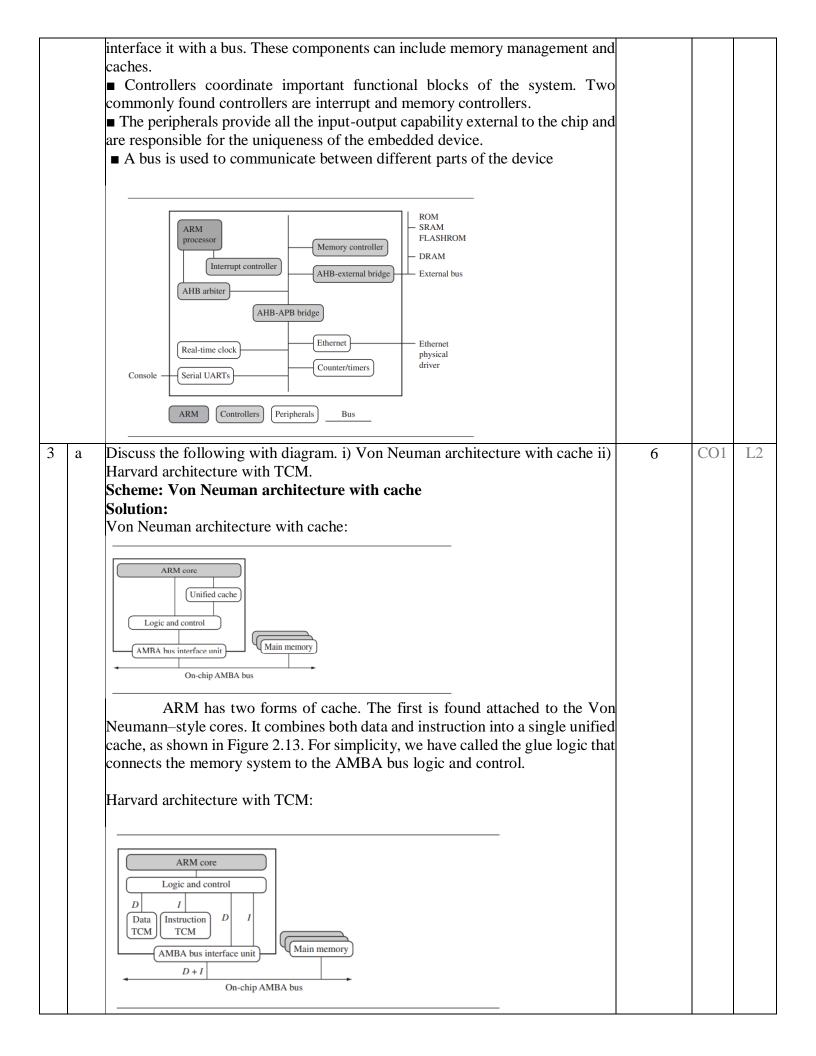

| 3   | a                                                                                            | Discuss the following with diagram. i) Von Neuman architecture with cache ii) Harvard architecture with TCM. |               |           | 6                   | CO1             | L2                            |

|     | b                                                                                            | Discuss the ARM design philosophy                                                                            |               |           |                     | CO1             | L2                            |

| 4   |                                                                                              | With example, explain the following ARM instructions i) MOV ii) LDR iii) ADD iv) BNE v) STR                  |               |           | 10                  | CO2             | L2                            |

| 5   | a Develop an ALP to find factorial of a given number.                                        |                                                                                                              |               |           | 5                   | CO2             | L3                            |

|     | b                                                                                            | Explain the AMBA Bus architecture in detail.                                                                 |               |           | 5                   | CO2             | L2                            |

| 6   | a                                                                                            | Explain the barrel shifter operation in ARM processor, with a neat diagram.                                  |               | 5         | CO1                 | L2              |                               |

|     | b                                                                                            | Develop a program for multiplying two 16 nit numbers.                                                        |               |           | 5                   | CO2             | L3                            |

Faculty Signature CCI Signature

HOD Signature

| US  | SN         |                                                                                | * can institute of technology, installur<br>accretated with a signal with a |     |                      |  |

|-----|------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------|--|

|     |            | Internal Assessment Test 1– July 2023                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |                      |  |

| Sub | <b>)</b> : | Microcontroller and Embedded Systems Sub Code: 21CS43                          | Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ISE |                      |  |

| Da  | te:        | 06/07/2023 Duration: 90 min's Max Marks: 50 Sem/Sec: IV / A, B                 | and C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OF  | E<br>RBT<br>L2<br>L2 |  |

|     |            | Answer any FIVE FULL Questions                                                 | MARKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CO  | RBT                  |  |

| 1   |            | Differentiate between i) RISC and CISC Processors ii) Microcontroller and      | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CO1 | L2                   |  |

|     | 1          | microprocessor.                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |                      |  |

| 2   |            | Explain the architecture of a typical embedded device based on ARM core with a | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CO1 | L2                   |  |

|     | ]          | neat diagram.                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |                      |  |

| 3   | a          | Discuss the following with diagram. i) Von Neuman architecture with cache ii)  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CO1 | L2                   |  |

|     | ]          | Harvard architecture with TCM.                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |                      |  |

|     | b          | Discuss the ARM design philosophy                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CO1 | L2                   |  |

| 4   |            | With example, explain the following ARM instructions i) MOV ii) LDR iii)       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CO2 | L2                   |  |

|     |            | ADD iv) BNE v) STR                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |                      |  |

| 5   | a          | Develop an ALP to find factorial of a given number.                            | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CO2 | L3                   |  |

|     | b          | Explain the AMBA Bus architecture in detail.                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CO2 | L2                   |  |

| 6   | a          | Explain the barrel shifter operation in ARM processor, with a neat diagram.    | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CO1 | L2                   |  |

|     | b          | Develop a program for multiplying two 16 nit numbers.                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CO2 | L3                   |  |

Faculty Signature CCI Signature HOD Signature

| USN  |                                                                                                                                                                       |                                      |                                  |                 | CELEBRONA CELEBRA CELE | TE OF TECHNOLOG | ARIT |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|

|      | Internal Asses                                                                                                                                                        | ssment Test 1–                       | July 2023                        |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |

| ub:  | Microcontroller and Embedded Systems                                                                                                                                  |                                      | Sub Code:                        | 21CS43          | Branch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ISE             |      |

| ate: | 06/07/2023 Duration: 90 min's Max                                                                                                                                     | Marks: 50                            | Sem/Sec:                         | IV / A, B       | and C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OF              | BE   |

|      | Answer any FIVE FULI                                                                                                                                                  | L Questions                          | 1                                | •               | MARKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CO              | RB'  |

|      | Differentiate between i) RISC and CISC microprocessor.  Scheme: - (i) Difference between RISC & Ci (ii) Difference between Microcon Solution: - (i) Any 5 differences | ISC Processor –                      | - 5 Marks                        |                 | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CO1             | L    |

|      | RISC                                                                                                                                                                  |                                      | CISC                             |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |

|      | It is a Reduced Instruction Set Computer.                                                                                                                             | It is a Complex In                   | struction Set Com                | puter.          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |

|      | It emphasizes on software to optimize the instruction set.                                                                                                            | It emphasizes instruction set.       | on hardware t                    | o optimize      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |

|      | It is a hard wired unit of programming in the RISC Processor.                                                                                                         | Microprogrammi                       | ng unit in CISC Pro              | ocessor.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |

|      | It requires multiple register sets to store the instruction.                                                                                                          | It requires a sinstruction.          | single register s                | et to store     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |

|      | RISC has simple decoding of instruction.                                                                                                                              | CISC has complex                     | decoding of instr                | ruction.        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |

|      | Uses of the pipeline are simple in RISC.                                                                                                                              | Uses of the pipeli                   | ine are difficult in             | CISC.           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |

|      | It uses a limited number of instruction that requires less time to execute the instructions.                                                                          | _                                    | umber of instruction             | -               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |      |